# **CMS**

# The TriDAS Project Technical Design Report, Volume 1: The Trigger Systems

Also available at http://cmsdoc.cern.ch/cms/TDR/TRIGGER-public/trigger.html

| CMS TriDAS Project                                                         |                                                                           |                                                  |  |  |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------|--|--|

| Chairperson Institution Board: Paris Sphicas, MIT-CERN, paris.sphicas@cern |                                                                           |                                                  |  |  |

| Project Manager                                                            | Trigger Project Manger                                                    | Resource Manager                                 |  |  |

| Sergio Cittolin<br>CERN<br>sergio.cittolin@cern.ch                         | Wesley H. Smith<br>University of Wisconsin<br>wsmith@hep.physics.wisc.edu | Joao Varela<br>LIP/Lisboa<br>joao.varela@cern.ch |  |  |

| CMS Spokesperson           | CMS Technical Coordinator |

|----------------------------|---------------------------|

| Michel Della Negra         | Alain Herve               |

| CERN                       | CERN                      |

| Michel.Della.Negra@cern.ch | Alain.Herve@cern.ch       |

| CMS Trigger T  | DR Editorial Board |

|----------------|--------------------|

| W.H.           | Smith, Chair       |

| Ph. Busson     | S. Dasu            |

| J. Hauser      | G. Heath           |

| J. Krolikowski | J. Varela          |

| A. Taurok      | G. Wrochna         |

| P. Zotto       |                    |

| CMS Trigger TDR Chapter Editors |                                                                                                              |  |  |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| 1.                              | W. H. Smith                                                                                                  |  |  |  |

| 2.                              | G.Wrochna                                                                                                    |  |  |  |

| 3.                              | J. Varela, S. Dasu                                                                                           |  |  |  |

| 4.                              | Ph. Busson, J. Varela, D. Baden                                                                              |  |  |  |

| 5.                              | S. Dasu                                                                                                      |  |  |  |

| 6.                              | G. Heath                                                                                                     |  |  |  |

| 7.                              | J. Varela                                                                                                    |  |  |  |

| 8.                              | G. Wrochna                                                                                                   |  |  |  |

| 9.                              | P. Zotto, A. Montanari, R.Martinelli, G. M. Dallavalle, F. Odorici                                           |  |  |  |

| 10.                             | J. Erö, M. Fierro, M. Brugger, G. M. Dallavalle                                                              |  |  |  |

| 11.                             | J. Hauser, P.Padley                                                                                          |  |  |  |

| 12.                             | D. Acosta                                                                                                    |  |  |  |

| 13.                             | J.Krolikowski, G. Wrochna, M.Konecki, M. Kudla, A.Ranieri, E.Pietarinen, K. Banzuzi, K. Pozniak, P. Zalewski |  |  |  |

| 14.                             | CE. Wulz, A.Taurok, H. Sakulin                                                                               |  |  |  |

| 15.                             | CE. Wulz, A. Taurok                                                                                          |  |  |  |

| 16.                             | J. Varela                                                                                                    |  |  |  |

| 17.                             | J. Varela                                                                                                    |  |  |  |

| 18.                             | W. H. Smith                                                                                                  |  |  |  |

| 19.                             | F. Szoncso                                                                                                   |  |  |  |

| 20.                             | W. H.Smith, J. Varela                                                                                        |  |  |  |

i

CMS Trigger TDR CMS Collaboration

# **CMS Collaboration**

# Yerevan Physics Institute, Yerevan, ARMENIA

G.L. Bayatian, N. Grigorian, V.G. Khachatrian, A. Margarian, A.M. Sirunyan, S. Stepanian

# Institut für Hochenergiephysik der ÖAW, Wien, AUSTRIA

W. Adam, M. Brugger, J. Erö, M. Fierro, M. Friedl, R. Fruehwirth, J. Hrubec, A. Jeitler, M. Krammer, M. Pernicka, P. Porth, H. Rohringer, L. Rurua<sup>1</sup>, A. Taurok, G. Walzel, R. Wedenig, C.-E. Wulz

# Research Institute for Nuclear Problems, Minsk, BELARUS

V.G. Baryshevsky, A. Fedorov, N. Gorodichenine, M. Korzhik, O. Missevitch<sup>2</sup>, V. Panov, R. Zuyeuski

# National Centre for Particle and High Energy Physics, Minsk, BELARUS

I. Akushevich, N. Chekhlova, V. Chekhovsky, O. Dvornikov, I. Emeliantchik, A. Khomitch, V. Kolpaschikov, M. Kryvamaz, V. Kuvshinov, A. Litomin, V. Mossolov, A. Panfilenko, S. Reutovich, N. Shumeiko, A. Solin, R. Stefanovitch, V. Strazhev, S. Vetokhin, Y. Yurenya, V. Zalessky

# Research Institute of Applied Physical Problems, Minsk, BELARUS

F. Ermalitsky, P. Kuchinsky, V. Lomako

# Byelorussian State University, Minsk, BELARUS

V. Petrov, V. Prosolovich

# Vrije Universiteit Brussel, Brussels, BELGIUM

O. Devroede, R. Goorens, J. Lemonne, S. Tavernier, F. Udo<sup>3</sup>, W. Van Doninck<sup>2</sup>, L. Van Lancker

# Université Libre de Bruxelles, Brussels, BELGIUM

D. Bertrand, G. De Lentdecker, J. Stefanescu, C. Vander Velde, P. Vanlaer

# Université Catholique de Louvain, Louvain-la-Neuve, BELGIUM

D. Favart, J. Govaerts, G. Gregoire, V. Lemaitre, A. Ninane, K. Piotrzkowski, O. Van der Aa

# Université de Mons-Hainaut, Mons, BELGIUM

I. Boulogne, E. Daubie, P. Herquet

# Universitaire Instelling Antwerpen, Wilrijk, BELGIUM

W. Beaumont, T. Beckers, E. De Langhe, F. Moortgat, F. Verbeure, V. Zhukov<sup>4</sup>

# Institute for Nuclear Research and Nuclear Energy, Sofia, BULGARIA

K. Abadjiev, T. Anguelov, I. Atanassov, J. Damgov, L. Dimitrov, V. Genchev, G. Georgiev, P. Iaydjiev, B. Kounov, L. Penchev, P. Raykov<sup>5</sup>, G. Sultanov, I. Vankov, P. Vankov

# University of Sofia, Sofia, BULGARIA

N. Darmenov, A. Gritskov, A. Jordanov, L. Litov, M. Mateev, P. Petev, V. Spassov, M. Tchijov, R. Tsenov, G.V.  $Velev^6$

# Institute of High Energy Physics, Beijing, CHINA PR

J.G. Bian, C. Chen, G.M. Chen, Y.N. Guo, J.T. He, C.H. Jiang, B.N. Jin, Z.J. Ke, J. Li, W.G. Li, X.N. Li, J.F. Qiu, B.W. Shen, X.Y. Shen, H.Y. Sheng, Y.Y. Wang, R.S. Xu, M. Yang, B.Y. Zhang, J.W. Zhang, S.Q. Zhang, W.R. Zhao, Z. Zhao, J.P. Zheng, G.Y. Zhu, Y.S. Zhu

CMS Collaboration CMS Trigger TDR

# Peking University, Beijing, CHINA PR

Y. Ban, J. Cai, J.E. Chen, H.T. Liu, S.Q. Liu, B.Q. Lou, S.J. Qian, Y.L. Ye

# University for Science and Technology of China, Hefei, Anhui, CHINA PR

Q. An, Z. Bian, H. Chen, Z.F. Gong, C. Li, C.S. Shi, L.Z. Sun, X.L. Wang, Z.M. Wang, J. Wu, S.W. Ye, Z.P. Zhang

# Shanghai Institute of Ceramics, Shanghai, CHINA PR (Associated Institute)

Q. Deng, P.J. Li, D.Z. Shen, Z.L. Xue, H. Yuan

# National Central University, Chung-Li, CHINA (TAIWAN)

Y.H. Chang, A.E. Chen, A. Go, W. Lin

# National Taiwan University, Taipei, CHINA (TAIWAN)

P. Chang, G.W.S. Hou, K. Ueno

# **Technical University of Split, Split, CROATIA**

N. Godinovic, M. Milin<sup>7</sup>, I. Puljak, I. Soric, M. Stipcevic<sup>7</sup>, J. Tudoric-Ghemo

# University of Split, Split, CROATIA

Z. Antunovic, M. Dzelalija, K. Marasovic

# University of Cyprus, Nicosia, CYPRUS

A. Hasan<sup>5</sup>, P.A. Razis, A. Vorvolakos

# National Institute of Chemical Physics and Biophysics, Tallinn, ESTONIA

A. Hall, E. Lippmaa, J. Lippmaa, M. Raidal, J. Subbi

# Laboratory of Advanced Energy Systems, Helsinki University of Technology, Espoo, FINLAND

P.A. Aarnio

# Helsinki Institute of Physics, Helsinki, FINLAND

K. Banzuzi, M.A. Heikkinen, J.V. Heinonen, A. Honkanen, V.J. Karimäki, H.M. Katajisto, R. Kinnunen, K. Lassila-Perini, V. Lefébure<sup>2</sup>, E. Pietarinen, E. Tuominen, J. Tuominiemi, D. Ungaro, T.P. Vanhala, C. Williams

# Department of Physics, University of Helsinki, Helsinki, FINLAND

S. Lehti, T. Linden

# Department of Physics, University of Jyväskylä, Jyväskylä, FINLAND

J. Aysto, R. Julin, V. Ruuskanen

# Dept. of Physics & Microelectronics Instrumentation Lab., University of Oulu, Oulu, FINLAND

S. Kallijarvi, A.J. Keranen, L. Palmu, K. Remes, E. Suhonen, T. Tuuva

# Digital and Computer systems Laboratory, Tampere University of Technology, Tampere, FINLAND

J. Niittylahti, O. Vainio

# Laboratoire d'Annecy-le-Vieux de Physique des Particules, IN2P3-CNRS, Annecy-le-Vieux, FRANCE

Y.W. Baek, D. Boget, J. Ditta, G. Drobychev, J.P. Guillaud, M. Maire, J.P. Mendiburu, P. Nedelec, J.P. Peigneux, M. Schneegans<sup>2</sup>, D. Sillou

# DSM/DAPNIA, CEA/Saclay, Gif-sur-Yvette, FRANCE

M. Anfreville, P. Bonamy, C. Bouchand, R. Chipaux, M. Dejardin, D. Denegri, F.X. Gentit, A. Givernaud, F. Kircher, Y. Lemoigne, E. Locci, J.P. Lottin, M.C. Nguyen, J.P. Pansart, A. Payn, J. Rander, J.M. Reymond, F. Rondeaux, A. Rosowsky, P. Roth, P. Verrecchia

# Laboratoire de Physique Nucléaire des Hautes Energies, Ecole Polytechnique, IN2P3-CNRS, Palaiseau, FRANCE

J. Badier, M. Bercher, J. Bourotte<sup>2</sup>, P. Busson, D. Chamont, C. Charlot, L. Dobrzynski, J. Gilly, M. Haguenauer, A. Karar, G.B. Kim, L. Kluberg, D. Lecouturier, P. Matricon, G. Milleret, P. Mine, R. Morano, P. Paganini, P. Poilleux, T. Romanteau

# Institut de Recherches Subatomiques, IN2P3-CNRS - ULP, LEPSI Strasbourg, UHA Mulhouse, Strasbourg, FRANCE

A. Albert<sup>8</sup>, J.D. Berst<sup>9</sup>, R. Blaes<sup>8</sup>, J.M. Brom, F. Charles<sup>8</sup>, J. Coffin, F. Didierjean, F. Drouhin<sup>8</sup>, J.P. Ernenwein<sup>8</sup>, J.C. Fontaine<sup>8</sup>, W. Geist, U. Goerlach, J.M. Helleboid, D. Huss<sup>8</sup>, C. Illinger<sup>9</sup>. P. Juillot, A. Lounis, C. Maazouzi, S. Moreau, Y. Riahi, I. Ripp-Baudot, T. Todorov<sup>2</sup>, D. Vintache, A. Zghiche

# Institut de Physique Nucléaire de Lyon, IN2P3-CNRS, Univ. Lyon I, Villeurbanne, FRANCE

M. Ageron, M. Bedjidian, E. Chabanat, C. Combaret, D. Contardo, P. Depasse, O. Drapier, M. Dupanloup, H. El Mamouni, J. Fay, S. Gascon-Shotkin, N. Giraud, C. Girerd, M. Goyot, R. Haroutounian, B. Ille, P. Lebrun, M. Lethuillier, J.P. Martin, H. Mathez, L. Mirabito, S. Muanza, S. Perries, P. Sahuc, G. Smadja, S. Tissot, J.P. Walder, F. Zach

# High Energy Physics Institute, Tbilisi State University, Tbilisi, GEORGIA

N. Amaglobeli, Y. Bagaturia, L. Glonti, V. Kartvelishvili, R. Kvatadze, D. Mzavia, T. Sakhelashvili<sup>10</sup>, R. Shanidze, Z. Tsamalaidze

# Institute of Physics Academy of Science, Tbilisi, GEORGIA

N. Djaoshvili, I. Iashvili<sup>11</sup>, A. Kharchilava, N. Roinishvili, V. Roinishvili

# RWTH, I. Physikalisches Institut, Aachen, GERMANY

C. Berger, W. Braunschweig, J. Breibach, W.H. Gu, A. Heister, W. Karpinski, T. Kirn, S. Konig, C. Kukulies, A. Ostaptchouk, D. Pandoulas, G. Pierschel, F. Raupach, S. Schael, D. Schmitz, A. Schultz Von Dratzig, R. Siedling, W. Wallraff, B. Wittmer

# RWTH, III. Physikalisches Institut A, Aachen, GERMANY

K. Banicz, S. Bechstein, A. Bohm, K. Bosseler, H. Faissner, H. Fesefeldt, S. Hermann, A. Ivannikov, D. Rein, H. Reithler, H. Szczesny, M. Tonutti, M. Wegner

# RWTH, III. Physikalisches Institut B, Aachen, GERMANY

M. Axer, F. Beissel, V. Commichau, G. Flüge, K. Hangarter, D. Macke, J. Mnich, A. Nowack, M. Petertill, P. Schmitz, R. Schulte, L. Sonnenschein, A. Zander

#### Humboldt-Universität zu Berlin, Berlin, GERMANY

M. Grunewald, T. Hebbeker, K. Hoepfner, A. Rosca

# Institut für Experimentelle Kernphysik, Karlsruhe, GERMANY

V. Bartsch, P. Blum, W. De Boer, A. Dierlamm, G. Dirkes, V. Drollinger, M. Erdmann, M. Feindt, E. Grigoriev, F. Hartmann, F. Hauler, A. Heiss, T. Muller, F. Roederer, H.J. Simonis, A. Skiba, A. Theel, W.H. Thummel, T. Weiler, S. Weseler

#### University of Athens, Athens, GREECE

L. Resvanis

# Institute of Nuclear Physics "Demokritos", Attiki, GREECE

P. Adzic, M. Barone, I. Bozovic-Jelisavcic, G. Fanourakis, T. Geralis, S. Harissopulos, P. Kokkinias, A. Kyriakis, D. Loukas, A. Markou, C. Markou, N. Mastroyiannopoulos, J. Mousa, I. Siotis, M. Spyropoulou-Stassinaki, A. Staveris Polykalas, A. Tsirigotis, S. Tzamarias. A. Vayaki, K. Zachariadou, M. Zupan

# University of Ioánnina, Ioánnina, GREECE

A. Asimidis, I. Evangelou, P. Kokkas, N. Manthos, O. Mitropoulos, K. Prouskas, F.A. Triantis, N. Tzoulis

# KFKI Research Institute for Particle and Nuclear Physics, Budapest, HUNGARY

Z. Bagoly, G. Bencze<sup>2</sup>, A. Csilling, C. Hajdu, P. Hidas, D. Horvath<sup>12</sup>, G. Odor, A. Ster, L. Urban, G. Vesztergombi, P. Zalan, M. Zsenei

# Institute of Nuclear Research ATOMKI, Debrecen, HUNGARY

G. Dajko, A. Fenyvesi, J. Molnar, J. Palinkas, D. Sohler, Z.L. Trocsanyi, J. Vamosi, J. Vegh

# **Kossuth Lajos University, Debrecen, HUNGARY**

L. Baksay, T. Bondar, S. Juhasz, G. Marian, S. Nagy, P. Raics, J. Szabo, Z. Szabo, S. Szegedi, Z. Szillasi, T. Sztaricskai, P. Tarjan, G. Zilizi

# Panjab University, Chandigarh, INDIA

S.B. Bala, V. Bhatnagar, M. Kaur, J.M. Kohli, J. Singh

# Bhabha Atomic Research Centre, Mumbai, INDIA

S. Borkar<sup>2</sup>, V. Chandratre, R.K. Chaudhury, M.Y. Dixit, M. Ghodgaonkar, B. John, S.K. Kataria, A.K. Mohanty, A. Topkar

#### Tata Institute of Fundamental Research - EHEP, Mumbai, INDIA

T. Aziz, Sunanda Banerjee, S. Chendvankar, P.V. Deshpande, S.N. Ganguli, A. Gurtu, S. Katta, M. Maity, K. Mazumdar, M.R. Patil, S.C. Tonwar

#### Tata Institute of Fundamental Research - HECR, Mumbai, INDIA

B.S. Acharya, Sudeshna Banerjee, S. Bheesette, S. Dugad, S.D. Kalmani, M.R. Krishnaswamy, V.R. Lakkireddi, N.K. Mondal, N. Panyam, N. Vemuri, P. Verma

# University of Delhi South Campus, New Delhi, INDIA

A. Bhardwaj, R.K. Shivpuri, V.K. Verma

# Università di Bari, Politecnico di Bari e Sezione dell' INFN, Bari, ITALY

M. Abbrescia, A. Colaleo, D. Creanza, M. De Palma, L. Fiore, G. Iaselli, F. Loddo, G. Maggi, B. Marangelli, M. Menegotto, S. My, S. Natali, S. Nuzzo, G. Pugliese, V. Radicci, A. Ranieri, F. Romano, F. Ruggieri, G. Selvaggi, L. Silvestris<sup>2</sup>, P. Tempesta, G. Zito

# Università di Bologna e Sezione dell' INFN, Bologna, ITALY

A. Benvenuti, P. Capiluppi, F. Cavallo, M. Cuffiani, I. D'Antone, G.M. Dallavalle, F. Fabbri, A. Fanfani, G. Giacomelli, P. Giacomelli<sup>13</sup>, C. Grandi, M. Guerzoni, S. Marcellini, P. Mazzanti, A. Montanari, C. Montanari, F. Navarria, F. Odorici, A. Perrotta, A. Rossi, T. Rovelli, G. Siroli, R. Travaglini

CMS Trigger TDR CMS Collaboration

CVIS CONDUCTATION

# Università di Catania e Sezione dell' INFN, Catania, ITALY

S. Albergo, V. Bellini, P. Castorina, S. Cavalieri, M. Chiorboli, S. Costa, L. Lo Monaco, R. Potenza, V. Russo, A. Tricomi, C. Tuve

#### Università di Firenze e Sezione dell' INFN, Firenze, ITALY

L. Bellucci, U. Biggeri, E. Borchi, M. Bruzzi, A. Buffini, S. Busoni, G. Castellini, C. Civinini, R. D'Alessandro, E. Focardi, G. Landi, M. Lenzi, M. Meschini, C. Minelli, G. Parrini, M. Pieri, S. Pirollo, S. Sciortino

# Università di Genova e Sezione dell' INFN, Genova, ITALY

M. Bozzo, P. Fabbricatore, S. Farinon, R. Musenich, C. Priano

# Laboratori Nazionali di Legnaro e Sezione dell' INFN, Legnaro, ITALY (Associated Institute)

L. Berti, M. Biasotto, U. Gastaldi, M. Gulmini, G. Maron, N. Toniolo

# Università di Padova e Sezione dell' INFN, Padova, ITALY

P. Azzi, N. Bacchetta, M. Bellato, M. Benettoni, D. Bisello, A. Candelori, A. Castro, P. Checchia, E. Conti, M. De Giorgi, A. De Min, U. Dosselli, C. Fanin, F. Gasparini, U. Gasparini, F. Gonella, A. Kaminski, S. Lacaprara, I. Lippi, M. Loreti, A.T. Meneguzzo, M. Michelotto, F. Montecassiano, A. Neviani, A. Paccagnella, S. Paoletti, M. Passaseo, M. Pegoraro, P. Ronchese, I. Stavitski, E. Torassa, L. Ventura, S. Ventura, M. Verlato, P. Zotto<sup>14</sup>, G. Zumerle

# Università di Pavia e Sezione dell' INFN, Pavia, ITALY

S. Altieri, G. Belli, G. Bruno, R. Guida, M. Merlo, S.P. Ratti, C. Riccardi, P. Torre, P. Vitulo

# Università di Perugia e Sezione dell' INFN, Perugia, ITALY

M.M. Angarano, E. Babucci, M. Biasini, G.M. Bilei, M.T. Brunetti, F. Ceccotti, B. Checcucci, M. Giorgi, P. Lariccia, G. Mantovani, D. Passeri, P. Placidi, V. Postolache, R. Santinelli, A. Santocchia, A. Scorzoni, L. Servoli, G. Tommasi

#### Università di Pisa e Sezione dell' INFN, Pisa, ITALY

F. Angelini, G. Bagliesi, A. Bardi, A. Basti, R. Bellazzini, J. Bernardini, L. Borrello, F. Bosi, P.L. Braccini, A. Brez, R. Carosi, R. Castaldi, G. Chiarelli, V. Ciulli, M. Dell'Orso, R. Dell'Orso, S. Donati, S. Dutta, L. Foa, S. Galeotti, P. Giannetti, A. Giassi, S. Giusti, G. Iannaccone, L. Latronico, F. Ligabue, N. Lumb, G. Magazzu, M. Mariani, M.M. Massai, A. Messineo, O. Militaru<sup>15</sup>, A. Moggi, F. Morsani, F. Palla, G. Punzi, F. Raffaelli, L. Ristori, G. Sanguinetti, A. Sciaba, G. Segneri, G. Sguazzoni, G. Spandre, M. Spezziga, F. Spinella, A. Starodumov, R. Tenchini, L. Teodorescu<sup>15</sup>, G. Tonelli, A. Venturi, P.G. Verdini, J. Wang, Z. Xie

# Università di Roma I e Sezione dell' INFN, Roma, ITALY

S. Baccaro<sup>16</sup>, L. Barone, A. Bartoloni, M. Castellani, A. Cecilia, I. Dafinei, F. De Notaristefani, M. Diemoz, A. Festinesi<sup>16</sup>, E. Longo<sup>2</sup>, P. Meridiani, M. Montecchi<sup>16</sup>, G. Organtini, M. Puccini<sup>16</sup>, E. Valente, A. Zullo

# Università di Torino e Sezione dell' INFN, Torino, ITALY

N. Amapane, M. Arneodo, F. Bertolino, C. Biino-Palestini, R. Cirio, M. Costa, D. Dattola, F. Daudo, V. Del Duca, L. Demaria, G. Favro, M.I. Ferrero, S. Maselli, V. Monaco, C. Peroni, A. Romero, R. Sacchi, A. Solano, A. Staiano, A. Vitelli

# Cheju National University, Cheju, KOREA

Y.J. Kim

CMS Collaboration CMS Trigger TDR

#### Chungbuk National University, Chongju, KOREA

Y.U. Kim

# Kangwon National University, Chunchon, KOREA

S.K. Nam

# Wonkwang University, Iksan, KOREA

S.Y. Bahk

# Chonnam National University, Kwangju, KOREA

H.I. Jang, J.Y. Kim, T.I. Kim, I.T. Lim

#### Dongshin University, Naju, KOREA

M.Y. Pac

# Seonam University, Namwon, KOREA

S.J. Lee

# Konkuk University, Seoul, KOREA

J.T. Rhee

# Korea University, Seoul, KOREA

S. Ahn, B. Hong, S.J. Hong, Y.J. Kim, K.S. Lee, H.K. Park, S.K. Park, K.S. Sim

# Seoul National University of Education, Seoul, KOREA

D.G. Koo

#### Seoul National University, Seoul, KOREA

B.J. Kim, S.B. Kim, I.H. Park

# Sungkyunkwan University, Suwon, KOREA

B.G. Cheon, Y.I. Choi

#### Kyungpook National University, Taegu, KOREA

W.H. Chung, S.W. Ham, H.M. Jeon, D.H. Kim, G. Kim, W.Y. Kim, S.K. Oh, S. Ro, D.C. Son

# National Centre for Physics, Quaid-I-Azam University, Islamabad, PAKISTAN

Z. Aftab, M.A. Ahmad, J. Alam Jan, N. Bhatti, K. Hasanain, H.R. Hoorani<sup>2</sup>, M.K. Khan, S.M. Khan, A. Niaz, R. Riazuddin, T. Solaija

#### Ghulam Ishaq Khan Institute of Engineering Sciences and Technology, Swabi, PAKISTAN

J. Ahmad, I.U. Awan, N. Iftikhar, M.A. Khan, M.U. Mirza, A. Muhammad, J. Zeb

# Institute of Experimental Physics, Warsaw, POLAND

M. Cwiok, H. Czyrkowski, R. Dabrowski, W. Dominik, M. Kazana, J. Krolikowski, I. Kudla, P. Majewski, M. Pietrusinski, K. Pozniak, P. Zych

# Soltan Institute for Nuclear Studies, Warsaw, POLAND

R. Gokieli<sup>2</sup>, M. Gorski, L. Goscilo, G. Wrochna, P. Zalewski

# Laboratório de Instrumentação e Física Experimental de Particulas, Lisboa, PORTUGAL

C. Almeida<sup>30</sup>, N. Almeida, J. Augusto<sup>30</sup>, T. Barata Monteiro, P. Bordalo<sup>31</sup>, N. Cardoso<sup>30</sup>, S. Da Mota Silva, J. Da Silva, O.P. Dias<sup>30</sup>, J. Gomes, F.M. Goncalves<sup>30</sup>, S. Ramos<sup>31</sup>, M. Santos<sup>30</sup>, J. Semiao<sup>30</sup>, S. Sequeira Lopes Tavares<sup>2</sup>, S. Silva, C. Simoes Azevedo, I. Teixeira<sup>30</sup>, J.P. Teixeira<sup>30</sup>, J. Varela<sup>2, 31</sup>

CMS Trigger TDR **CMS** Collaboration

#### Joint Institute for Nuclear Research, Dubna, RUSSIA

S. Afanasiev, I. Anissimov, D. Bandurin, A. Belkov, S. Chatrchyan, C.V. Cheshkov, A. Chvyrov, A. Dmitriev, V. Elsha, Y. Erchov, M. Finger, M. Finger, I. Golutvin,

N. Gorbunov, I. Gramenitsky, I. Ivantchenko, A. Janata, V. Kalagin, V. Karjavin, S. Khabarov,

V. Khabarov, Y. Kiryushin, V. Kolesnikov, V. Konoplyanikov, V. Korenkov, I. Kossarev,

T. Kracikova, V. Krasnov, A. Litvinenko, V. Lysiakov, A. Koutov, A. Malakhov,

G. Mechtcheriakov, I. Melnichenko, V. Mitsyn, P. Moissenz, S. Movchan, V. Palichik,

V. Perelygin, Y. Petukhov, M. Popov, D. Pose, R. Pose, A. Samoshkin, M. Savina, S. Sergeev,

S. Shmatov, A. Skatchkova, V. Smirnov, D. Smolin, E. Tikhonenko, V. Uzhinskii, N. Vlasov,

A. Volodko, A. Yukaev, N. Zamiatin, A. Zarubin, P. Zarubin, E. Zubarev

# Petersburg Nuclear Physics Institute, Gatchina (St Petersburg), RUSSIA

A. Atamanchuk, V. Barashko, N. Bondar, L. Chtchipounov, A. Denissov, G. Gavrilov,

V. Golovtsov, Y. Gusev, Y. Ivanov, O. Kisselev, V. Kozlov, E. Kouznetsova, E. Lobatchev,

G. Makarenkov, E. Orichtchine, A. Petrunin, O. Prokofiev<sup>17</sup>, V. Rasmislovich, B. Razmyslovich,

V. Sknar, I. Smirnov, S. Sobolev, V. Soulimov, V. Souvorov, A. Vassiliev, G. Velitchko,

S. Volkov, A. Vorobyov

# Institute for Nuclear Research, Moscow, RUSSIA

G.S. Atoyan, V. Bolotov, S. Gninenko, N. Goloubev, E.V. Gushin, M. Kirsanov, A. Kovzelev, V. Matveev, A. Pashenkov, A. Poliarouch, N. Krasnikov, S. Laptev, A. Proskouriakov, A. Sadovski, I. Semeniouk, V. Shmatkov, A. Skassyrskaia<sup>6</sup>, A. Toropin<sup>6</sup>

# Institute for Theoretical and Experimental Physics, Moscow, RUSSIA

E. Dorochkevitch, V. Gavrilov, V. Kaftanov, A. Khanov<sup>18</sup>, I. Kisselevitch, V. Kolosov, M. Kossov, S. Koulechov, A. Krokhotine, A. Oulianov, N. Stepanov, V. Stoline, S. Uzunyan

# P.N. Lebedev Physical Institute, Moscow, RUSSIA

E. Devitsin, A.M. Fomenko, N. Konovalova, V. Kozlov, A.I. Lebedev, N. Loktionova, N. Lvova, S. Potashov, S.V. Rusakov, A. Terkulov

#### Moscow State University, Moscow, RUSSIA

A. Belsky, V. Bodyagin, E. Boos, A. Cherstney, A. Demianov, M. Dubinin, L. Dudko, A. Erchov, R. Gloukhov, A. Gribushin, V. Ilin, O.L. Kodolova, V. Korotkikh, A. Krioukov, N.A. Kruglov, I.P. Lokhtin, V. Mikhailin, S. Petrouchanko, A. Poukhov, L. Sarycheva, V. Slad, A. Sniguirev, I. Vardanyan, A. Vassiliev

# High Temperature Technology Center of Research & Development Institute of Power Engineering (HTTC RDIPE), Moscow, RUSSIA (Associated Institute)

D. Chmelev, A. Ivanov, V. Koudinov, O. Logatchev, S. Onishchenko, A. Orlov, V. Sakharov, V. Smetannikov, S. Zavodthikov

# Institute for High Energy Physics, Protvino, RUSSIA

A. Abramov, V. Abramov, I. Azhgirey, S. Bitioukov, K. Datsko, A. Dolgopolov, V. Evdokimov, V. Falaleev<sup>2</sup>, P. Goncharov, A. Invakin, V. Katchanov, Y. Kharlov, V. Klioukhine, E. Kolatcheva, A. Korablev, Y. Korneev, A. Kostritski, A. Krinitsyn, V. Kryshkin, O. Lapyguina,

A. Levine, A. Markov, V. Medvedev, M. Oukhanov, V. Pak, D. Patalakha, V. Petrov, V. Pikalov,

V. Potapov, A. Riabov, A. Sannikov, P. Shagin, Z. Simonova, E. Skvortsova, S. Slabospitski, A. Sobol, V. Solovianov, V. Sougonyaev, S. Stepouchkine, A. Surkov, A. Sytin, B. Tchuiko,

N.E. Tyurin, S. Tereschenko, S. Troshin, L. Turchanovich, A. Uzunian,

A. Zaitchenko, S. Zelepoukine

CMS Collaboration CMS Trigger TDR

# Russian Federal Nuclear Centre - Scientific Research Institute for Technical Physics (RFNC-VNIITF), Snezhinsk, RUSSIA (Associated Institute)

A. Andriyash, A. Chtcherbakov, D. Gorchkov, D. Griaznykh, O. Gueinak, D. Korotchine, S. Kotegov, A. Maloiaroslavtsev, M. Naoumenko, I. Pavlov, S. Samarine, R. Skripov

# Slovak University of Technology, Bratislava, SLOVAK REPUBLIC

P. Ballo, J. Lipka, V. Necas, M. Seberini, K. Vitazek

Centro de Investigaciones Energeticas Medioambientales y Tecnologicas, Madrid, SPAIN M. Aguilar-Benitez, J. Alberdi, J.M. Barcala, M. Cerrada, N. Colino, M. Daniel, M. Fernandez Garcia, A. Ferrando, M.C. Fouz, M.I. Josa, P. Ladron De Guevara, J. Marin, A. Molinero, J.C. Oller, J.L. Pablos, J. Puerta Pelayo, L. Romero, J. Salicio, C. Willmott

#### Universidad Autónoma de Madrid, Madrid, SPAIN

C. Albajar

# Universidad de Oviedo, Oviedo, SPAIN

J. Cuevas

# Instituto de Física de Cantabria (IFCA), CSIC-Universidad de Cantabria, Santander, SPAIN

P. Arce, E. Calvo, C. Figueroa, G. Gomez Ceballos, I. Gonzalez, J.M. Lopez, M.A. Lopez Virto, J. Marco, F. Matorras, T. Rodrigo, A. Ruiz Jimeno, I. Vila

# Universität Basel, Basel, SWITZERLAND

P. Garcia-Abia, L. Tauscher, S. Vlachos, M. Wadhwa

# CERN, European Organization for Nuclear Research, Geneva, SWITZERLAND

D. Abbaneo<sup>6</sup>, R. Alemany-Fernandez, A. Annenkov<sup>19</sup>, P. Aspell, E. Auffray, P. Azzurri, P. Baillon, A. Ball, R. Barillere, D. Barney, D. Blechschmidt, P. Bloch, M. Bosteels, S. Braibant, H. Breuker, P. Brooks<sup>20</sup>, D. Campi, A. Caner, E. Cano, F. Carena, A. Cattai, F. Cavallari, G. Cervelli, R. Chierici, J. Christiansen, S. Cittolin, B. Cure, C. D'Ambrosio, A. De Roeck, T. De Visser, D. Delikaris, M. Della Negra, A. Elliott-Peisert, B. Faure, A. Favara, P. Figueiredo, H. Foeth, R. Folch, A. Frey, W. Funk, A. Furtjes, A. Gaddi, J.C. Gayde, H. Gerwig, K. Gill<sup>21</sup>, W. Glessing, R. Goudard, P. Gras, J.P. Grillet, J. Gutleber, F. Hahn, S. Hameed Khan<sup>22</sup>, R. Hammarstrom, M. Hansen, E.H.M. Heijne, A. Hervé, A. Honma, M. Huhtinen, V. Innocente, W. Jank, P. Janot, P. Jarron, M. Kado, K. Kloukinas, C. Koch, M. Konecki, Z. Kovacs, V. Lara, C. Lasseur, J.M. Le Goff, M. Lebeau, P. Lecoq, M. Letheren, M. Liendl, C. Ljuslin, B. Lofstedt, R. Loos, R. Mackenzie, R. Malina, M. Mannelli, E. Manola-Poggioli, A. Marchioro, J.C. Marin, C. Mariotti, C. Martinez Rivero, J. Matheson, J.M. Maugain, F. Meijers, M. Mermoud, E. Meschi, E. Migliore, J. Mocholi Moncholi<sup>23</sup>, A. Moutoussi, N. Neumeister, A. Nikitenko<sup>24</sup>, A. Oh, A. Onnela, M. Oriunno, L. Orsini, G. Pa'Sztor, L. Pape, C. Palomares Espiga, G. Passardi, P. Petagna, A. Pfeiffer, M. Pimiä, R. Pintus, E. Piotto, B. Pirollet, A. Placci, J.P. Porte, H. Postema, J. Pothier, R. Principe, A. Quadt, A. Racz, P. Rebecchi, P. Reis, S. Revnaud, H. Rezvani Naraghi, R. Ribeiro, J. Roche, P. Rodrigues Simoes Moreira, T. Rohe, G. Rolandi, H. Sakulin, D. Samyn, J.C. Santiard, W. Schleifer, R. Schmidt, M. Schroder, C. Schwick, P. Sempere Roldan, P. Sharp<sup>25</sup>, P. Siegrist, F. Sikler, A. Simma, P. Spagnolo, P. Sphicas<sup>26</sup>, H. Stockinger, F. Szoncso, B.G. Taylor, D. Tchougounov<sup>19</sup>, T. Toifl, N. Toth<sup>20</sup>, D. Treille, J. Troska, E. Tsesmelis, A. Tsirou, F. Van Lingen<sup>20</sup>, F. Vasey, T. Virdee<sup>21</sup>, H. Voss, W. Weingarten, J.P. Wellisch, P. Wertelaers, M. Wilhelmsson, I.M. Willers, M. Winkler<sup>27</sup>, S. Wynhoff

ix

# Paul Scherrer Institut, Villigen, SWITZERLAND

M. Barbero, R. Baur, W. Bertl, K. Deiters, P. Dick, A. Dijksman, K. Gabathuler, J. Gobrecht, G. Heidenreich, R. Horisberger, O. Ingram, D. Kotlinski, R. Morf, D. Renker, R. Schnyder

# Institut für Teilchenphysik, Eidgenössische Technische Hochschule (ETH), Zürich, **SWITZERLAND**

H. Anderhub, G. Antchev $^{28}$ , A. Badertscher, A. Barczyk, B. Betev, A. Biland, B. Blau, D. Bourilkov $^{28}$ , A. Bueno, M. Campanelli, P. Cannarsa, C. Carpanese, N. Chivarov $^{28}$ , M. Dittmar<sup>2</sup>, L. Djambazov, R. Eichler, W. Erdmann<sup>10</sup>, G. Faber, J.L. Faure, M. Felcini, K. Freudenreich, I. Gil Botella, C. Grab, M. Hilgers, H. Hofer, A. Holzner, I. Horvath, C. Humbertclaude<sup>2</sup>, B. Iliev<sup>28</sup>, P. Ingenito, J. Kuipers, P. Le Coultre, P. Lecomte, B. List, W. Lustermann, I. Nanov, F. Nessi-Tedaldi, R.A. Ofierzynski, A. Patino Revuelta<sup>2</sup>, F. Pauss, G. Rahal, J.F. Rico, C.H. Rivetta<sup>2</sup>, U. Roeser, A. Rubbia, H. Rykaczewski, A. Schoning, N. Sinanis, H. Suter, S. Udriot, J. Ulbricht, I. Veltchev<sup>28</sup>, G. Viertel, H. Von Gunten, S. Waldmeier-Wicki, A. Zanet<sup>2</sup>

# Universität Zürich, Zürich, SWITZERLAND

C. Amsler, R. Kaufmann, H. Pruys, C. Regenfus, P. Riedler, P. Robmann, T. Speer, S. Steiner

# Cukurova University, Adana, TURKEY

I. Dumanoglu, E. Eskut, A. Kayis Topaksu, A. Kuzucu-Polatoz, G. Onengut, N. Ozdes Koca

# Middle East Technical University, Physics Department, Ankara, TURKEY

A.M. Guler, M. Serin-Zeyrek, R. Sever, P. Tolun, H. Yildiz, M. Zeyrek

# Bogazici University, Department of Physics, Istanbul, TURKEY

E. Gulmez, R. Unalan

# Institute of Single Crystals of National Academy of Science, Kharkov, UKRAINE

A. Borisenko, B. Grinev, V. Lebedev, V. Lyubynskiy, V. Senchyshyn, V. Vasilchuk

# National Scientific Center, Kharkov Institute of Physics and Technology, Kharkov, UKRAINE

L. Levchuk, A. Nemashkalo, V. Popov, P. Sorokin

# Kharkov State University, Kharkov, UKRAINE

S. Duplij, N.A. Kluban, I. Zalyubovskiy

# University of Bristol, Bristol, UNITED KINGDOM

D.S. Bailey, J.J. Brooke, D. Cussans, R.D. Head, G.P. Heath, H.F. Heath, C.K. Mackay, D.M. Newbold, A.D. Presland, M.G. Probert, V.J. Smith, R.J. Tapper

# Centre for Complex Cooperative Systems, University of the West of England, Bristol, **UNITED KINGDOM (Associated Institute)**

N. Baker, A. Barry, G. Chevenier, F. Estrella, G. Mathers<sup>2</sup>, R. McClatchey<sup>2</sup>

# Rutherford Appleton Laboratory, Didcot, UNITED KINGDOM

S.A. Baird, R.A. Barlow, E. Bateman, K.W. Bell, R.M. Brown, D.J. Cockerill, J.A. Coughlan, L.G. Denton, P.S. Flower, V.B. Francis, M. French, J. Greenhalgh, R. Halsall, W.J. Haynes, F.R. Jacob, P.W. Jeffreys, L. Jones, B.W. Kennedy, L. Lintern, A.B. Lodge, J. Maddox, S. Martin, Q.R. Morrissey, P. Murray, P. Rabbetts, A.A. Shah, B. Smith, S. Spagnolo, M. Sproston, R. Stephenson, P. Thayaparan, I. Tomalin, M. Torbet, J. Williams

#### Imperial College, University of London, London, UNITED KINGDOM

M. Apollonio, G. Barber, R. Beuselinck, D. Britton, W. Cameron, E. Corrin, G. Davies, C. Foudas, J. Fulcher, G. Hall, J. Hays, G. Iles, B.C. Macevoy, N. Marinelli, E.M. McLeod, E. Noah Messomo, D.M. Raymond, P.J. Savage, C. Seez, L. Toudup, P. Walsham

# Brunel University, Uxbridge, UNITED KINGDOM

R. Broadhead, B. Camanzi, P.R. Hobson, D.C. Imrie, A. McKemey, O. Sharif, S.J. Watts

# University of California at Davis, Davis, California, USA

R. Breedon, P.T. Cox, J. Gunion, S. Hershman, B. Holbrook, W. Ko, R. Lander, P. Murray, D. Pellett, J. Smith, M. Tripathi, R. Vogt

# University of California San Diego, La Jolla, California, USA

S. Bhattacharya, J.G. Branson, I. Fisk, J.P. Fryckman, D. Macfarlane, M. Mojaver, H.P. Paar, G. Raven, V. Sharma, A. White

# University of California at Los Angeles, Los Angeles, California, USA

K. Arisaka, A. Attal, F. Chase, D. Cline, R. Cousins, S. Erhan, J. Hauser, M. Lindgren, C. Matthey, S. Otwinowski, Y. Pischalnikov, P. Schlein, Y. Shi, B. Tannenbaum, M. Von Der Mey, H.G. Wang

# California Institute of Technology, Pasadena, California, USA

J. Bunn, G. Denis, P. Galvez, M. Gataullin, M. Hafeez<sup>2</sup>, T. Hickey, K. Holtman, I. Legrand, V. Litvine, H.B. Newman, A. Samar, S. Shevchenko, R. Wilkinson, L. Xia, R.Y. Zhu

# University of California, Riverside, California, USA

R. Clare, I. Crotty<sup>2</sup>, J.W. Gary, J.G. Layter, H. Rick, B.C. Shen, V. Sytnik, D. Zer-Zion<sup>2</sup>

# Fairfield University, Fairfield, Connecticut, USA

C.P. Beetz, G. Cirino, V. Podrasky, C. Sanzeni, D. Winn

# University of Florida, Gainesville, Florida, USA

D. Acosta, P. Avery, S. Dolinsky, R.D. Field, L. Gorn, S. Klimenko, J. Konigsberg, A. Korytov, A. Madorsky, G. Mitselmakher<sup>17</sup>, A. Nomerotski, P. Ramond, B. Scurlock, S.M. Wang, J. Yelton

# Florida State University, Tallahassee, Florida, USA

H. Baer, M. Bertoldi, H. Goldman, S. Hagopian, V. Hagopian, K.F. Johnson, H.B. Prosper, J. Thomaston, H. Wahl

# Fermi National Accelerator Laboratory, Batavia, Illinois, USA

G. Apollinari, M. Atac, S. Aziz, E. Barsotti, L.A.T. Bauerdick, A. Baumbaugh, U. Baur, A. Beretvas, M. Binkley, M. Bowden, J.N. Butler, N. Chester, I. Churin, S. Cihangir, M. Crisler, D. Denisov, M. Diesburg, D.P. Eartly, J.E. Elias, S. Feher, B. Flaugher, J. Freeman, I. Gaines, H. Glass, D.A. Glenzinski, J. Goldstein, D. Green, J. Hanlon, S. Hansen, R.M. Harris, J. Incandela, U. Joshi, S. Kwan, M. Lamm, S. Lammel, D. Lazic, R. Lee, R. Lipton, M. Litmaath, S. Los, P. Lukens, K. Maeshima, J.M. Marraffino, S. Mishra, N. Mokhov, C. Moore, S. Muzaffar, V. O'Dell, J. Patrick, R. Pordes, R. Raja, P. Rapidis, M. Reichanadter, A. Ronzhin, V. Rykalin, T. Shaw, M. Shea, E. Skup, R.P. Smith, L. Spiegel, D. Stuart, I. Suzuki, S. Tkaczyk, R. Tschirhart, R. Vidal, R. Wands, H. Wenzel, J. Whitmore, W.J. Womersley, W.M. Wu, A. Yagil, V. Yarba

# University of Illinois at Chicago (UIC), Chicago, Illinois, USA

M.R. Adams, C.E. Gerber, K. Papageorgiou, J. Solomon

хi

CMS Trigger TDR CMS Collaboration

#### Northwestern University, Evanston, Illinois, USA

B. Gobbi, S. Malik, R. Tilden

# University of Notre Dame, Notre Dame, Indiana, USA

B. Baumbaugh, J.M. Bishop, N.M. Cason, M. Hildreth, D.J. Karmgard, R. Ruchti, J. Warchol, M. Wayne

# Purdue University - Tasks D & G, West Lafavette, Indiana, USA

V.E. Barnes, G. Bolla, D. Bortoletto, A. Bujak, A.F. Garfinkel, L. Gutay, M. Kopal, A.T. Laasanen, S. Medved, I. Pal, C. Rott, A. Roy, A. Sedov

#### Iowa State University, Ames, Iowa, USA

E.W. Anderson, H. Chakir, J.M. Hauptman, J. Krane

# The University of Iowa, Iowa City, Iowa, USA

U. Akgun, A.S. Ayan, A. Cooper, M. Fountain, E. McCliment, J.P. Merlo, M.J. Miller, Y. Onel, I. Schmidt

# Johns Hopkins University, Baltimore, Maryland, USA

B.A. Barnett, C.Y. Chien, H.S. Cho, G. Liang, M. Swartz, X. Xie

# University of Maryland, College Park, Maryland, USA

S. Abdullin<sup>24</sup>, S. Arcelli, D. Baden, R. Bard, S.C. Eno, D. Fong, T. Grassi, N.J. Hadley, R.G. Kellogg, S. Kunori, A. Sharma, A. Skuja

# Boston University, Boston, Massachusetts, USA

R. Carey, E. Hazen, E. Kearns, E. Machado, J. Miller, D. Osborne, B.L. Roberts, J. Rohlf, L. Sulak, J.D. Sullivan, S. Wu

#### Northeastern University, Boston, Massachusetts, USA

G. Alverson, H. Fenker, I. Gaponenko, J. Moromisato, Y.V. Musienko<sup>29</sup>, S. Nicol, T. Paul, S. Reucroft, J. Swain, L. Taylor, E. Von Goeler, T. Yasuda

# Massachusetts Institute of Technology, Cambridge, Massachusetts, USA

G. Bauer, J. Friedman, C. Paus, S. Pavlon, L. Rosenson, K.S. Sumorok, S. Tether, J. Tseng

# University of Minnesota, Minneapolis, Minnesota, USA

P. Cushman, A.H. Heering, I. Kronkvist, R. Rusack, A. Singovsky, P. Vikas

#### University of Mississippi, University, Mississippi, USA

K. Bhatt, M. Booke, L. Cremaldi, R. Kroeger, J. Reidy, D. Sanders, D. Summers

# University of Nebraska-Lincoln, Lincoln, Nebraska, USA

W.B. Campbell, D.R. Claes, C. Lundstedt, G.R. Snow

# Rutgers, the State University of New Jersey, Piscataway, New Jersey, USA

E. Bartz, J. Conway, T. Devlin, J. Doroshenko, P.F. Jacques, M.S. Kalelkar, T. Koeth, A. Lath, L. Perera, S. Schnetzer, S. Somalwar, R. Stone, G. Thomson, T.L. Watts

# Princeton University, Princeton, New Jersey, USA

J.M. Bussat, P. Denes, V. Gupta, J. Mans, D. Marlow, P. Piroue, D. Stickland, C. Tully, T. Wildish

CMS Collaboration CMS Trigger TDR

CWS Conadoration CWS Trigger TDR

# University of Rochester, Rochester, New York, USA

S.R. Blusk, A. Bodek, H. Budd, P. De Barbaro, A. Dyshkant, G. Ginther, M.C. Kruse, D. Ruggiero, W. Sakumoto, P. Slattery, P. Tipton

# The Ohio State University, Columbus, Ohio, USA

B. Bylsma, L.S. Durkin, J. Gilmore, J. Gu, D. Herman, C. Kim, D. Larsen, T.Y. Ling, C.J. Rush, V. Sehgal

# Carnegie Mellon University, Pittsburgh, Pennsylvania, USA

T. Ferguson, J. Russ, N. Terentyev, H. Vogel, I. Vorobiev

#### Rice University, Houston, Texas, USA

N. Adams, M. Corcoran, G. Eppley, J. Lamas-Valverde, M. Matveev, H.E. Miettinen, T. Nussbaum, P. Padley, E. Platner, J. Roberts, P. Yepes

# Texas Tech University, Lubbock, Texas, USA

N. Akchurin, J. Cranshaw, V. Nagaslaev, V. Papadimitriou, A. Sill, R. Wigmans

# University of Texas at Dallas, Richardson, Texas, USA

R.C. Chaney, E.J. Fenyves, H.D. Hammack, M.R. O'Malley, D. Suson, A.V. Vassiliev

# Virginia Polytechnic Institute and State University, Blacksburg, Virginia, USA

H. Meyer, L. Mo, T.A. Nunamaker

# University of Wisconsin, Madison, Wisconsin, USA

D. Carlsmith, P. Chumney, S. Dasu, F. Feyzi, M. Jaworski, J. Lackey, R. Loveless, S. Lusin, D. Reeder, W.H. Smith

# Institute of Nuclear Physics of the Uzbekistan Academy of Sciences, Ulugbek, Tashkent, UZBEKISTAN

A. Avezov, M. Belov, N. Bisenov, A. Gafarov, E. Gasanov, E. Ibragimova, G. Kim, Y. Koblik, N. Rakhmatov, I. Rustamov, I. Shukrullo, A. Urkinbaev, B.S. Yuldashev

- 1. Also at Inst. of Physics Academy of Science, Tbilisi, Georgia

- 2. Also at CERN, Geneva, Switzerland

- 3. Also at NIKHEF, Amsterdam, Netherlands

- 4. Also at Moscow State Univ., Moscow, Russia

- 5. Also at Inst. für Teilchenphysik, ETH, Zürich, Switzerland

- 6. Also at Univ. di Pisa e Sez. dell' INFN, Pisa, Italy

- 7. Also at Institute Rudjer Boskovic, Zagreb, Croatia

- 8. Also at Université de Haute-Alsace, Mulhouse, France

- 9. Also at Université Louis Pasteur, Strasbourg, France

- 10. Also at Paul Scherrer Inst., Villigen, Switzerland

- 11. Also at Humboldt-Univ. zu Berlin, Berlin, Germany

- 12. Also at Institute of Nuclear Research ATOMKI, Debrecen, Hungary

- 13. Also at Univ. of California, Riverside, California, USA

- 14. Also at Politecnico di Milano, Milano, Italy

CMS Trigger TDR CMS Collaboration

- 15. Also at Univ. of Bucharest, Bucuresti-Magurele, Romania

- 16. Also at ENEA Casaccia Research Center, S. Maria di Galeria, Italy

- 17. Also at Fermi National Accelerator Lab., Batavia, Illinois, USA

- 18. Also at Kansas State Univ., Manahattan, Kansas, USA

- 19. Also at Bogoroditsk Tech. Plant (BTCP), Moscow

- 20. Also at Centre for Complex Coop. Systems, Univ. of the West of England, Bristol, UK

- 21. Also at Imperial College, Univ. of London, London, United Kingdom

- 22. Also at AI Techn. Corp. of Pakistan (PVT) Ltd, Islamabad, Pakistan

- 23. Also at CIEMAT, Madrid, Spain

- 24. Also at Inst. for Theoretical and Exp. Phys., Moscow, Russia

- 25. Also at RAL, Didcot, United Kingdom

- 26. Also at MIT, Cambridge, Massachussets, USA

- 27. Also at HEPHY, Wien, Austria

- 28. Also at Inst. for Nucl. Research and Nucl. Energy, Sofia, Bulgaria

- 29. Also at Inst. for Nucl. Research, Moscow, Russia

- 30. Also at INESC, Lisbon, Portugal

- 31. Also at IST, Technical University of Lisbon, Portugal

Acknowledgements CMS Trigger TDR

# Acknowledgements

The CMS Trigger and Data Acquisition group wish to thank all the technical staff involved in the design, prototyping, and testing work for their invaluable contributions.

We wish to express our thanks to Kirsti Aspola, Madeleine Azeglio, Delphine Labrousse, Anne Lissajoux, Guy Martin, Sandra Monachon, and Marie-Claude Pelloux for their help and assistance with innumerable tasks. Their expertise and dedication are truly appreciated.

Special thanks go to Sergio Cittolin for his artist's view of the Trigger project, which graces the cover of this report.

# **Table of Contents**

| C            | MS T  | rigger T                 | IDR Editorial Board                          | . i |

|--------------|-------|--------------------------|----------------------------------------------|-----|

| $\mathbf{C}$ | MS C  | ollabora                 | ation                                        | ii  |

| A            | cknov | vledgem                  | ents                                         | χV  |

|              |       | _                        | ntsx                                         |     |

|              |       |                          |                                              |     |

| 1            |       |                          | rview                                        |     |

|              |       |                          | ction                                        |     |

|              | 1.2   |                          | ry of Requirements                           |     |

|              |       | 1.2.1                    | Physics Requirements                         |     |

|              |       | 1.2.2                    | System Requirements                          |     |

|              |       | 1.2.3                    | Rate Requirements                            |     |

|              | 1.2   | 1.2.4                    | Structural Requirements                      |     |

|              | 1.3   |                          | w of Trigger Structure                       |     |

|              |       | 1.3.1                    | Level 1                                      |     |

|              | 1.4   | 1.3.2                    | High Level Triggers                          |     |

|              | 1.4   |                          | w of Level 1 Trigger Organization            |     |

|              |       | 1.4.1                    | Introduction                                 |     |

|              |       | 1.4.2                    | Calorimeter Trigger                          |     |

|              |       | 1.4.3<br>1.4.4           | Muon Trigger                                 |     |

|              |       |                          | Global Trigger                               |     |

|              |       | 1.4.5<br>1.4.6           | Timing, Trigger and Control System           |     |

|              |       | 1.4.0                    | Physical Location of the Trigger Electronics |     |

|              |       | 1.4.7                    | Coordinates and unit requirements            |     |

| 2            | Dogu  |                          | =                                            |     |

| 4            | _     |                          | ts                                           |     |

|              | 2.1   | •                        | Requirements                                 |     |

|              |       | 2.1.1                    | Cross Sections and Rates                     |     |

|              |       | 2.1.2                    | Physics Simulation Tools                     |     |

|              |       | 2.1.3                    | Review of Physics Channels                   |     |

|              |       | 2.1.4                    | Trigger Requirements                         |     |

|              | 2.2   | 2.1.5                    | Background                                   |     |

|              |       |                          | neter Trigger Requirements                   |     |

|              |       |                          | rigger Requirements                          |     |

|              | 2.4   |                          | Efficiency Measurement                       |     |

|              |       | 2.4.1                    | Electron/Photon and Muon Triggers            |     |

|              |       | 2.4.2                    | Triggering of leptons inside jets            |     |

|              |       | 2.4.3                    | τ Trigger                                    |     |

|              |       | 2.4.4                    | Jet Triggers                                 |     |

|              |       | 2.4.5                    | Missing E <sub>T</sub> Trigger.              |     |

|              | 2 5   | 2.4.6<br><b>P</b> oquire | Technical Triggersements for Heavy Ion Runs  |     |

| 2            |       | -                        | · · · · · · · · · · · · · · · · · · ·        |     |

| 3            |       |                          | Trigger Introduction                         |     |

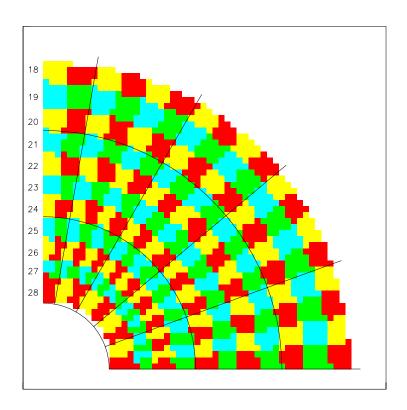

|              | 3.1   |                          | alorimetry                                   |     |

|              |       | 3.1.1                    | Electromagnetic Calorimeter                  |     |

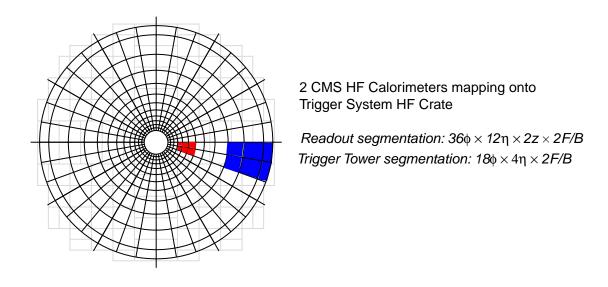

|              |       | 317                      | Hadronic Calorimeter                         | 34  |

|   | 3.2                      | Calorin                                                                                                                                  | neter Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34              |

|---|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|   | 3.3                      | Calorin                                                                                                                                  | neter Trigger Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 36              |

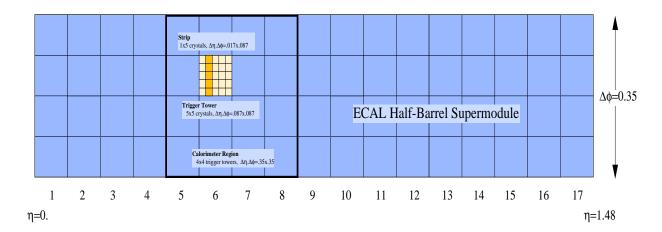

|   |                          | 3.3.1                                                                                                                                    | Geometry and Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |

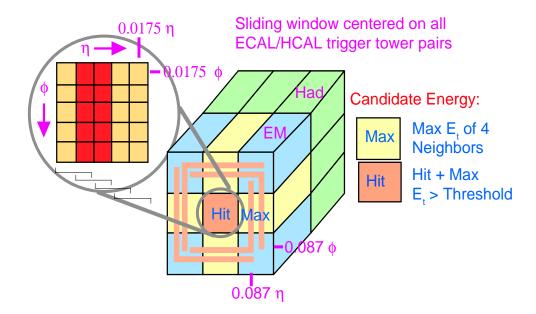

|   |                          | 3.3.2                                                                                                                                    | Trigger Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 40              |

|   |                          | 3.3.3                                                                                                                                    | Electron and Photon Triggers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42              |

|   |                          | 3.3.4                                                                                                                                    | Jet and τ Triggers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

|   |                          | 3.3.5                                                                                                                                    | Energy Triggers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45              |

|   |                          | 3.3.6                                                                                                                                    | Quiet and MIP Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46              |

|   |                          | 3.3.7                                                                                                                                    | Calorimeter Trigger Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47              |

|   | 3.4                      | Algorit                                                                                                                                  | hm Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47              |

|   |                          | 3.4.1                                                                                                                                    | Simulation Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47              |

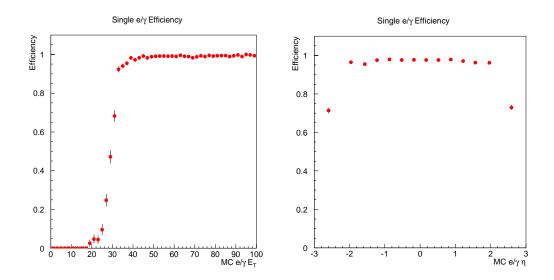

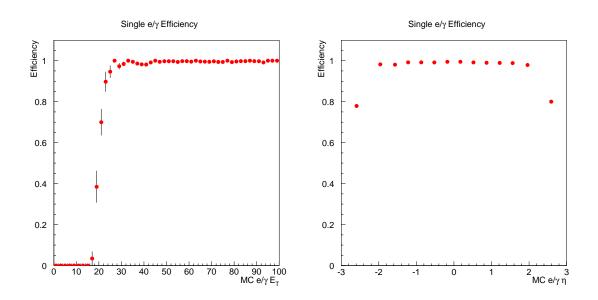

|   |                          | 3.4.2                                                                                                                                    | Electron and Photon Trigger Efficiencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |

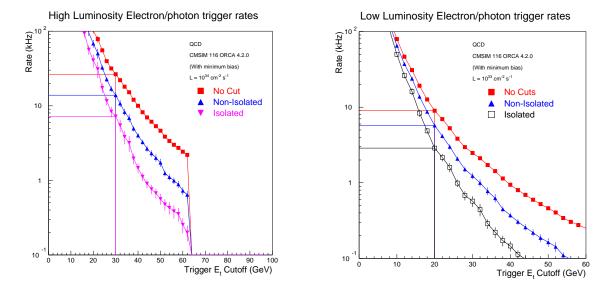

|   |                          | 3.4.3                                                                                                                                    | Electron and Photon Trigger Background Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |

|   |                          | 3.4.4                                                                                                                                    | Jet Trigger Rate and Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50              |

|   |                          | 3.4.5                                                                                                                                    | τ Trigger Rate and Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |

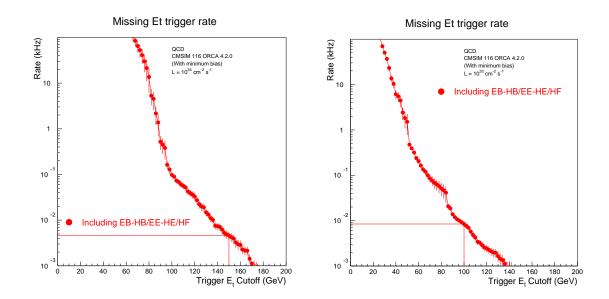

|   |                          | 3.4.6                                                                                                                                    | Missing E <sub>T</sub> Trigger Rate and Efficiency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 52              |

|   |                          | 3.4.7                                                                                                                                    | Sample Trigger Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |

|   | 3.5                      | Overall                                                                                                                                  | Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |

|   |                          | 3.5.1                                                                                                                                    | Calorimeter Trigger Subdivisions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |

|   |                          | 3.5.2                                                                                                                                    | Trigger Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

|   |                          | 3.5.3                                                                                                                                    | Regional Calorimeter Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |

|   |                          | 3.5.4                                                                                                                                    | Global Calorimeter Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

|   |                          |                                                                                                                                          | Robustness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

|   |                          |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |

| 4 |                          |                                                                                                                                          | Trigger Primitive Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |

| 4 |                          | Require                                                                                                                                  | ements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61              |

| 4 |                          | Require<br>4.1.1                                                                                                                         | ements Functional Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>61</b>       |

| 4 |                          | 4.1.1<br>4.1.2                                                                                                                           | Functional Requirements Performance Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>61</b> 61 62 |

| 4 |                          | <b>Require</b> 4.1.1 4.1.2 4.1.3                                                                                                         | ements  Functional Requirements  Performance Requirements  Interface Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |

| 4 |                          | <b>Require</b> 4.1.1 4.1.2 4.1.3 4.1.4                                                                                                   | Functional Requirements Performance Requirements Interface Requirements Testing Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |

| 4 | 4.1                      | <b>Require</b> 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5                                                                                             | Punctional Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |

| 4 | 4.1                      | <b>Require</b> 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 <b>System</b>                                                                               | Functional Requirements Performance Requirements Interface Requirements Testing Requirements Upgradability or Flexibility Requirements Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |

| 4 | 4.1                      | Require 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 System Information                                                                                 | Functional Requirements Performance Requirements Interface Requirements Testing Requirements Upgradability or Flexibility Requirements Overview ation from the Calorimeter                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

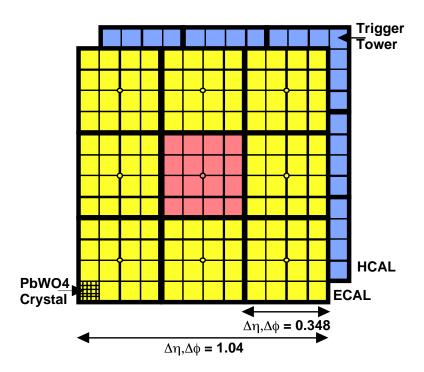

| 4 | 4.1                      | 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br><b>System</b><br><b>Inform</b><br>4.3.1                                                     | Functional Requirements  Performance Requirements  Interface Requirements  Testing Requirements  Upgradability or Flexibility Requirements  Overview  ation from the Calorimeter  Trigger Tower Definition                                                                                                                                                                                                                                                                                                                                                                                            |                 |

| 4 | 4.1                      | Require 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 System Informa 4.3.1 4.3.2                                                                         | Functional Requirements Performance Requirements Interface Requirements Testing Requirements Upgradability or Flexibility Requirements Overview ation from the Calorimeter Trigger Tower Definition Data Formats for ECAL and HCAL                                                                                                                                                                                                                                                                                                                                                                    |                 |

| 4 | 4.1                      | Require 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 System Informa 4.3.1 4.3.2 4.3.3                                                                   | Functional Requirements Performance Requirements Interface Requirements Testing Requirements Upgradability or Flexibility Requirements Overview Trigger Tower Definition Data Formats for ECAL and HCAL Synchronization of the Trigger Tower Channels                                                                                                                                                                                                                                                                                                                                                 |                 |

| 4 | 4.1                      | Require 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 System Informa 4.3.1 4.3.2 4.3.3 4.3.4                                                             | Functional Requirements Performance Requirements Interface Requirements Testing Requirements Upgradability or Flexibility Requirements Overview Trigger Tower Definition Data Formats for ECAL and HCAL Synchronization of the Trigger Tower Channels Suppression of Bad Channels                                                                                                                                                                                                                                                                                                                     |                 |

| 4 | 4.1                      | Require 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 System Inform 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5                                                        | Functional Requirements Performance Requirements Interface Requirements Upgradability or Flexibility Requirements Overview ation from the Calorimeter Trigger Tower Definition Data Formats for ECAL and HCAL Synchronization of the Trigger Tower Channels Suppression of Bad Channels Zeroing of Channels during Monitoring                                                                                                                                                                                                                                                                         |                 |

| 4 | 4.1                      | Require 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 System Informa 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.3.6                                                 | Functional Requirements Performance Requirements Interface Requirements Upgradability or Flexibility Requirements Overview Trigger Tower Definition Data Formats for ECAL and HCAL Synchronization of the Trigger Tower Channels Suppression of Bad Channels Zeroing of Channels during Monitoring Linearization of ECAL Data and Scale Transformation                                                                                                                                                                                                                                                |                 |

| 4 | 4.1<br>4.2<br>4.3        | Require 4.1.1 4.1.2 4.1.3 4.1.4 4.1.5 System Informa 4.3.1 4.3.2 4.3.3 4.3.4 4.3.5 4.3.6 4.3.7                                           | Functional Requirements Performance Requirements Interface Requirements Upgradability or Flexibility Requirements Overview Trigger Tower Definition Data Formats for ECAL and HCAL Synchronization of the Trigger Tower Channels Suppression of Bad Channels Zeroing of Channels during Monitoring Linearization of HCAL Data and Scale Transformation Linearization of HCAL Data and Scale Transformation                                                                                                                                                                                            |                 |