83

#### 4.8 HIGH VOLTAGE

The circuits described in this section perform the following functions:

- Generate a 16kHz sine wave by band-pass filtering a 16kHz squarewave from the Reference Divider Assembly

- (2) Control the amplitude of the 16kHz sine wave in a voltage-controlled amplifier, followed by power amplification to drive a step-up HV transformer.

- (3) Rectify and filter the HV transformer secondary voltage to provide DC voltages to the I+terminal:

- -200V to +200V on 100V Range -1200V to +1200V on 1000V Range

- (4) Sense the voltages at the output terminals (or at the load in Remote Sense)

(5) Attenuate the sensed voltage and compare against the DC Reference Voltage in the Error Amplifier, using the error voltage as drive to the Voltage-Controlled Amplifier.

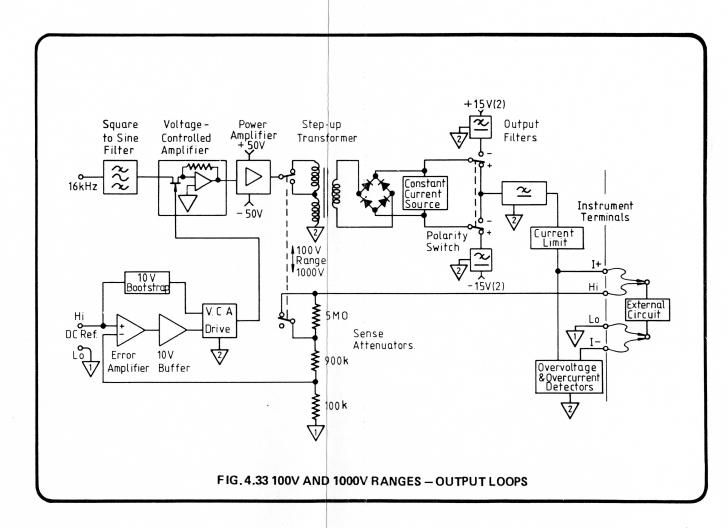

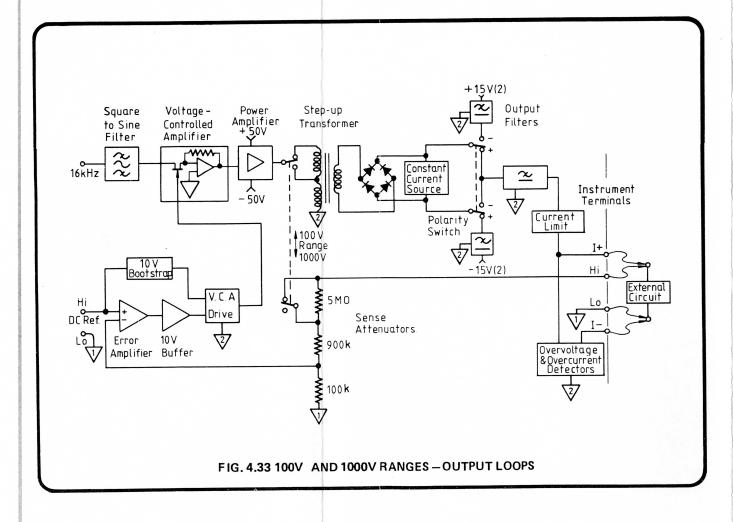

The circuits together form a negative-feedback loop which refers the output DC voltage to the value of the DC Reference Voltage, using AC drive transformation and DC sense attenuation as means of achieving the required high voltage outputs. This is illustrated in Fig. 4.33, which shows 100V Range selected, positive output in remote sense with output on.

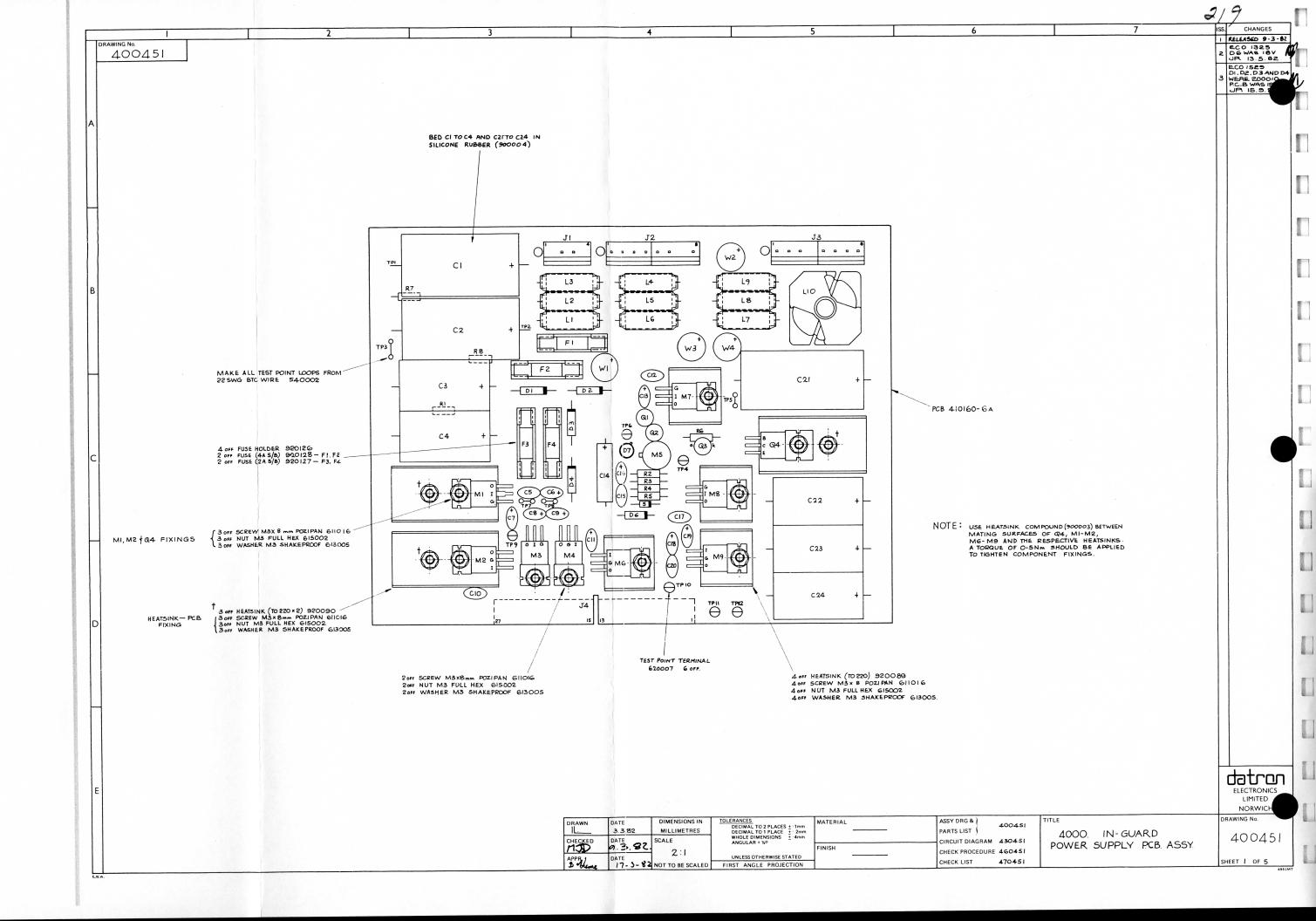

In the main, the circuits are located on the Power Amplifier (DC) Assembly. The Error Amplifier, VCA drive circuitry, sense attenuator, overvoltage and overcurrent detectors and output switching are located on the DC PCB Assembly. Some of these circuits are common to the Low Voltage DC functions.

#### 4.8.1 General (Fig. 4.33)

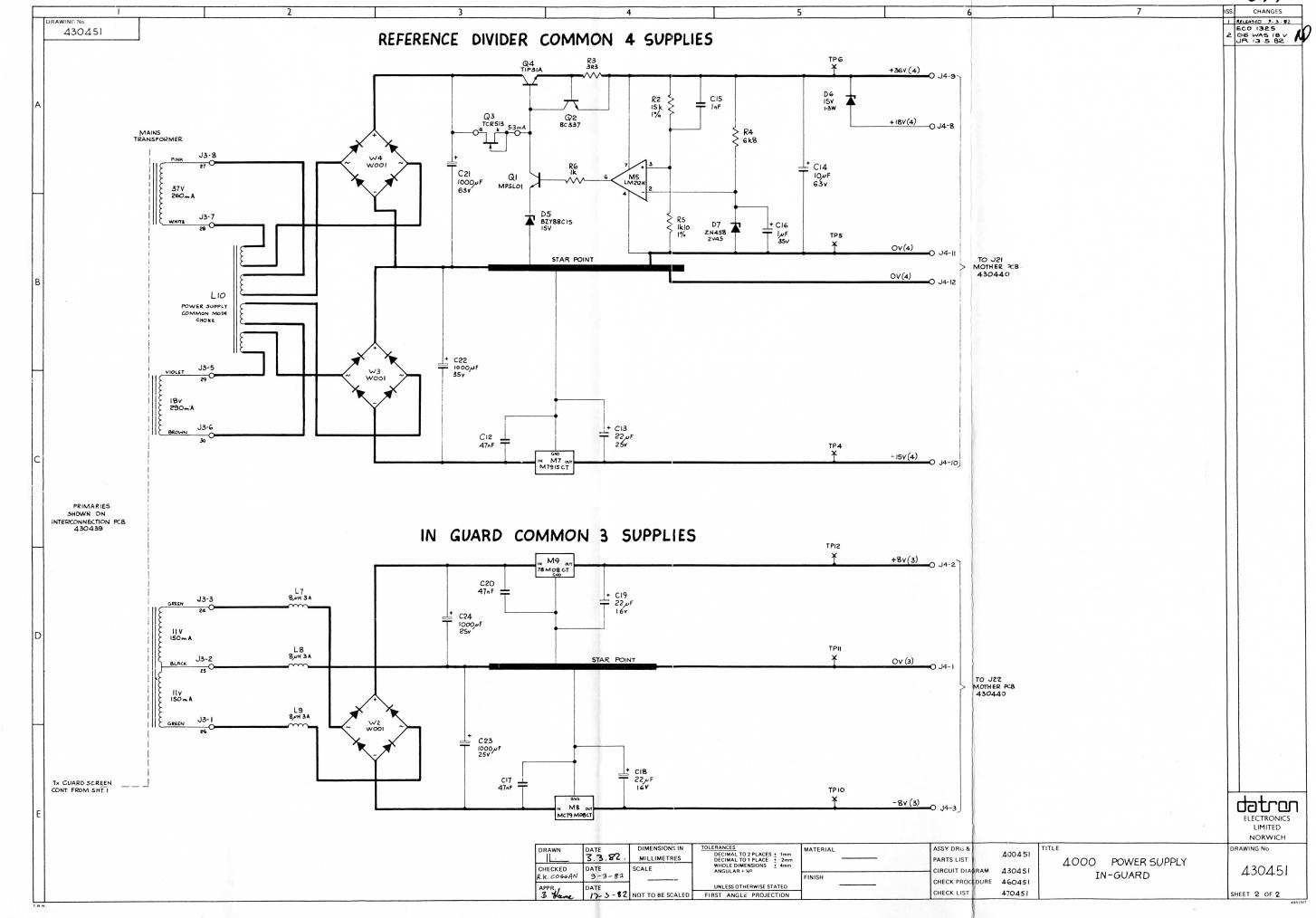

AC transformation is carried out at 16kHz, derived from M16 in the Analogue Interface 13-bit counter, and transferred into guard as a square wave through optocoupler M3 on the Reference Divider pcb.

The square wave is filtered to provide a 16kHz sine wave. The filter has high selectivity at 16kHz to eliminate harmonic distortion.

The sine wave amplitude is controlled by the DC loop-error drive in a Voltage-Controlled Amplifier (VCA), and power-amplified to drive the step-up transformer primary. Range switching is achieved by changing the step-up ratio, both primary windings being connected in series on the 100V Range.

A constant-current source acts as a shunt to sustain the current drawn from the high-voltage secondary winding through the bridge rectifier, and polarity is switched with respect to common-2 via the LC-filtered ± 15V common-2 supplies. Positive polarity output is referred to -15V at zero output, to provide an overlap with Negative polarity output referred to +15V. The overlap allows digital calibration constants to be used to align zero voltage output in both polarities to the same calibrated zero.

The main output filter is placed in the output line. This is a low-pass filter with a high rejection at 16kHz, reducing the ripple voltage to within specification limits.

Shutdown of the high voltage power-circuitry occurs when an output current of 30 — 40mA is detected in the Current Limit circuitry. The output voltage is fed

out through the Range switch on the DC pcb, where it is subject to Remote Sense and Output On/Off switching and over voltage detection, before being passed to the I+terminal by the same route as for low voltage ranges. The external current is sunk into common-2 via the overcurrent detector, which warns the control processor when the output current exceeds approximately 28.5mA. On 100V and 1000V ranges the processor will switch the output off on receipt of the overcurrent signal from either the current limit circuit or the overcurrent detector.

The output voltage is sensed between the Hi and Lo terminals. Lo is referred to Sense attenuator Lo and DC Ref Lo. The Hi sense voltage is divided in the Sense Attenuators by 10 (100V Range) or 60 (1000V Range). The attenuated output is compared against DC Ref Hi in the Error Amplifier, and modifies its output to the 10V Buffer and VCA drive. The 10V Bootstrap, in addition to supplying the Error Amplifier, also buffers DC Ref Hi as reference for the VCA Drive circuit.

The error voltage between the buffered DC Ref Hi and the 10V buffer output is conditioned by the VCA drive to provide a suitable control signal for the VCA itself.

The Sense loop thus stabilises the High Voltage DC output to a value which on 100V range is 10 times the DC Ref voltage and on 1000V range is 60 times the DC Ref voltage. On 1000V range, the DC Ref voltage is scaled digitally so that Full Scale of 20V corresponds to 1200V on the OUTPUT display and at the output terminals.

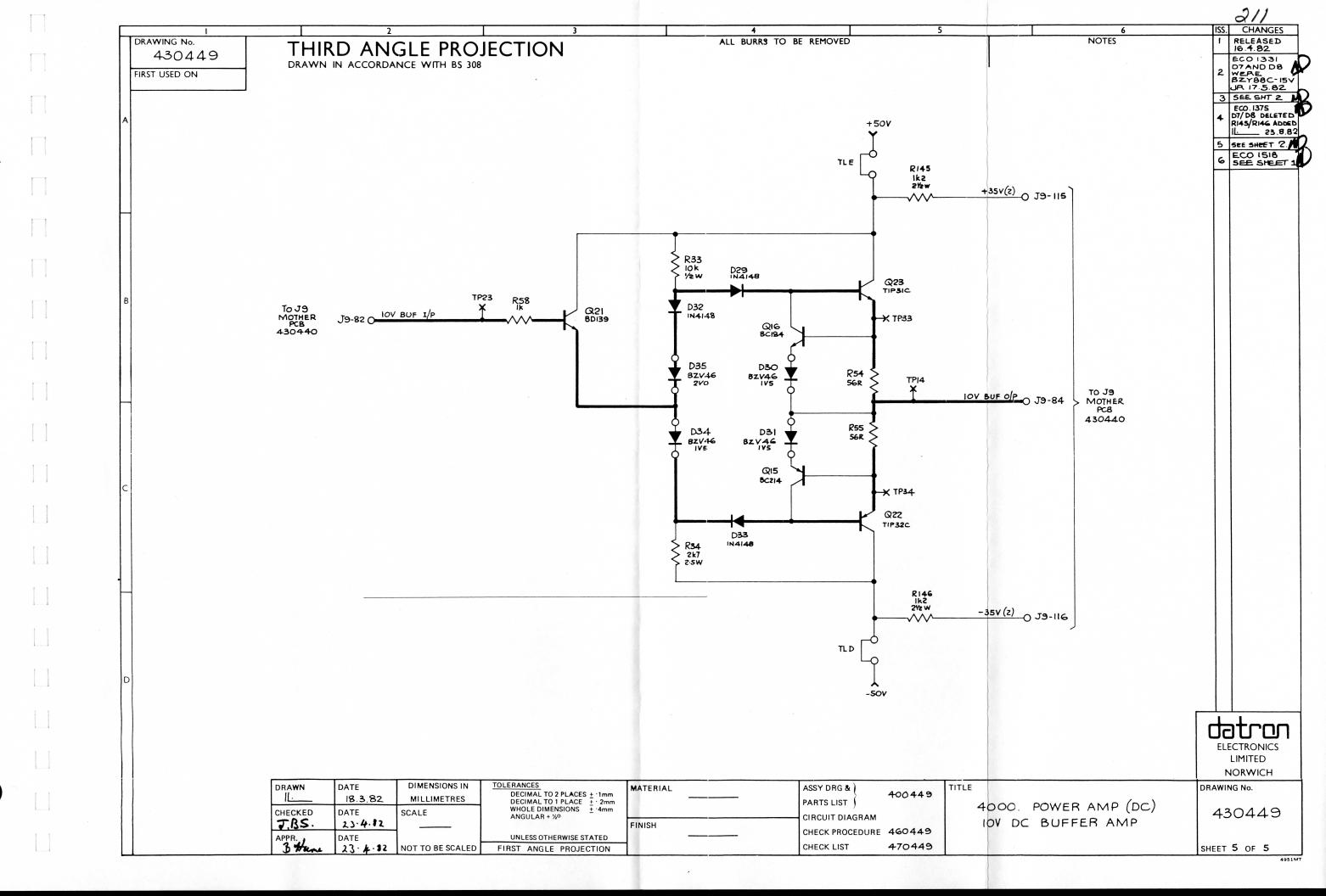

# 4.8.2 Square-Sine Filter (Circuit Diagram No. 430449 Sheet 4)

The 13-bit counter in the Analogue Interface generates 16kHz at M16-14 (Circuit Diagram 430443 Sheet 2), which is transferred into guard through optoisolator M3 on the Reference Divider (Circuit Diagram 430444 Sheet 4). The 16kHz square wave, switching between logic-1 = 0V and logic-0 = -15V, enters the Power Amplifier pcb on J9-86.

M8 buffers apply the full 15V p-p squarewave to coupling capacitors C38 and C39. M3 input circuit is a 16kHz series-tuned filter. This, together with M3 active low-pass filter, produces a sine wave at TP15 of 0.6V to 0.8V pk-to-pk amplitude and approx 5% distortion.

# 4.8.3 Voltage Controlled Amplifier

The DC loop error voltage is applied from the VCA drive to Q26 to control the input resistance to M4. Q26 and R66 are matched to standardise the gain range (mid-range gain of approx 0.5). A manual gain adjustment

(Q28, R68, R65) is provided for test purposes.

M4 output is AC-coupled as drive to the power amplifier.

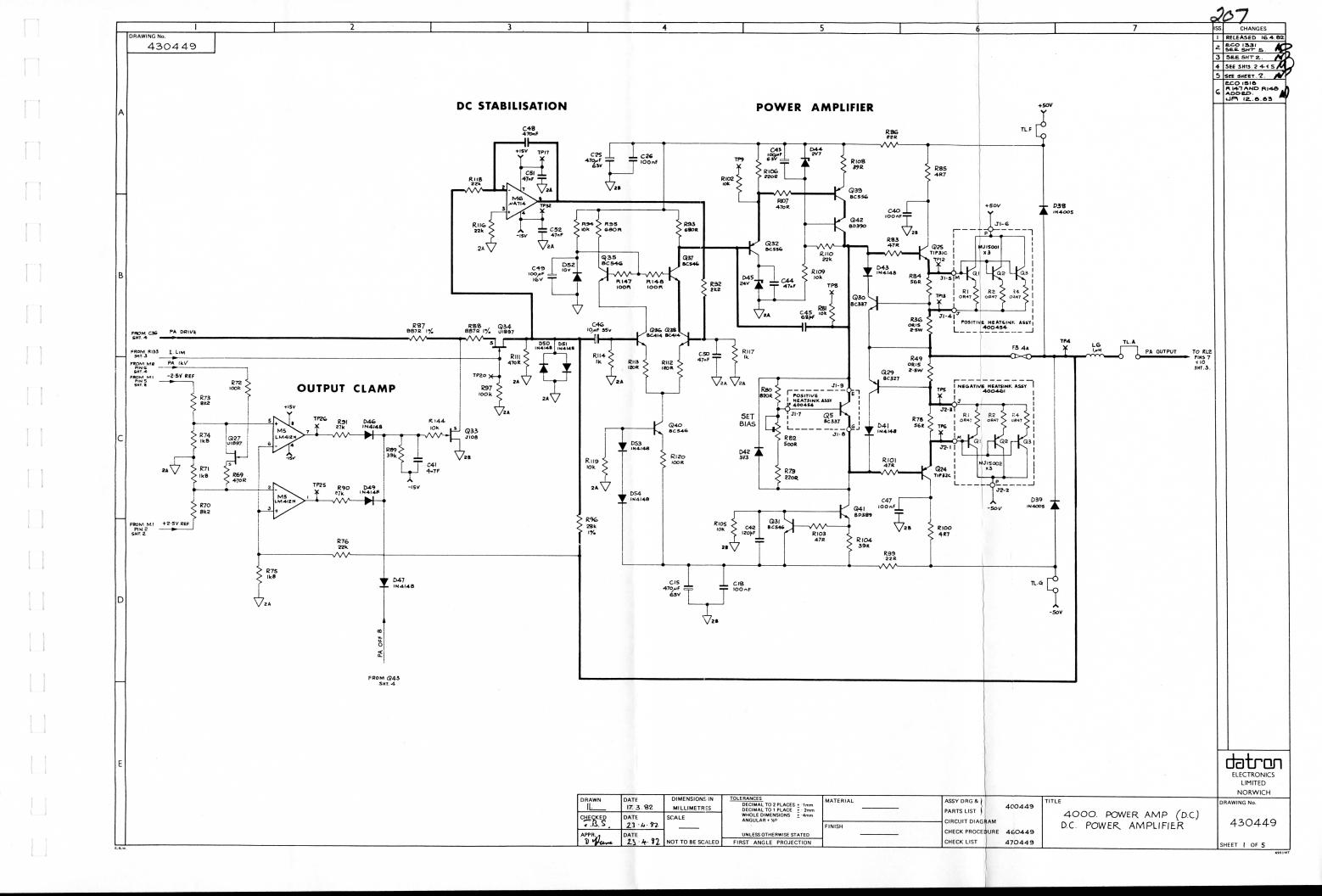

# 4.8.4 Output Clamp (Circuit Diagram No. 430449 Sheet 1)

When the CPU switches the Power Amplifier on or off in 100V or 1000V ranges, it controls the 16kHz drive to the high voltage power amplifier. For both ranges, a signal PA OFF is provided at M15 pin 5 on the Reference Divider (Circuit Diagram No. 430444 Sheet 4) which is buffered by M8/Q43 on the Power Amplifier (Circuit Diagram No. 430449 Sheet 4), as PA OFF B signal.

With output off, the Output Clamp circuit is allowed to operate by D47 reverse bias. The  $\pm$  2.5V Reference from the 50V Power Supply is divided by R70/71/73/74 to provide  $\pm$  0.45V bias for M5 on 100V range. Q27 conducts only when the CPU has selected 1000V range, reducing M5 bias to  $\pm$  0.025V.

Example of clamp action

On 100V range, the bias on M5 pin 5 is -0.45V. If the PA output voltage is less negative than -5.95 volts, M5 pin 6 is more positive than pin 5 and D46 is nonconducting due to -15V at TP26. If the PA output is more negative than -5.95V, M5 pin 6 is more negative

than -0.45V, TP26 rises to cause D46 conduction and Q33 starts to conduct. The 16kHz drive to the PA is reduced due to the extra volts drop across R87, which limits the negative half-cycles of the PA output at approx.

In similar fashion, D49 conducts on positive output half-cycles to start limiting at +6V and on 1000V range, positive and negative half-cycles start limiting at approx. 0.3V.

This limiting action ensures that when the 4000 output is off, the PA output to the step-up transformer is limited to less than 10V peak on 100V range, and less than 3V peak on 1000V range.

As the PA OFF B input is low (-15V) when output is on in 100V or 1000V range, Q33 is pinched off, and the PA output is not clamped.

Q34 in the PA drive line is pinched-off by  $\overline{\text{L IM}}$  at -15V when the output Current Limit is activated (see Section 4.8.9).

# 4.8.5 Power Amplifier (Circuit Diagram No. 430449 Sheet 1)

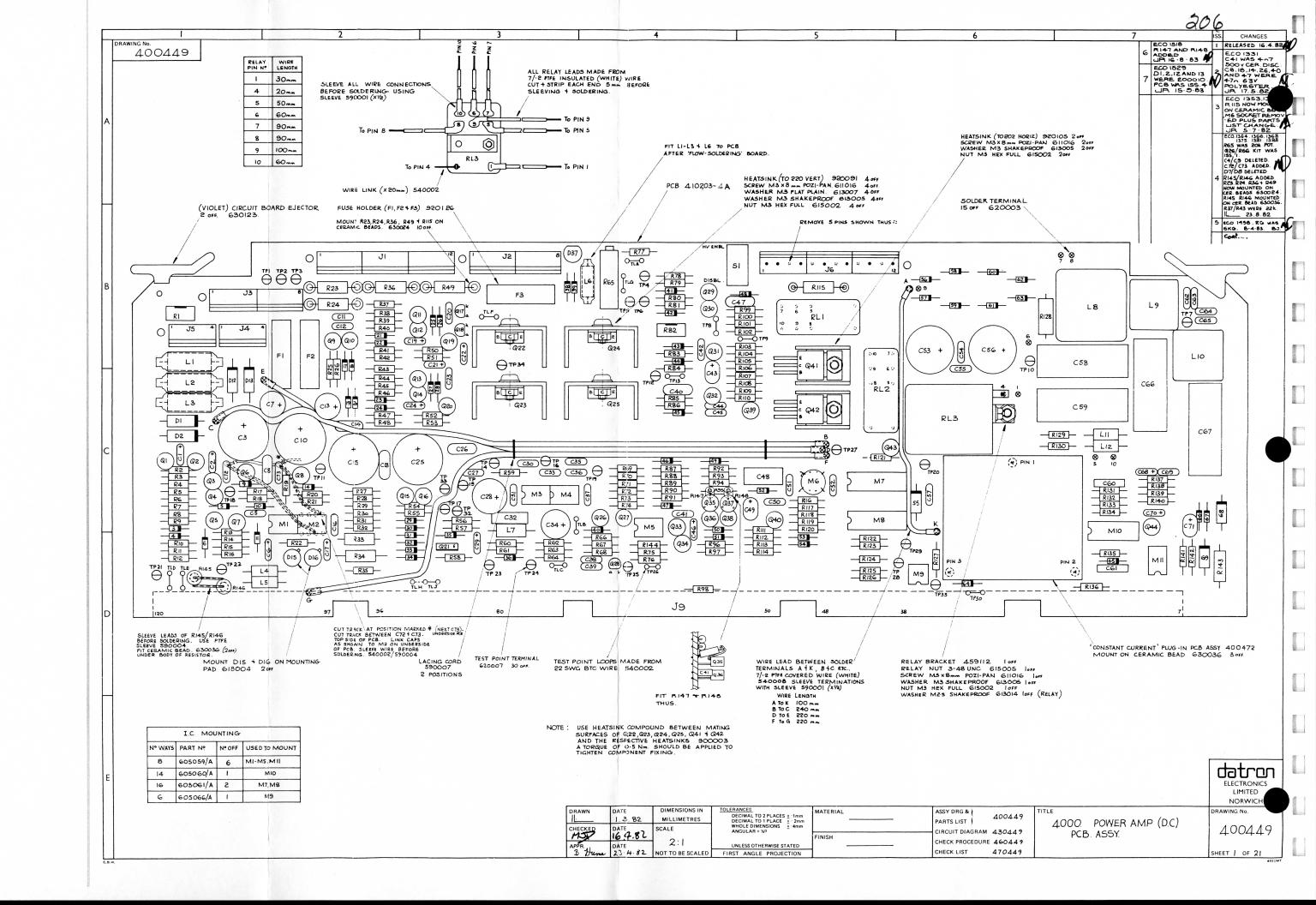

The Power Amplifier deals with AC and DC separately. The overall purpose is to stabilize the mean output level at zero DC, whilst driving the step-up transformer with a large enough voltage swing to provide DC output voltages at the I+ terminal of 200V (100V range) and 1200V (1kV range). The power delivered to the transformer is sufficient to provide output loading for each range of 25mA, with a little in reserve.

C46 is the only DC blocking capacitor in the whole amplifier, so Q36 and Q35 form the AC preamplifier as one half of an emitter-coupled cascode amplifier with Q38 and Q37. Q40 provides the constant current which reduces common mode disturbances at Q37 collector.

The DC path through the power amplifier passes through M6 and the Q38/Q37 half of the long-tailed pair. The DC loop is self-zeroing at input and output due to its

three inversions in M6, Q38 and Q39. M6 is converted into an integrator by C48, so acts as a low-pass filter with unity gain at around 15Hz. Q32, Q39 and Q42 shift the DC level and provide high driver gain into the output Darlington amplifier. Q5 establishes the correct bias on Q24 to reduce crossover distortion, compensating four output  $V_{be}$  variations with temperature by being in thermal contact with the positive heat sink. Q41 provides constant current pull-down for the driver stage.

Q29 and Q30 current limiters prevent damage in the event of an output short circuit.

The d.c. output level is therefore referred to common-2 by R116 at M6 non-inverting input.

The AC loop also includes three inversions, so feedback controls both AC and DC to R96/(R87 + R88).

# 4.8.6 High Voltage Transformer and Rectifier (Circuit Diagram No. 430449 Sheet 3)

Relay RL2 is energised permanently when the watchdog BARK signal is low (-15V). The 16kHz PA output passes via RL2 pins 7 and 10 to RL1 contacts and to the High Voltage transformer.

When the watchdog BARK signal goes high (OV), the drive is removed and the transformer primary is shorted to common-2 as RL2 is de-energised.

RL1 is only energised on 1000V range with switch S1 ON (indicated by LED D37 lit on the PA (DC) Assembly. On 100V range it is set as shown on the circuit drawing, selecting both primaries in series for a step-up ratio of 9.2. For 1000V range, RL1 connects the PA

output to only one primary winding (J6-1 to J6-4), a step up ratio of 49.2.

These ratios generate secondary voltage outputs sufficiently large to provide DC outputs from the instrument of 200V (100V range) and 1200V (1000V range).

The rectifier bridge uses to series diodes in each arm. Each diode is current-rated at 1A, with a p.i.v. of  $1.5 \, \text{kV}$ .

N.B. The transformer secondary, and bridge rectifier are not directly referred to any common. This allows the rectifier output to float so that it may be used for either polarity.

## 4.8.7 Constant-Current Source and Overvoltage Detector Assembly (400472)

#### 4.8.7.1 Constant-Current Source

Q1-12 form a series Darlington chain, connected across the bridge rectifier output as a constant-current source, having two functions:

- (1) It provides a discharge path which is a "constant" current at all output voltages, of approx 1.2mA above 120V, rising to 7mA at 0V.

- (2) It maintains diode bridge D56-D63 conduction in no-load conditions. At higher voltages, D14-D17 limit Q11 base voltage to +2.4V, limiting the series current in R11 to 1.2mA, with Q13 pinched off. At lower voltages Q13 conducts, shunting R11 with 170-180  $\Omega$  (R10 plus Q13 'On' resistance which falls to approx 125 $\Omega$ ), and increasing the discharge current to approx 7mA.

Note that the minimum voltage applied across the constantcurrent source is 15V. Even at zero output voltage and current, the diode bridge generates 15V to back off the positive or negative 15V connected to RL3.

## 4.8.7.2 Overvoltage Detection

Zener diodes D1 - D13 form a series chain across the High Voltage supply. When the voltage exceeds 1440V this chain conducts, lifting D13 cathode and driving optoisolator M9. M9 emitter rises, and provides a "Reset" logic-1 (0V) input to M10-10, resulting in a logic-0 (-15V) output from M10 - 13.

The operation of M10 and subsequent action is described in section 4.8.9.

## 4.8.8 Polarity Switching and Ouput Filter

Double-pole relay RL3 performs the polarity-reversal. With RL3 de-energised as shown the output filter is connected to rectifier negative, and +15V Common-2 supply is connected to rectifier positive. During zero calibration, the +15V is backed off to give a true zero output by an output from the rectifier.

When RL3 is energised by the POSITIVE signal from the serial data-link parallel output registers at logic-1 (0V), the output filter is connected to the rectifier positive rail, referred to -15V common-2 supply. Again, this -15V is backed off to zero when calibrated.

Filtering is accomplished in three stages:

- L8, R128, C58, C59 2-pole filter attenuates 16kHz by approx 30dB and 32kHz by approx 42dB.

- (2) L9, L10 and associated capacitors form a 5-pole filter with elliptic characteristics, attenuating by at least 60dB above 16kHz.

- (3) The final stage is formed by C1 on the Mother PCB (Refer to Circuit Diagram 430440 Sheet 1) and the output resistance (approx  $500\Omega$ ) of the high voltage circuitry on the Power Amplifier PCB (Circuit Diagram 430449 sheet 3). This gives attenuations of approx. 30dB at 16kHz and 36dB at 32kHz.

# 4.8.9 High Voltage Output Current Limit Detector

Section 4.7.10 describes over-current sensing circuitry on the DC pcb Assembly, which provides LIM ST 1 signal when the output current exceeds approximately 28.5mA. It also generates HV STATUS signal when the output voltage exceeds 130V.

In addition to these signals; the two high voltage ranges are protected against over-voltage (see Section 4.8.7.2) and over-current on the Power Amplifier pcb itself.

# 4.8.9.1 Over-Current Detector

An output current of approx. 35mA will cause the output to be shutdown. Opto-isolator M11 is set to respond to a threshold level of approximately 5.25V across R143, causing conduction between pins 6 and 5.

# 4.8.9.2 Protection Logic

On Power-up, M10 settles into its stable state with Q (pin 2) and Q (pin 13) both at logic-1 (0V). Both sections have set and reset pins at logic-0 (-15V), and PA OFF B signal at logic-1. Q44 is cut off, as also are M9 and M11 output emitter-followers, holding M10 reset (pin 10) at -15V (logic-0).

By selecting Output On in 100 or 1000V range, PA OFF B goes to logic-0. M10 is not clocked by the negative edge, but Q44 is turned on, providing the supply to M11, which remains cut-off unless overcurrent is detected.

When an over-current is detected M11 Output stage conducts, lifting pin 5 from -15V to approximately -1V (logic-1 on M10 pin 10). The Q output of M10 (pin 13) is forced into reset state. HI I ST and I LIM fall to logic-0 (-15V).

The I LIM signal switches off Q34 at the input to the Power Amplifier (sheet 1), removing the 16kHz drive, and reducing the output voltage to zero, thus providing instantaneous shut-down. HIIST signal is returned

via the serial data link to the CPU, which presents "Error OL" on the MODE display and carries out the normal Output OFF routine, disconnecting the external load, reducing R143 current to zero, hence cutting off M11 Output stage. M10 pin 10 reverts to Logic-0, sensitising the flip-flop to any positive clock-edge on pin 11.

At the same time, the PA OFF B signal rises to Logic-1, cutting off Q44, and clocking the logic-1 on M10 pin 5 through to pin 1 (Q) so Q (pin 2) goes to logic-0.

Pin 4 rises on time constant C61 R135, and the monostable times out after 8mS by forcing Reset state. Pin 1 falls to logic-0 and rapidly sets pin 4 to logic-0, sensitising the monostable to any positive clock-edge on pin 3. Meanwhile, pin 2 has reverted to logic-1, clocking the logic-1 on pin 9 through to pin 13, and returning HIIST and ILIM signals to their non-active logic-1 state. The detector remains in this state until output is again switched ON on 100V or 1000V range. The "Error OL" presentation is retained until the user makes a further Front Panel or Remote selection.

If the instrument is operating normally with Output ON in 100V or 1000V range, and Output OFF is selected, M10 monostable pin 2 again delivers its negative 8mS pulse to Pin 11 and the logic-1 at pin 9 is clocked in. But as pin 13 is already at logic-1 this does not disturb the HIIST and ILIM signals.

# 4.8.10 Output Switching, Sense Attenuator and Guard (Circuit Diagram No. 340445)

The high voltage output is taken from the Power Amplifier to be Range-switched on the DC pcb (RL2 on Circuit Diagram No. 430445 Sheet 1). On 100V or 1000V the selected PHi voltage is Remote/Local and Output ON/OFF switched before passing to the instrument output I+ terminal. Any output current drawn by the external load is returned via the I- terminal and the over-current sensor to common-2 (Refer to section 4.7.10).

The external load Lo is connected directly to the Lo terminal and hence to common-1 in the DC pcb. Load Hi is returned via the Hi terminal to the head of a high-voltage attenuator (R10, R27, R48, R66, R89, R96, R99 of circuit drawing 430445 Sheet 1), which is also referred to common-1.

The attenuator is range-switched by RL3 between 1000V and 100V ranges. On 1000V range the attenuation is 60:1, reducing Full Scale load voltage of 1200V to 20V for comparison against the DC Ref Hi voltage. On 100V range; R89, R96 and R99 divide the voltage by 10. The attenuator and DC Ref Lo are both returned to common-1.

To guard the necessarily high-impedance attenuator each connection between resistors is shielded. The potential divider R8, R9, R25, R26, R46, R47, R64, R65, R88, R95 and R98 connected between the Power Amplifier output voltage and common-2 maintains each screen at the potential of the connection it is shielding, to reduce leakage. RL3 shorts part of the divider on 100V Range to equalise potentials.

## 4.8.10.1 Model 4000A - 100V/1000V Precision Sense Attenuator (Layout Drawing 400445 Sheet 1 and Circuit Diagram 430445 Sheet 1)

In the Model 4000A, the DC PCB is fitted with an uprated 100V/1000V attenuator, to hold the specification over a wider temperature range than the 4000:

- (1) R10, R27, R46 and R48 (1M25) are replaced by five 1MO resistors.

- (2) R89, R96 and R99 are replaced by one 900k/100k unit.

The whole attenuator set is referenced as part no. 090057/A.

# 4.8.11 VCA Drive and Control

The attenuated sense signal is applied to the inverting input of the Error Amplifier via RL11-10 and RL9-14. This bootstrapped, high-gain amplifier compares the sense signal with DC Ref Hi. When both are equal: the output from the 10V buffer at TP5 star-point, the bootstrap common BS2, DC Ref Hi and the sense signal are all at the same level. Therefore the differential input to M12 (VCA error amplifier) is zero at R42/R43.

The gain from M12-1 to I+ terminal is approx. x2000 on the 1000V Range and approx. x400 on the 100V Range. Components R97, C33 at the Error Amplifier input, and R33, C16 on M11 provide frequency compensation for the overall loop.

The second M12 stage acts as a polarity switch. With OUTPUT ON + LED lit, the POSITIVE control signal is at logic-1 (0V). Q2 conducts setting M12 non-inverting

input (pin 5) to zero volts, so the amplifier inverts the pin 6 input. If OUTPUT ON- LED is lit the POSITIVE signal is at logic-0 (-15V) cutting off Q2, M12 pin 5 follows the pin 1 voltage, so the amplifier acts as a voltage follower.

The polarity switching is necessary to adapt the bi-polar action of the error amplifier to the unipolar sensitivity of the Voltage Controlled Amplifier.

#### 4.8.11.1 VCA Action

If a user increases a positive OUTPUT display value, the positive DC REF Hi voltage will increase, (a demand to increase a positive output voltage). The polarity switch inverts the positive input from M12-1. So M12-7 feeds a negative output to M11. This is inverted and fed, via the Mother pcb, to D36 on the Power Amplifier Assembly as an error signal (Circuit Diagram No. 430449 Sheet 4).

On the Power Amplifier Assembly; as the VCA control signal becomes more positive the gain of M4 between TP15 and TP19 is increased, thus increasing the output at I+. The attenuated sense voltage rises to equallise the differential inputs to the error amplifier, and the I+ voltage stabilises at its new value.

M4 has a maximum gain of x12 when TP24 is at 0V and a minimum gain of x0.01 when TP24 is at -12V or lower.

## 4.8.12 Decoding Logic (Circuit Diagram 430499 Sheet 4)

# 4.8.12.1 "PA OFF"

The PA OFF signal is originated by the CPU and latched at M15 Q2 (pin 5) Serial/Parallel data converter on the Reference Divider pcb (Circuit Diagram No. 430444 Sheet 4); as logic-1 (0V) for PA OFF, and logic-0 (-15V) to provide the DC 100V/1kV drive from the Power Amplifier Assembly. Under normal use test link TLJ is made, but for test purposes link TLJ can be unsoldered, and TLH made. PA OFF is buffered by M8 and Q43 as

PA OFF B, which has two functions:

- (1) At logic-1 it allows the output clamp to operate but at logic-0 removes the clamp from the PA input. (Refer to Section 4.8.4).

- (2) A 0-1 transition by PA OFFB clocks the over-voltage and over-current detector M10 to reset. (Refer to Section 4.8.9).

#### 4.8.12.2 "POSITIVE"

The polarity of 100V and 1000V Range outputs is determined by the CPU. In addition to changing the polarity of the DC Ref Hi signal fed from the Reference Divider into the DC Error Amplifier, the POSITIVE signal performs polarity switching in the VCA drive (refer to sections 4.6.11 and 4.8.11). On the Power Amplifier pcb it energises RL3 when at logic-1 (0V), connecting the

positive rectified voltage from the HV transformer to the Output Filter (Refer to Section 4.8.8). At logic-0 (-15V), RL3 is de-energised, and the drive to the output filter is negative.

The POSITIVE signal is latched at M31 Q1 (pin 4) on the Reference Divider pcb serial/parallel data converter. (Refer to Section 4.5.5).

#### 4.8.12.3 "HV ENBL"

On 1000V Range, HV ENBL signal is at logic-1 (0V) to energise RL1, whose contacts apply the P.A. output to the single primary winding (J6-1 to J6-4) of the high voltage transformer. (Refer to Section 4.8.6). The Output Clamp circuit requires reduced reference voltages on this

range, so HV ENBL is buffered as PA 1kV signal and applied to Q27 for this purpose (Refer to Section 4.8.4). Switch S1 on the PA pcb can be set to disable the 1kV Range output by releasing RL1 and shorting the 16kHz drive to the PA. When the switch is in the "Enable" position, LED D37 lights as a visible warning.

# 4.8.12.4 "DC ST"

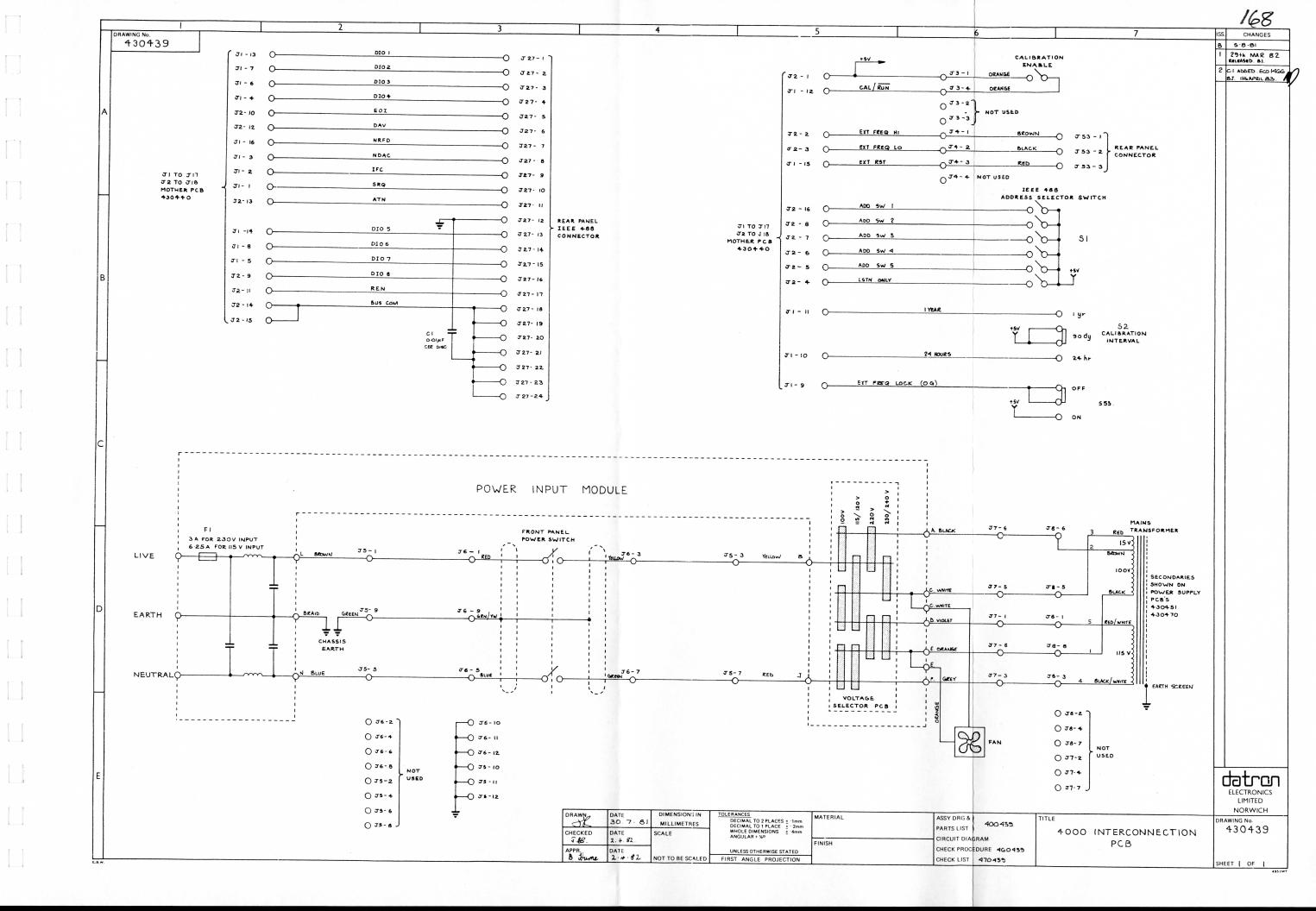

The DC ST line returns to the Reference Divider pcb, (Circuit Diagram No. 430444 Sheet 4), and is connected there to M21 pin 5. An identical line from the DC pcb also connects to M21 pin 5. Each line is pulled down to -15V through a 15k $\Omega$  resistor. When both lines are correctly connected, M21 pin 7 (TP17) is at logic-0 (-15V), input

to M22-13 Parallel/Serial data converter. The DC status bit is read out of the SSDA "Receive" register by the CPU on each data transfer. If at logic-0, DC function may be selected by a user. If at logic-1, the CPU inhibits selection. The same method is used for AC ST, but as AC is not fitted in the 4000, M22-4 will always be at logic-1.

#### 4.8.12.5 "BARK"

The Safety Monitor (Watchdog) produces the BARK signal when the CPU or SSDA is functioning incorrectly, and the SAFETY message is presented on the MODE display. The BARK signal is normally at logic-0 (-15V) so that RL2 is energised, applying the PA output

to the HV transformer. When a failure trips the watchdog, BARK goes to logic-1, de-energising RL2, which disconnects the PA output and shorts the HV primary to common-2, reducing the 4000 output voltage to zero. (Refer to Section 4.5.6 for information on the Safety Monitor).

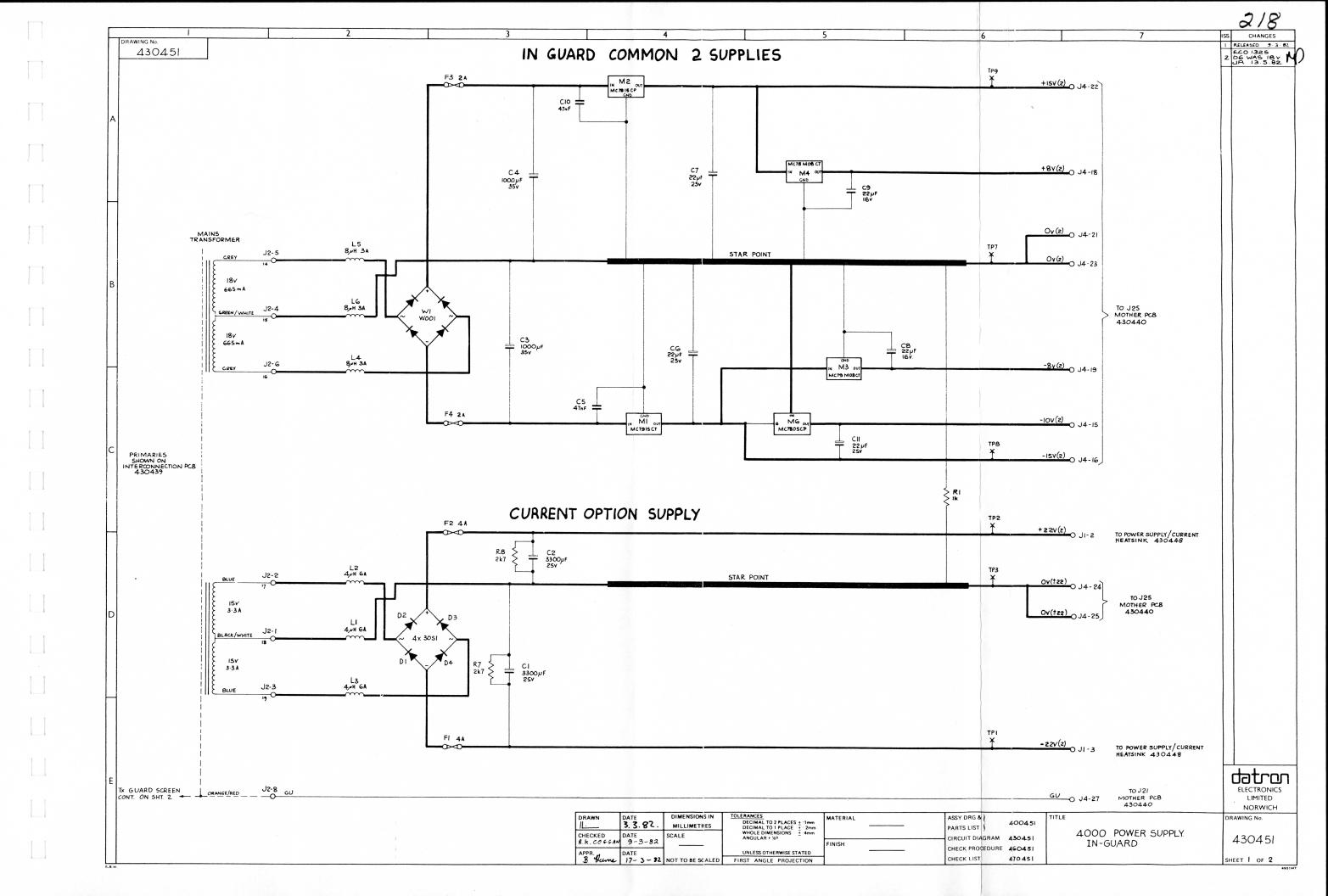

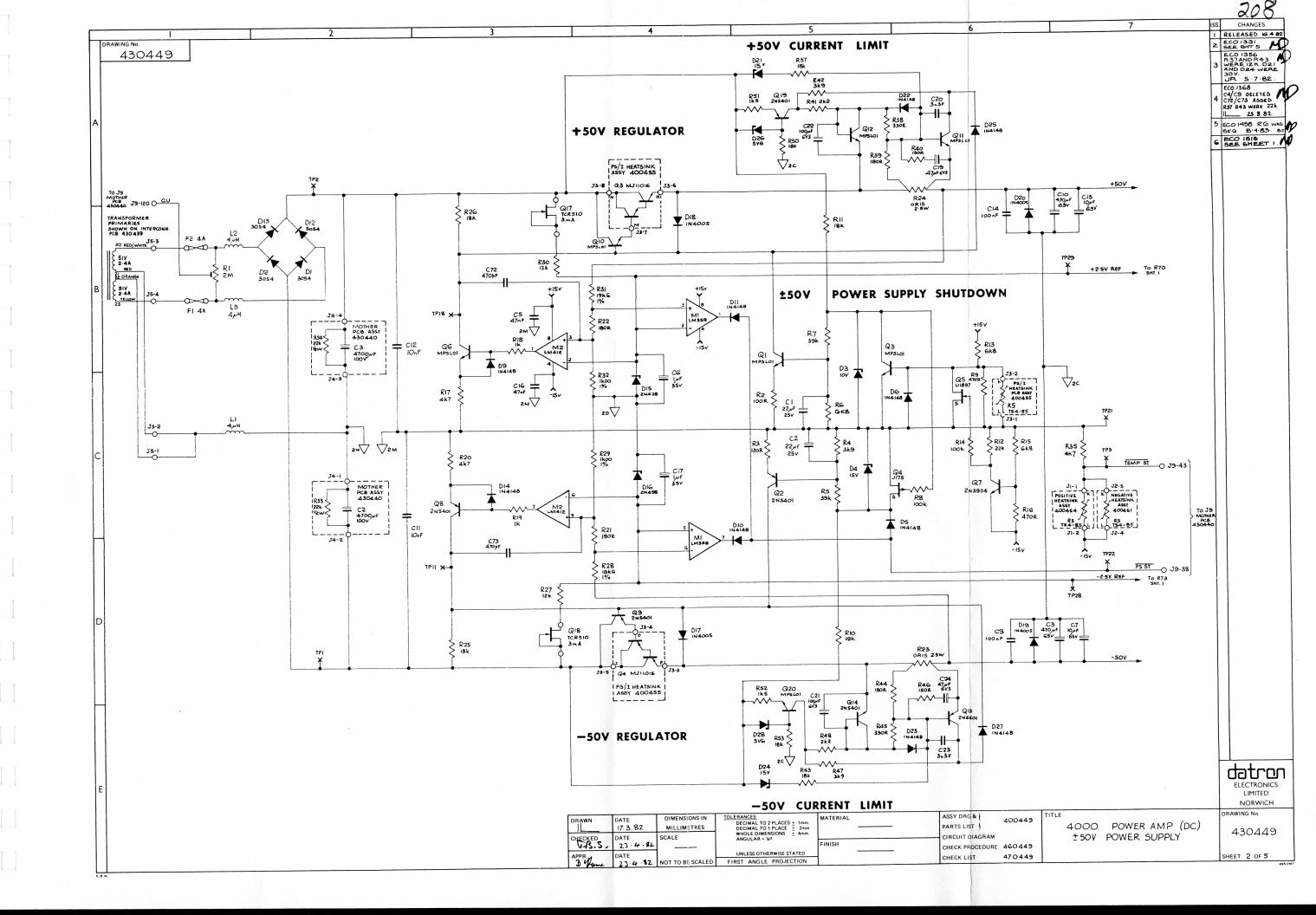

# 4.8.13 50V Power Supply (Circuit Drawing No. 430449 Sheet 2)

The power supply on the PA pcb provides  $\pm$  50 volts regulated power for the Power Amplifier. It incorporates "Foldback" current limiting and "excess input voltage" limiting for both polarities. Overheating of the positive or negative heatsink (PA Output stages) generates a  $\overline{\text{TEMP ST}}$  signal to the CPU via the serial data link. Overheating of the PS/I heatsink, failure of the  $\pm$  15V supply or  $\pm$  50V output undervoltage; generates a  $\overline{\text{PS ST}}$  signal to the CPU.

In both cases the CPU sets 4000 Output Off and displays a FAIL message:

FAIL 1 — TEMP ST at Logic-0 FAIL 7 — PS ST at Logic-0

When the power supply is operating normally, both signals are at logic-1. The logic levels for these signals at TP3 and TP22 are Logic-0 = -15V, Logic-1 = 0V (common-2).

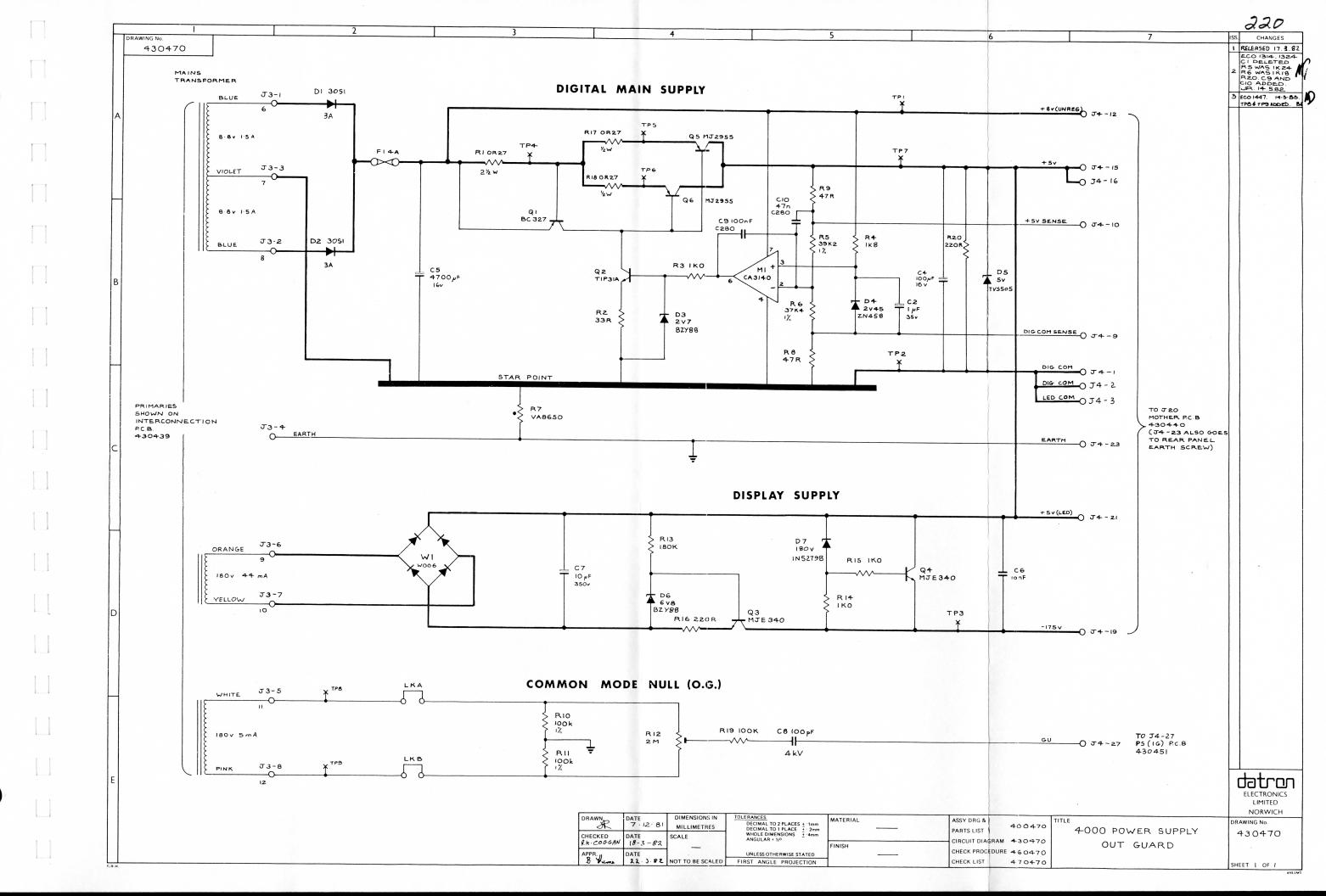

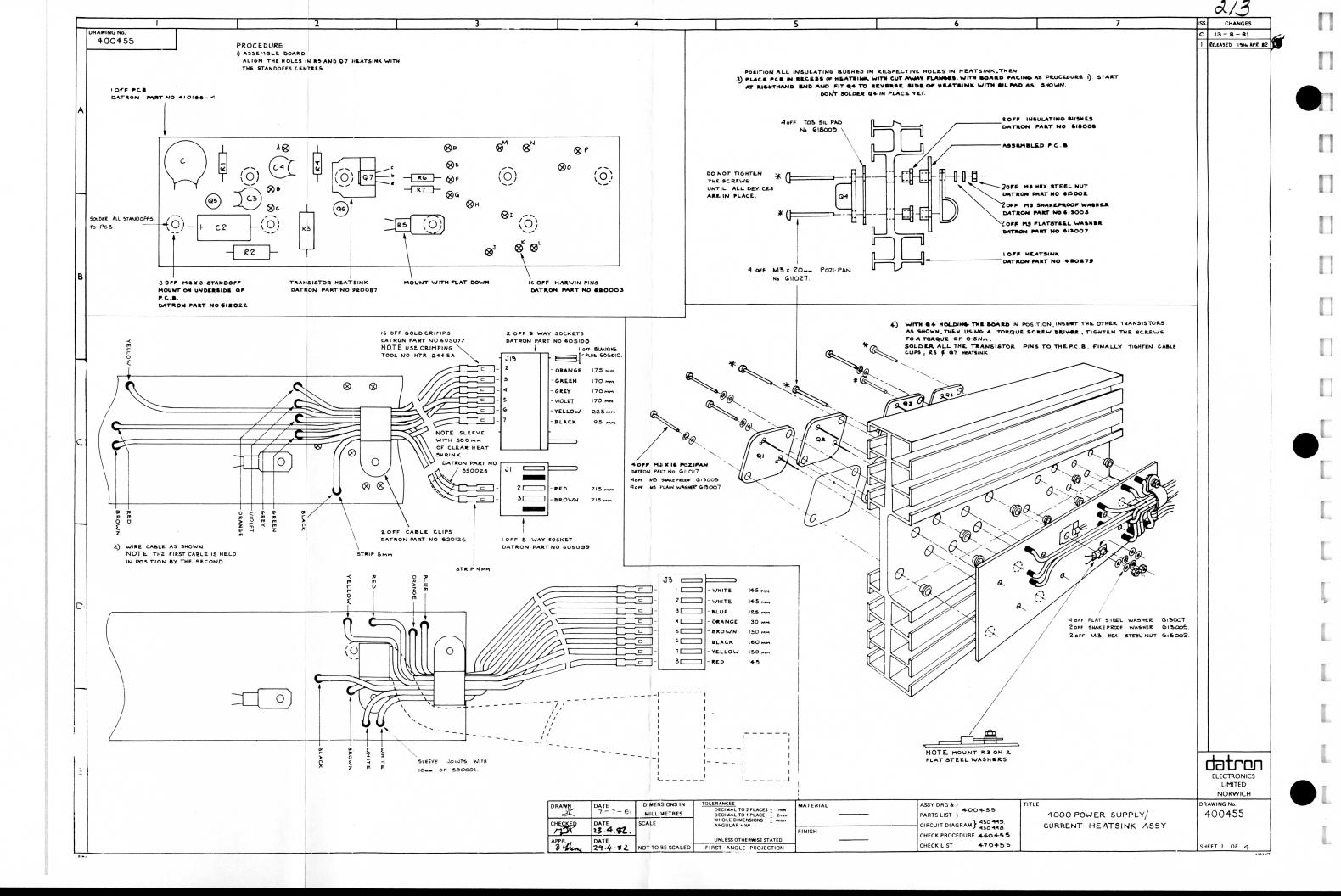

# 4.8.13.1 50V Supply Regulation

Power is input from the Line Transformer secondaries, both fused at 4A. R1 provides an adjustment to eliminate line frequency hum on the guard shields, in conjunction with R52/C4 on the Mother pcb. (For adjustment procedure refer to Section 5.7).

The secondaries are referred to common-2, and the rectified outputs are smoothed by reservoir capacitors C2 and C3 at the rear of the Mother pcb.

The series regulation elements Q3 and Q4 are mounted on the PS/I heatsink assembly. These Darlingtons are driven by Q10 and Q9.

# NB. The following description refers only to the positive 50 Volt supply. The action in the negative supply is similar.

Q17 generates constant current of 3mA to activate D15 2.45V Zener diode. The +2.45V provides the positive reference supply for the Output Clamp circuit (Refer to Section 4.8.4.). It is also the reference for comparator M2-2. The output voltage is sensed on the +50V rail and divided down to Reference potential at M2-3. M2-1 output drives Q6 whose collector voltage at TP18 controls Q3 (PS/I Heatsink) conduction via Q10. If the +50V rail voltage falls due to loading, TP18 voltage rises, increasing the conduction of Q3 to restore the output rail voltage.

# 4.8.13.2 50V Current Limit (Positive 50V only described)

R24 is the series current detector, which drops 0.4V at 2.7A. Q19 generates a constant current of approximately 3mA which can be shared between Q12 and Q11. Q12 is saturated, generating approximately 200mV across R39. With little or no load current passing through R24, Q11 is off. When the current through R24 reaches approximately 2.7A, Q11 is switched on.

Q11 collector voltage rapidly falls below Q10 base voltage, D25 conducts and pulls Q10 base voltage

down, reducing Q3 conduction. This reduces the current through R24, but with Q11 fully conducting, it is held on by the voltage across R39. As a result, Q3 conduction can fall to approximately 500mA, and with the overload still present, the 50V rail voltage can fall to approximately 12.5V. This is a stable condition which persists until the 4000 is powered-down. As the voltage falls below +43V the under-voltage detector is activated (Refer to Section 4.8.13.3).

# 4.8.13.3 Under-Voltage Detection

With the Power Supply operating normally, the positive rail voltage lies between +49.5V and +52.2V. M1-3 is held at approximately +2.85V, and as the +2.45V Reference is connected to M1-2, D11 is reverse-biassed by +15V at M1-1. (D11 anode is normally pulled to 0V by AN2 on the Reference Divider pcb — Refer to Circuit Drawing No. 430444 Sheet 4).

When the rail voltage falls below approximately +43V, M1-3 falls below +2.45V, and M1-1 changes polarity to -15V, forward-biassing D11, and setting PS ST to logic-0. This is detected by the CPU, which presents FAIL 7 on the MODE display and sets 4000 Output OFF.

# 4.8.13.4 50V Power Supply Shutdown

At normal operating temperatures, the PS/I heatsink thermal detector has high resistance (approximately 100k $\Omega$ ). Q3 base is biassed by approximately +1V from the junction of R13/R9, so Q3 is saturated, holding approximately 150mV across R7 — R6, cutting Q1 off. The same 150mV holds p-channel FET Q4 On, which in turns holds Q2 cut off. D5 is unbiassed so  $\overline{\text{PS ST}}$  is at logic-1 (0V).

If either the +15V or -15V supply fails, the voltage at Q3 base falls and cuts Q3 off. The clamp on Q1 base is removed, and it draws collector-current through

R26, turning off the conduction in Q3 (PS/I heatsink). In the negative supply, Q4 is cut off, and Q2 turns off Q4 (PS/I heatsink) conduction. D5 is forward-biassed by -15V from the unregulated supply, clamped by D4, setting PS ST to logic-0 (-15V).

If the PS/I heatsink overheats, the temperature is detected by R3 (NTC thermistor). R3 resistance falls from  $100 k\Omega$  to  $100\Omega$  (approximately) as its temperature rises from  $80^{\circ}\text{C}$  to  $90^{\circ}\text{C}$ , reducing Q3  $V_{be}$  to approximately 200 mV. Q3 cut-off initiates the power supply shutdown as for loss of  $\pm 15 \text{V}$  supply.

## 4.8.13.5 PA Overheating

The Positive and Negative Heat Sink assemblies house the Power Amplifier output transistors. Each assembly is sensed by a NTC thermistor. These are connected in parallel, in series with R35 across the -15V supply. If

either heatsink overheats, the  $\overline{\text{TEMP}}$  ST signal changes from logic-1 to logic-0, the CPU presents FAIL 1 on the MODE display, and turns the 4000 Output OFF.