##

# GLT725608/08L

Ultra High Performance 32K x 8 Bit CMOS Static RAM

## FEATURES

- .....

- ◆ 32K x 8-bit organization

- ◆ Very high speed -10,12,15, 20 ns.

- Low standby power

- Maximum 100 µA for GLT725608L

- GLT725608L also provides minimum 2 V data retention.

- Fully static operation

## **GENERAL DESCRIPTION**

GLT725608 and GLT725608L are high performance 256K bit static random access memory organized as 32K by 8 bits and operate at a single 5 volt supply. Fabricated with G-Link Technology's very advanced CMOS sub-micron technology, GLT725608, GLT725608L offer a combination of features: very high speed and very low stand-by current. In addition, this device also supports easy mem-

- $\blacklozenge$  5 V ±10% power supply

- ♦ TTL compatible I/O

- ◆ Three state output

- ◆ Chip enable for simple memory expansion.

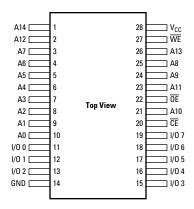

- Available in 28-Pin 600 mil plastic DIP, 300 mil plastic DIP, 300 mil SOJ, 28-Pin TSOP and 330 mil SOP Packages

ory expansion with an active LOW chip enable ( $\overline{CE}$ ) as well as an active LOW output enable ( $\overline{OE}$ ) and three state outputs.

The lower power version, GLT725608L also provides typical 1  $\mu A$  data retention current at minimum 2 V data retention voltage.

# GLT725608/08L

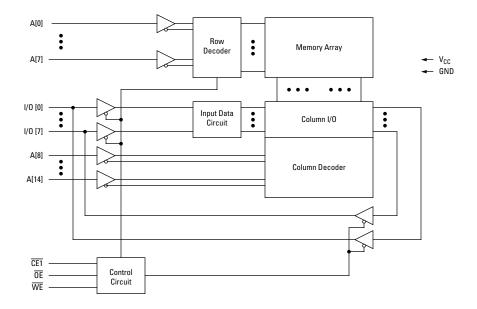

### **FUNCTIONAL BLOCK DIAGRAM**

#### **Signal Descriptions**

| Symbol          | Description                |

|-----------------|----------------------------|

| A[14:0]         | Address Inputs             |

| CE              | Chip Enable Input          |

| ŌĒ              | Output Enable Input        |

| WE              | Write Enable Input         |

| I/O[7:0]        | Data Input and Data Output |

| V <sub>CC</sub> | +5 V Power Supply          |

| GND             | Ground                     |

#### **Truth Table**

| Mode                      | WE | CE | ŌĒ | I/O Operation    | V <sub>CC</sub> Current                |

|---------------------------|----|----|----|------------------|----------------------------------------|

| Not Selected (Power Down) | Х  | Н  | Х  | High Z           | I <sub>CCSB</sub> , I <sub>CCSB1</sub> |

| Output Disabled           | Н  | L  | Н  | High Z           | I <sub>CC</sub>                        |

| Read                      | Н  | L  | L  | D <sub>OUT</sub> | I <sub>CC</sub>                        |

| Write                     | L  | L  | Х  | D <sub>IN</sub>  | I <sub>CC</sub>                        |

## **ELECTRICAL SPECIFICATIONS**

#### .....

## Absolute Maximum Ratings <sup>[1]</sup>

| Parameter                      | Ratings        | Unit |

|--------------------------------|----------------|------|

| Ambient Temperature Under Bias | -10°C to +80   | °C   |

| Storage Temperature (plastic)  | -55°C to +125  | °C   |

| Voltage Relative to GND        | -0.5 V to +7.0 | V    |

| Data Output Current            | 50             | mA   |

| Power Dissipation              | 1.0            | W    |

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATING may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### Capacitance ( $T_A = 25^{\circ}C$ ,f = 1.0 MHZ)

| Symbol           | Parameter                | Conditions            | Max. | Unit |  |

|------------------|--------------------------|-----------------------|------|------|--|

| CIN              | Input Capacitance        | V <sub>IN</sub> = 0 V | 8    | pF   |  |

| C <sub>I/O</sub> | Input/Output Capacitance | $V_{I/0} = 0 V$       | 10   | pF   |  |

### DC Characteristics <sup>[1]</sup>

|                    |                                                 |                                                                                                                             |      | -10 -12              |      | -15                  |      | -20                  |      |                      |      |

|--------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|----------------------|------|----------------------|------|----------------------|------|----------------------|------|

| Symbol             | Parameter                                       | Test Conditions                                                                                                             | Min  | Max                  | Min  | Max                  | Min  | Max                  | Min  | Max                  | Unit |

| V <sub>IL</sub>    | Guaranteed Input Low<br>Voltage <sup>[2]</sup>  |                                                                                                                             | -0.3 | +0.8                 | -0.3 | +0.8                 | -0.3 | +0.8                 | -0.3 | +0.8                 | V    |

| V <sub>IH</sub>    | Guaranteed Input High<br>Voltage <sup>[2]</sup> |                                                                                                                             | 2.2  | V <sub>CC</sub> +0.3 | V    |

| ILI                | Input Leakage Current                           | $V_{CC} = Max, V_{IN} = 0 V to V_{CC}$                                                                                      | -5   | 5                    | -5   | 5                    | -5   | 5                    | -5   | 5                    | μA   |

| I <sub>LO</sub>    | Output Leakage Current                          | $V_{CC} = Max, \overline{CE} \ge V_{IH}$                                                                                    | -5   | 5                    | -5   | 5                    | -5   | 5                    | -5   | 5                    | μA   |

| V <sub>OL</sub>    | Output Low Voltage                              | V <sub>CC</sub> = Min, I <sub>OL</sub> = 8 mA                                                                               | -    | 0.4                  | -    | 0.4                  | -    | 0.4                  | -    | 0.4                  | V    |

| V <sub>OH</sub>    | Output High Voltage                             | V <sub>CC</sub> = Min, I <sub>OH</sub> = -4 mA                                                                              | 2.4  | -                    | 2.4  | -                    | 2.4  | -                    | 2.4  | -                    | V    |

| ICC                | Operating Power Supply<br>Current               |                                                                                                                             | -    | 190                  | -    | 160                  | -    | 150                  | -    | 120                  | mA   |

| I <sub>CCSB</sub>  | Standby Power Supply<br>Current                 | $V_{CC} = Max, \overline{CE} \ge V_{IH}, I_{I/O} = 0 \text{ mA},$<br>$F = F_{max}^{[3]}$                                    | -    | 70                   | _    | 40                   | -    | 30                   | _    | 20                   | mA   |

| I <sub>CCSB1</sub> | Power Down Power<br>Supply Current              | $ \begin{array}{l} V_{CC} = Max, \overline{CE} \geq \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | _    | 20                   | _    | 10                   | _    | 10                   | _    | 10                   | mA   |

|                    | L version only                                  |                                                                                                                             |      | -                    |      | 100                  |      | 100                  |      | 100                  | μA   |

1. Typical characteristics are at  $V_{CC}$  = 5 V, TA = 25

2. These are absolute values with reject to device ground and all overshoots due to system or tester noise are included.

3.  $F_{MAX} = 1/t_{RC}$ .

# GLT725608/08L

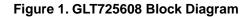

#### Data Retention (L version only)

| Symbol                           | Parameter                            | Test Conditions                                                                                                                                                                     | Min                            | Typ <sup>[1]</sup> ) | Мах | Unit |

|----------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------|-----|------|

| V <sub>DR</sub>                  | V <sub>CC</sub> for Data retention   | $\label{eq:constraint} \boxed{ \frac{\overline{CE}}{CE} \geq V_{CC}} \ \text{-0.2 V}, \ V_{IN} \geq V_{CC} \ \text{-0.2 V} \\ \text{or } V_{IN} \leq 0.2 \ \text{V} \\ \end{array}$ | 2.0                            | -                    | 5.5 | V    |

| I <sub>CCDR</sub> <sup>[1]</sup> | Data Retention Current               | V <sub>DR</sub> = 2.0 V                                                                                                                                                             |                                | -                    | 30  | μA   |

|                                  |                                      | V <sub>DR</sub> = 3.0 V                                                                                                                                                             |                                |                      | 50  | μA   |

| t <sub>CDR</sub>                 | Chip Deselect to Data Retention Time | See Retention Waveform                                                                                                                                                              | 0                              | -                    | -   | ns   |

| t <sub>R</sub>                   | Operating Recovery Time              | ]                                                                                                                                                                                   | t <sub>RC</sub> <sup>[2]</sup> | -                    | -   | ns   |

1.  $\overline{\text{CE}} \ge V_{DR}$  -0.2 V,  $V_{IN} \ge V_{DR}$  -0.2 V or  $V_{IN} \le$  0.2 V.

2.  $t_{RC}$  = Read Cycle Time.

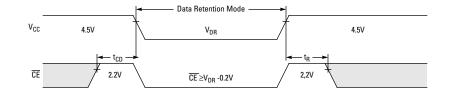

#### **AC Test Conditions**

| Parameter                               | Rating     |

|-----------------------------------------|------------|

| Input pulse levels                      | 0V to 3.0V |

| Input rise and fall times               | 3 ns       |

| Input and Output Timing Reference level | 1.5 V      |

Figure 3. AC Test Loads and Waveforms

| JEDEC              |                  |                                       | -10 <sup>[1]</sup> |     | -10 <sup>[1]</sup> -12 |     | -15 |     | -20 |     |      |

|--------------------|------------------|---------------------------------------|--------------------|-----|------------------------|-----|-----|-----|-----|-----|------|

| Symbol             | Symbol           | Parameter                             | Min                | Max | Min                    | Max | Min | Max | Min | Max | Unit |

| t <sub>AVAX</sub>  | t <sub>RC</sub>  | Read Cycle Time                       | 10                 | -   | 12                     | -   | 15  | -   | 20  | -   | ns   |

| t <sub>AVQV</sub>  | t <sub>AA</sub>  | Address Access Time                   | -                  | 10  | -                      | 12  | -   | 15  | -   | 20  | ns   |

| t <sub>e1lQV</sub> | t <sub>ACS</sub> | Chip Select Access Time, CE           | -                  | 10  | _                      | 12  | _   | 15  | _   | 20  | ns   |

| t <sub>GLQV</sub>  | t <sub>OE</sub>  | Output Enable to Output Valid         | -                  | 5   | -                      | 5   | -   | 6   | -   | 8   | ns   |

| t <sub>e1lox</sub> | t <sub>CLZ</sub> | Chip Select to Output Low Z, CE       | 3                  | -   | 3                      | -   | 3   | -   | 3   | -   | ns   |

| t <sub>GLQX</sub>  | t <sub>OLZ</sub> | Output Enable to Output in Low Z      | 0                  | -   | 3                      | -   | 3   | -   | 3   | -   | ns   |

| t <sub>e1HQZ</sub> | t <sub>CHZ</sub> | Chip Deselect to Output in High Z, CE | -                  | 7   | -                      | 7   | -   | 8   | -   | 10  | ns   |

| t <sub>ghoz</sub>  | t <sub>OHZ</sub> | Output Disable to Output in High Z    | -                  | 6   | -                      | 6   | _   | 6   | -   | - 8 | ns   |

| t <sub>AXQX</sub>  | t <sub>OH</sub>  | Output Hold from Address Change       | 3                  | -   | 3                      | -   | 3   | -   | 3   | -   | ns   |

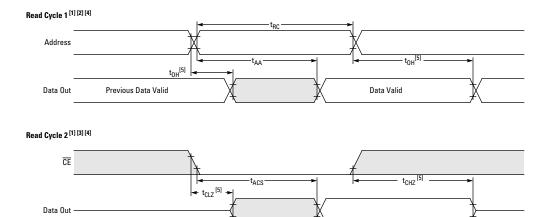

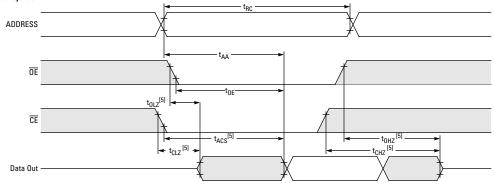

### AC Characteristics - Read Cycle (over the commercial operating range)

1. GLT725609 Standard power only.

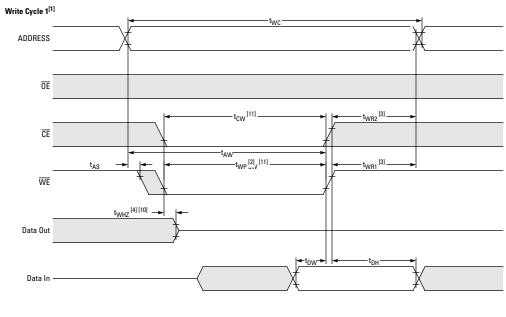

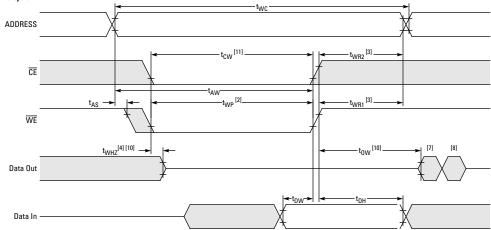

### AC Characteristics - Write Cycle (over the commercial operating range)

| JEDEC              |                  |                               | -10 <sup>[1]</sup> |     | -1  | -12 -15 |     | 15  | -20 |     |       |

|--------------------|------------------|-------------------------------|--------------------|-----|-----|---------|-----|-----|-----|-----|-------|

| Symbol             | Symbol           | Parameter                     | Min                | Max | Min | Max     | Min | Max | Min | Max | Units |

| t <sub>AVAX</sub>  | t <sub>WC</sub>  | Write Cycle Time              | 10                 | -   | 12  | -       | 15  | -   | 20  | -   | ns    |

| t <sub>E1LWH</sub> | t <sub>CW</sub>  | Chip Select to End of Write   | 10                 | -   | 10  | -       | 12  | -   | 15  | -   | ns    |

| t <sub>AVWL</sub>  | t <sub>AS</sub>  | Address Set up Time           | 0                  | -   | 0   | -       | 0   | -   | 0   | -   | ns    |

| t <sub>AVWH</sub>  | t <sub>AW</sub>  | Address Valid to End of Write | 10                 | -   | 10  | -       | 12  | -   | 15  | -   | ns    |

| t <sub>WLWH</sub>  | t <sub>WP</sub>  | Write Pulse Width             | 8                  | -   | 10  | -       | 12  | -   | 15  | -   | ns    |

| t <sub>WHAX</sub>  | t <sub>WR1</sub> | Write Recovery Time, WE       | 0                  | -   | 0   | -       | 0   | -   | 0   | -   | ns    |

| t <sub>E2LAX</sub> | t <sub>WR2</sub> | Write Recovery Time, CE       | 0                  | -   | 0   | -       | 0   | -   | 0   | -   | ns    |

| t <sub>WLQZ</sub>  | t <sub>WHZ</sub> | Write to Output in High Z     | -                  | 6   | -   | 7       | -   | 8   | -   | 10  | ns    |

| t <sub>dvwh</sub>  | t <sub>DW</sub>  | Data to Write Time Overlap    | 6                  | -   | 6   | -       | 7   | -   | 8   | -   | ns    |

| t <sub>WHDX</sub>  | t <sub>DH</sub>  | Data Hold from Write Time     | 0                  | -   | 0   | -       | 0   | -   | 0   | -   | ns    |

| t <sub>whax</sub>  | t <sub>ow</sub>  | End of Write to Output Active | 0                  | -   | 3   | -       | 3   | -   | 3   | -   | ns    |

1. GLT725609 Standard power only.

# GLT725608/08L

Read Cycle 3<sup>[1]</sup>

WE is high for READ Cycle.

Device is continuously selected CE ≤ V<sub>IL</sub> and CE 2 ≥ V<sub>IH</sub>.

Address valid prior to or coincident with CE 1 transition low and/or CE transition high.

OE ≤ V<sub>IL</sub>

5. Transition is measured  $\pm 200 \text{ mV}$  from steady state with C<sub>L</sub> = 5 pF.

Figure 4. Read Cycle Timing

Write Cycle 2<sup>[1][6]</sup>

1. WE must be high during address transitions.

- The internal write time of the memory is defined by the overlap CE 1 and CE 2 active and WE low. All signals must be active to initiate a write and any one 2. signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the second transition edge of the signal that terminates the write.

- 3.

- 4.

- Two is near the ortho. Two is measured from the earlier of CE 1 or WE going high or CE 2 going low at the end of write cycle. During this period, I/O pins are in the output state so that the input signals of opposite phase to the outputs must not be applied. If the CE 1 low transition or the CE 2 high transition occurs simultaneously with the WE low transition or after the WE transition, outputs remain in high imped-5.  $\begin{array}{l} \hline & \text{ance state.} \\ \hline & \overline{\text{OE}} \text{ is continuously low } (\overline{\text{OE}} = \text{V}_{IL}). \\ \hline & \text{D}_{\text{OUT}} \text{ is the same phase of write data of this write cycle.} \end{array}$

- 6.

- 7.

- 8. 9.

- Dour is the read data of next address. If CE 1 is low and CE 2 is high during this period, I/O pins are in the output state. Then the data input signals of the opposite phase to the outputs must not be applied to them.

# 10. Transition is measured $\pm$ 200 mV from steady state with C<sub>L</sub> = 5 pF. 11. t<sub>CW</sub> is measured from the later of $\overline{CE}$ 1 going low or $\overline{CE}$ 2 going high to the end of write.

#### Figure 5. Write Cycle Timing

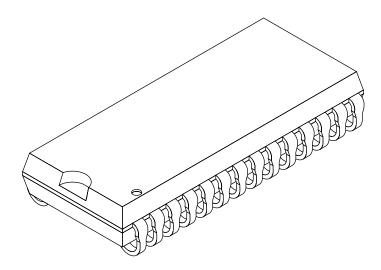

#### **PACKAGING INFORMATION**

|--|

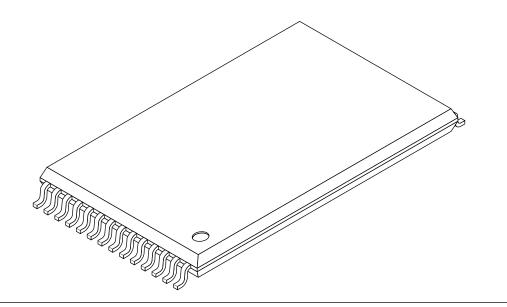

Figure 7. 28-Pin TSOP Pin Assignment

Figure 8. 28-Pin 300 mil SOJ Package Dimensions

9

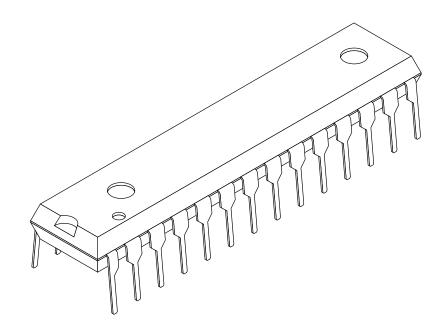

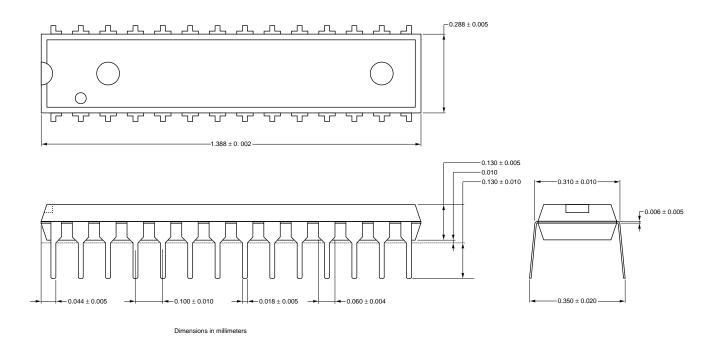

Figure 9. 28-Pin 300 mil PDIP Package Dimensions

Figure 10. 28-Pin 600 mil PDIP Package Dimensions

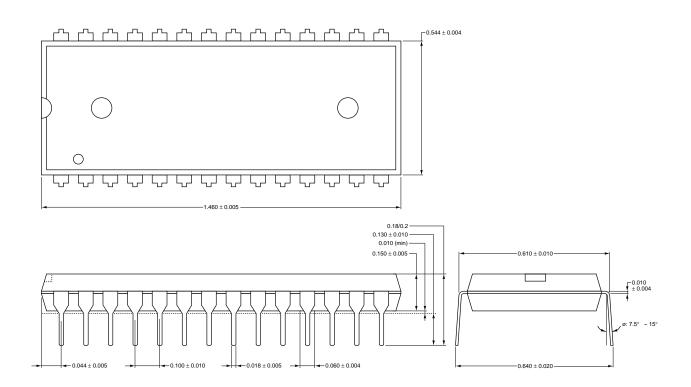

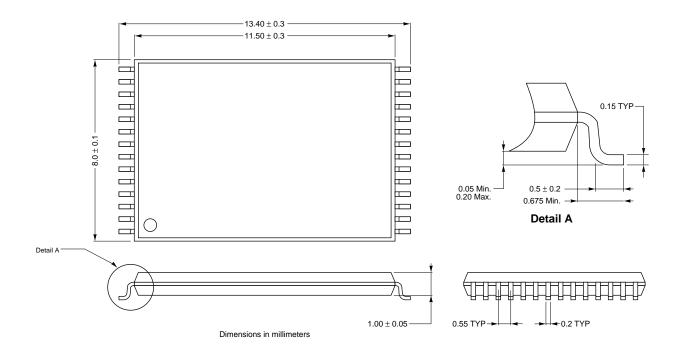

Figure 11. 28-Pin (8 x 13.4 mm) TSOP (Type I) Package Dimensions

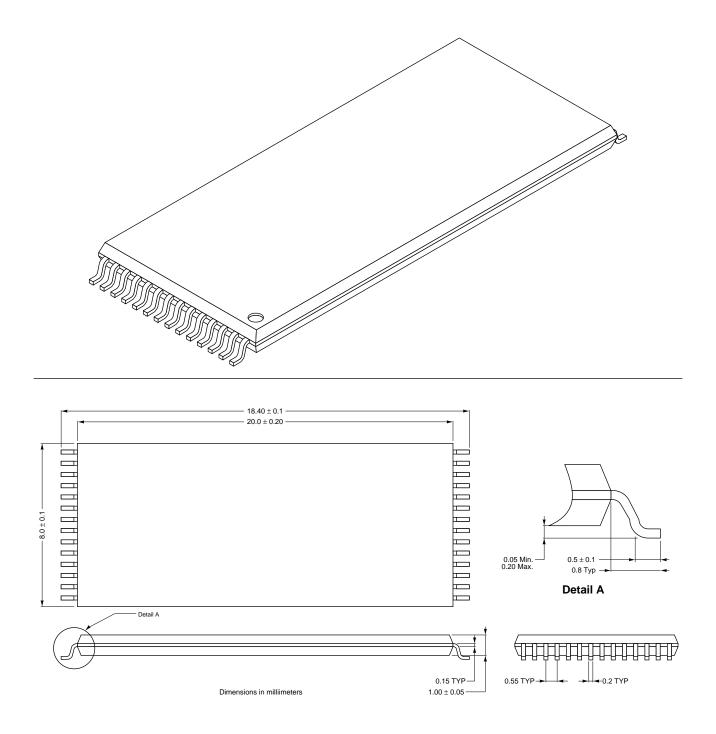

Figure 12. 28-Pin (8 x 20 mm) TSOP (Type I) Package Dimensions

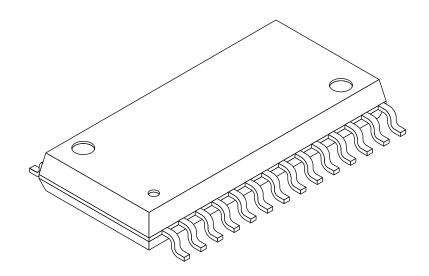

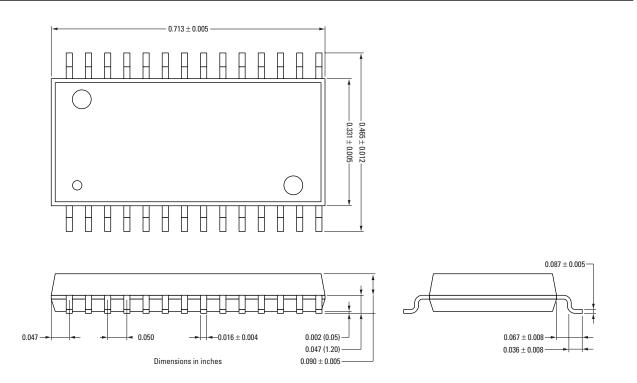

Figure 13. 28-Pin 330 mil SOP Package Outline

## **ORDERING INFORMATION**

.....

| Part Number    | Speed | Power       | Package              |

|----------------|-------|-------------|----------------------|

| GLT725608-12T  | 12 ns | Normal      | 28-Pin SDIP          |

| GLT725608-15T  | 15 ns | Normal      | 28-Pin SDIP          |

| GLT725608-20T  | 20 ns | Normal      | 28-Pin SDIP          |

| GLT725608-12J3 | 12 ns | Normal      | 28-Pin 300 mil SOJ   |

| GLT725608-15J3 | 15 ns | Normal      | 28-Pin 300 mil SOJ   |

| GLT725608-20J3 | 20 ns | Normal      | 28-Pin 300 mil SOJ   |

| GLT725608-10TS | 10 ns | Normal      | 28-Pin TSOP (Type I) |

| GLT725608-12T  | 12 ns | Mix Voltage | 28-Pin SDIP          |

| GLT725608-15T  | 15 ns | Mix Voltage | 28-Pin SDIP          |

| GLT725608-20T  | 20 ns | Mix Voltage | 28-Pin SDIP          |

| GLT725608-12J3 | 12 ns | Mix Voltage | 28-Pin 300 mil SOJ   |

| GLT725608-15J3 | 15 ns | Mix Voltage | 28-Pin 300 mil SOJ   |

| GLT725608-20J3 | 20n s | Mix Voltage | 28-Pin 300 mil SOJ   |

#### www.glinktech.com

#### **G-LINK Technology**

1753 South Main Street Milpitas, California, 95035, USA TEL: 408-240-1380 • FAX: 408-240-1385

#### **G-LINK Technology Corporation, Taiwan**

6F, No. 24-2, Industry E. Rd. IV Science-Based Industrial Park Hsin Chu, Taiwan, R.O.C. TEL: 03-578-2833 • FAX: 03-578-5820

© 2001 G-LINK Technology

G-LINK Technology reserves the right to change products or specifications without notice.

The information contained in this document does not convey any license under copyrights, patent rights or trademarks claimed and owned by G-LINK or its subsidiaries. G-LINK assumes no liability for G-LINK applications assistance, customer's product design, or infringement of patents arising from use of semiconductor devices in such systems' designs. Nor does G-LINK warrant or represent that any patent right, copyright, or other intellectual property right of G-LINK covering or relating to any combination, machine, or process in which such semiconductor devices might be or are used.

G-LINK Technology's products are not authorized for use in life support devices or systems. Life support devices or systems are device or systems which are: a) intended for surgical implant into the human body and b) designed to support or sustain life; and when properly used according to label instructions, can reasonably be expected to cause significant injury to the user in the event of failure.

The information contained in this document is believed to be entirely accurate. However, G-LINK Technology assumes no responsibility for inaccuracies.

All rights reserved. No part of this document may be copied or reproduced in any form or by any means or transferred to any third party without the prior written consent of G-LINK Technology.

Circuit diagrams utilizing G-LINK products are included as a means of illustrating typical semiconductor applications. Complete information sufficient for design purposes is not necessarily given.