Keysight Technologies W1717 SystemVue Hardware Design Kit Data Sheet

> From Algorithm to Implementation of Digital Signal Processing Systems

# Overview

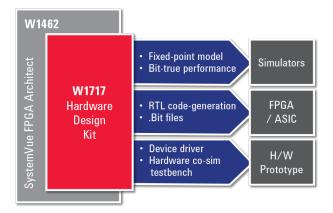

The W1717 SystemVue Hardware Design Kit (HDK) is a hardware design flow personality that adds onto the core W1461 SystemVue core environment to accelerate the design and verification of digital signal processing (DSP) algorithms in communications and aerospace defense systems. It allows system architects and algorithm developers to create baseband models quickly and validate their performance at the system-level against RF models, test equipment, Standards references, and other signals and conditions.

The W1717 HDK enables a model-based design approach to FPGA rapid prototyping and integrates easily into mainstream design and verification flows. It includes a synthesizable fixed-point model library, and offers a rich set of example designs, ranging from basic filters to realistic communications physical layer design.

# **Key Features**

# **Design and Verification Productivity**

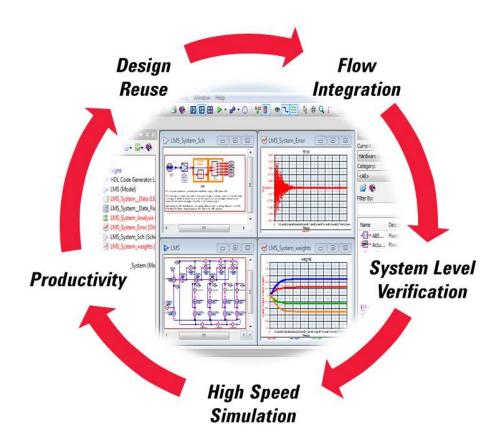

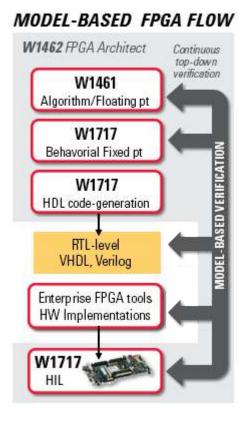

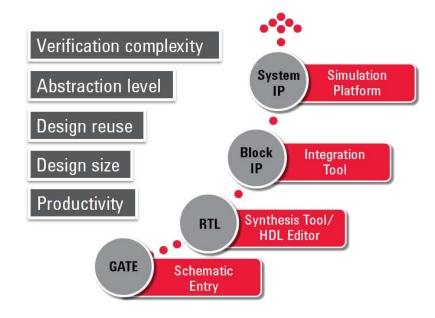

System-level modelers and verification engineers can take advantage of SystemVue's comprehensive integration into hardware design and verification flows. A fixed-point simulation library predicts hardware-like effects without committing to a targeted implementation, and generates synthesizable, hierarchical, RTL-level Verilog and VHDL that is bit-true and cycle accurate. This provides a path to implementation and creates a verification wrapper for polymorphic model-based design flows moving from algorithm to fixed point to RTL and to instantiated hardware. The ability to co-simulate with external hardware description language (HDL) simulators or real hardware is included free with the SystemVue core environment.

*Figure 2. The HDK provides the fastest hardware design flow, enabling high performance and high productivity*

### **Fixed Point Design**

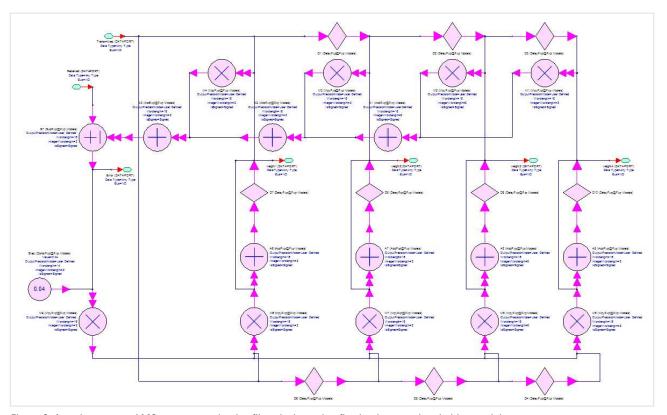

Mapping signal-processing algorithms to dedicated hardware with fixed-point arithmetic is often an integral part of the algorithm design and analysis flow. Hardware Design Parts, available in the HDK, can be used to build, simulate and analyze fixed-point systems. A library of over 45 functions, from low-level logic elements to more advanced signal-processing parts such as filters and fast Fourier transforms (FFTs), is available. The fixed-to-float and float-to-fixed conversion parts provide a means of interfacing fixed-point components with other SystemVue blocks. Hardware Design Parts can also be configured to automatically collect information on dynamic range, overflows and underflows. The parts can be shown in the Fixed-Point Analysis Table to help engineers with system optimization.

The SystemVue HDK supports use of standard-compliant IEEE 1666 SystemC fixed-point data types.

Figure 3. A cycle-accurate LMS transpose adaptive filter design using fixed-point generic primitive models

### Synthesizable HDL code generation

SystemVue's HDL Code Generation capability provides users an easy path from schematic design to hardware. A user-created SystemVue sub-network model, with only synthesizable fixedpoint parts from the HDK, can be used to generate VHDL/Verilog for the sub-network. For Xilinx's Virtex-4/5/6 FPGAs, SystemVue provides a path to configure the clock and reset the user's HDL design, as well as set up an ISE project or generate bit files directly. For Altera's Cyclone IV/Stratix IV/Stratix V FPGAs, SystemVue provides a similar path to set up a Quartus II project or generate programming files directly.

# Simulation

### VHDL/Verilog co-simulation

With the SystemVue HDL co-simulation feature, users can simulate components represented in a HDL, VHDL and Verilog, in the same schematic with other SystemVue components. This integrated capability provides complete design flexibility and complements other SystemVue features, including HDL generation.

HDL co-simulation also allows the user's existing HDL code to be included in system-level simulations, and integrated with local synthesizable fixed-point primitives. The HDL Code Generator connects the user's HDL code with other Hardware Design Parts to generate HDL codes for the whole design. It then runs the Xilinx/Altera automatic implementation flow to generate the programming file.

The ability to design all portions of a communications product in one integrated environment eliminates design errors resulting from disconnects among different design teams. By co-simulating with HDL designs, users can easily incorporate existing HDL intellectual property (IP) into new designs, or even co-simulate with SystemVue-generated HDL. SystemVue integrates well with the Mentor ModelSim or Aldec Riviera-PRO HDL simulators via two simulation modes, either direct simulation from the SystemVue user interface or hierarchical HDL project generation, for full interaction and debugging using the external development environments.

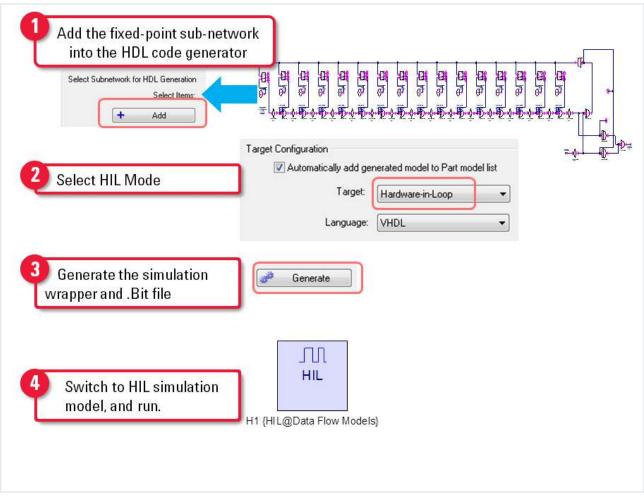

### Hardware co-simulation

The SystemVue Hardware-in-Loop (HIL) co-simulation engine allows the dynamic use of FPGA hardware to accelerate computational tasks in a multi-threaded software environment. Effectively, it circumvents traditional bottlenecks where the accelerator hardware would only be usable by a single thread at a time. The engine provides both the hardware implementation and dynamic partial reconfiguration on Virtex-6 to implement functions or measurements in FPGA hardware.

Hardware co-simulation requires a great deal of data stream exchange between processors and FPGA cards. It can be streamed via the PCI Express<sup>®</sup> bus. In theory, an eight-lane PCI Express Gen 2 bus offers a peak throughput of 500 MB/s. Even though PCI Express suffers from latencies inherent in device drivers and operating system interrupt handling, there are clear advantages to performing hardware co-simulation with a FPGA board using a PCI Express connection to the host processor.

Figure 4. Automated model-based HIL polymorphism in SystemVue HDK

# **Design Reuse**

Design reuse is part of the growing Electronic Design Automation (EDA) industry trend toward repeated use of previously designed components. SystemVue provides two efficient methods for carrying IP into the system-level design environment.

Figure 5. SystemVue HDK improves design productivity by allowing engineers to design at a higher abstraction level and reuse their designs

The SystemVue environment provides the primary method for design re-use, using sub-network models. SystemVue subnetworks are portable and easily inserted into other design workspaces (e.g., via a copy and paste function). Within SystemVue, they are known as "design" objects, and contain a symbol, schematic, equation, parameters, and notes. Sub-networks can include fixed-point schematics built using the graphical UI, or external HDL code that is instantiated in SystemVue using the HDL co-simulation block.

A second method of design re-use is facilited by the W1717 HDK's XilinxIPIntegrator model. This model allows Xilinx CORE Generator IP cores to be co-simulated using external HDL simulators. Furthermore, SystemVue can combine these external Xilinx CORE Generator IP cores with native SystemVue fixed-point designs and other external HDL blocks, and then use HDL Code Generation to create a hierarchical HDL for the overall design. SystemVue's XilinxIPIntegrator model supports most of the Xilinx IP cores needed for communications signal processing including: Base IP, Basic Elements, Communication & Networking, Digital Signal Processing, Math Functions, and Memory & Storage Elements.

After HDL code generation is complete, SystemVue can be configured to invoke Xilinx' automatic FPGA implementation tools to generate a programming (".bit") file and add a polymorphic model choice for the HIL model, all in a single step, from the SystemVue GUI.

# **Benefits**

The W1717 HDK provides a number of key benefits for baseband algorithm developers and communications and radar system architects, including:

### • Fidelity

Quickly account for bit-true hardware effects prior to targeting, while still at the architecture level, for better baseband-RF partitioning.

# • Productivity

Integrate your proprietary, hand-optimized HDL blocks or import IP cores from external sources, such as Xilinx CORE Generator IP.

# • Vendor-neutrality

Generate target-neutral RTL that is transportable between hardware vendors.

# Tool connectivity

Rapid-prototyping with direct integration to Xilinx ISE, Altera Quartus II and other synthesis tools.

### Real-time verification

Verify and accelerate algorithms with HIL cosimulation with Xilinx Virtex-6 families (such as the ML-605 development board) over a PCI Express interface.

### Cross-domain model-based design

Verify and debug algorithms at every level of FPGA hardware abstraction, in the presence of models from other domains, such as RF EDA models, test and measurement waveforms, and simulation-based wireless Standards references.

# Included with the W1717 HDK

- Fixed-point library containing 45 bit-true, cycle accurate models. Enables fixed-point data type and simulation mode with block-level/ pin-level, fixed-point histograms and "red-x" overflow/underflow analysis.

- Integration of custom libraries of handgenerated HDL and external IP cores, such as the Xilinx CORE Generator.

- HDL code generation of RTL-level VHDL/ Verilog, complete with design hierarchy, system-level test bench wrappers, test vectors, and intelligent creation of clock ready and enable signals.

- Polymorphic model instantations added for each installed HDL simulator, such as Aldec Riviera-PRO, or Mentor Modelsim SE, enabling easy model-based scripting and co-simulation, with verification-in-place.

- Direct integration of synthesis tools (such as Xilinx ISE and Altera Quartus II) from the SystemVue GUI.

- **Hardware-in-the-Loop** co-simulation. Bring real-time Virtex-6 acceleration into SystemVue using development boards such as the ML-605 over PCle.

# Configuration

The W1717 HDK can be added to any SystemVue environment. It is already included in both the W1462 SystemVue FPGA Architect and W1465 SystemVue System Architect bundles.

### myKeysight

www.keysight.com/find/mykeysight

A personalized view into the information most relevant to you.

#### www.axiestandard.org

AdvancedTCA® Extensions for Instrumentation and Test (AXIe) is an open standard that extends the AdvancedTCA for general purpose and semiconductor test. Keysight is a founding member of the AXIe consortium.

# www.lxistandard.org

LAN eXtensions for Instruments puts the power of Ethernet and the Web inside your test systems. Keysight is a founding member of the LXI consortium.

# www.pxisa.org

PCI eXtensions for Instrumentation (PXI) modular instrumentation delivers a rugged, PC-based high-performance measurement and automation system.

#### **Three-Year Warranty**

### www.keysight.com/find/ThreeYearWarranty

Keysight's commitment to superior product quality and lower total cost of ownership. The only test and measurement company with three-year warranty standard on all instruments, worldwide.

# **Keysight Assurance Plans**

# www.keysight.com/find/AssurancePlans

Up to five years of protection and no budgetary surprises to ensure your instruments are operating to specification so you can rely on accurate measurements.

### www.keysight.com/quality

Keysight Electronic Measurement Group DEKRA Certified ISO 9001:2008 **Quality Management System**

### **Keysight Channel Partners**

### www.keysight.com/find/channelpartners

Get the best of both worlds: Keysight's measurement expertise and product breadth, combined with channel partner convenience.

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

### Americas

| Canada        | (877) 894 4414   |

|---------------|------------------|

| Brazil        | 55 11 33 51 7010 |

| Mexico        | 001 800 254 2440 |

| United States | (800) 829 4444   |

|               |                  |

#### Asia Pacific

| Australia          | 1 800 629 485  |

|--------------------|----------------|

| China              | 800 810 0189   |

| Hong Kong          | 800 938 693    |

| India              | 1 800 112 929  |

| Japan              | 0120 (421) 345 |

| Korea              | 080 769 0800   |

| Malaysia           | 1 800 888 848  |

| Singapore          | 1 800 375 8100 |

| Taiwan             | 0800 047 866   |

| Other AP Countries | (65) 375 8100  |

#### Europe & Middle East

| Belgium        | 32 (0) 2 404 93 40   |

|----------------|----------------------|

| Denmark        | 45 45 80 12 15       |

| Finland        | 358 (0) 10 855 2100  |

| France         | 0825 010 700*        |

|                | *0.125 €/minute      |

| Germany        | 49 (0) 7031 464 6333 |

| Ireland        | 1890 924 204         |

| Israel         | 972-3-9288-504/544   |

| Italy          | 39 02 92 60 8484     |

| Netherlands    | 31 (0) 20 547 2111   |

| Spain          | 34 (91) 631 3300     |

| Sweden         | 0200-88 22 55        |

| United Kingdom | 44 (0) 118 927 6201  |

|                |                      |

For other unlisted countries: www.keysight.com/find/contactus (BP-04-11-14)

This information is subject to change without notice. © Keysight Technologies, 2013-2014 Published in USA, August 1, 2014 5991-2056EN www.keysight.com