# Keysight U4154B Logic Analyzer

Service Guide

### **Notices**

© Keysight Technologies 2014

No part of this manual may be reproduced in any form or by any means (including electronic storage and retrieval or translation into a foreign language) without prior agreement and written consent from Keysight Technologies as governed by United States and international copyright laws.

### **Trademarks**

Windows and MS Windows are U.S. registered trademarks of Microsoft Corporation.

Windows XP is a U.S. registered trademark of Microsoft Corporation.

### Manual Part Number

U4154-97006

### **Edition**

First edition, September 2014

Available in electronic format only

Keysight Technologies 1900 Garden of the Gods Road Colorado Springs, CO 80907 USA

### Warranty

THE MATERIAL CONTAINED IN THIS DOCU-MENT IS PROVIDED "AS IS," AND IS SUB-JECT TO BEING CHANGED, WITHOUT NOTICE, IN FUTURE EDITIONS. FURTHER, TO THE MAXIMUM EXTENT PERMITTED BY APPLICABLE LAW, KEYSIGHT DISCLAIMS ALL WARRANTIES, EITHER EXPRESS OR IMPLIED WITH REGARD TO THIS MANUAL AND ANY INFORMATION CONTAINED HEREIN, INCLUDING BUT NOT LIMITED TO THE IMPLIED WARRANTIES OF MERCHANT-ABILITY AND FITNESS FOR A PARTICULAR PURPOSE, KEYSIGHT SHALL NOT BE LIABLE FOR ERRORS OR FOR INCIDENTAL OR CON-SEQUENTIAL DAMAGES IN CONNECTION WITH THE FURNISHING, USE, OR PERFOR-MANCE OF THIS DOCUMENT OR ANY INFORMATION CONTAINED HEREIN. SHOULD KEYSIGHT AND THE USER HAVE A SEPARATE WRITTEN AGREEMENT WITH WARRANTY TERMS COVERING THE MATE-RIAL IN THIS DOCUMENT THAT CONFLICT WITH THESE TERMS, THE WARRANTY TERMS IN THE SEPARATE AGREEMENT WILL CONTROL.

### **Technology Licenses**

The hardware and/or software described in this document are furnished under a license and may be used or copied only in accordance with the terms of such license.

### Restricted Rights Legend

If software is for use in the performance of a U.S. Government prime contract or subcontract, Software is delivered and licensed as "Commercial computer software" as defined in DFAR 252.227-7014 (June 1995), or as a "commercial item" as defined in FAR 2.101(a) or as "Restricted computer software" as defined in FAR 52.227-19 (June 1987) or any equivalent agency regulation or contract clause. Use, duplication or disclosure of Software is subject to Keysight Technologies' standard commercial license terms, and non-DOD Departments and Agencies of the U.S. Government will receive no greater than Restricted Rights as defined in FAR 52.227-19(c)(1-2) (June 1987). U.S. Government users will receive no greater than Limited Rights as defined in FAR 52.227-14 (June 1987) or DFAR 252.227-7015 (b)(2) (November 1995), as applicable in any technical data.

### Safety Notices

### **CAUTION**

A CAUTION notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in damage to the product or loss of important data. Do not proceed beyond a CAUTION notice until the indicated conditions are fully understood and met.

### WARNING

A WARNING notice denotes a hazard. It calls attention to an operating procedure, practice, or the like that, if not correctly performed or adhered to, could result in personal injury or death. Do not proceed beyond a WARNING notice until the indicated conditions are fully understood and met.

### Additional Safety Notices

This apparatus has been designed and tested in accordance with IEC Publication 1010, Safety Requirements for Measuring Apparatus, and has been supplied in a safe condition. This is a Safety Class I instrument (provided with terminal for protective earthing). Before applying power, verify that the correct safety precautions are taken (see the following warnings). In addition, note the external markings on the instrument that are described under "Safety Symbols."

### Warnings

- Before turning on the instrument, you must connect the protective earth terminal of the instrument to the protective conductor of the (mains) power cord. The mains plug shall only be inserted in a socket outlet provided with a protective earth contact. You must not negate the protective action by using an extension cord (power cable) without a protective conductor (grounding). Grounding one conductor of a two-conductor outlet is not sufficient protection.

- Only fuses with the required rated current, voltage, and specified type (normal blow, time delay, etc.) should be used. Do not use repaired fuses or short-circuited fuseholders. To do so could cause a shock or fire hazard.

- If you energize this instrument by an auto transformer (for voltage reduction or mains isolation), the common terminal must be connected to the earth terminal of the power source.

- Whenever it is likely that the ground protection is impaired, you must make the instrument inoperative and secure it against any unintended operation.

- Service instructions are for trained service personnel. To avoid dangerous electric shock, do not perform any service unless qualified to do so. Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

- · Do not install substitute parts or perform any unauthorized modification to the instrument.

- Capacitors inside the instrument may retain a charge even if the instrument is disconnected from its source of supply.

- Do not operate the instrument in the presence of flammable gasses or fumes. Operation of any electrical instrument in such an environment constitutes a definite safety hazard.

- Do not use the instrument in a manner not specified by the manufacturer.

### To clean the instrument

If the instrument requires cleaning: (1) Remove power from the instrument. (2) Clean the external surfaces of the instrument with a soft cloth dampened with a mixture of mild detergent and water. (3) Make sure that the instrument is completely dry before reconnecting it to a power source.

### Safety Symbols

Instruction manual symbol: the product is marked with this symbol when it is necessary for you to refer to the instruction manual in order to protect against damage to the product.

Hazardous voltage symbol.

Earth terminal symbol: Used to indicate a circuit common connected to grounded chassis.

### Keysight U4154B Logic Analyzer - At a Glance

The U4154B logic analyzer module is a 136 channel state and timing analyzer that provides 2.5 Gb/s state logic analysis and up to 5.0 GHz timing analysis. The U4154B has 4 M to 200 M sample memory depth (depending on the option chosen).

The U4154B logic analyzer module uses 4 pod cables. Each of these pod cables has 2 90-pin probe connector pods making it a total of eight pods per U4154B module. Each of these pods contain 17 channels, out of which 16 are data channels and 1 channel is bonus bit or clock channel.

### Features

Some of the main features of the U4154B are as follows:

- · 136 channels per module

- Expandable to 272 channels (as a 2-card set in the AXIe chassis).

- · 2.5 Gb/s maximum state acquisition speed (full channel).

- 4.0 Gb/s maximum state acquisition speed (half channel).

- · "Eye scan" feature.

- A state sampling clock with four clock qualifiers (Pods 2, 3, 4, and 5 of the clocking module) and an additional "RESET" clock qualifier (Pod 7 of the clocking module).

- 2.5 GHz timing analysis on all channels and 5.0 GHz timing analysis in the half channel timing mode.

### Service Strategy

The service strategy for this module is the replacement of defective module/parts. This service guide contains information for finding a defective assembly by testing and servicing the U4154B logic analyzer module.

The modules can be returned to Keysight Technologies for all service work, including troubleshooting. Contact your nearest Keysight Technologies Sales Office for more details.

### Contacting Keysight Technologies

To locate a sales or service office near you, go to www.keysight.com/find/contactus.

### Application

This service guide applies to U4154B logic analyzer modules installed in a M9502A or M9505A AXIe chassis.

Figure 1 U4154B Logic Analyzer Module

The following figure displays the M9502A (2-slot) AXIe chassis and M9505A 5-slot AXIe chassis.

Figure 2 M9502A and M9505A AXIe Chassis

### In This Service Guide

This book is the service guide for the U4154B logic analyzer module.

This service guide has five chapters.

**Chapter 1**, "General Information" contains information about the module, lists accessories for the module, gives specifications and characteristics of the module, and provides a list of the equipment required for servicing the module.

Chapter 2, "Preparing for Troubleshooting or Performance Testing" tells how to prepare the module for use.

Chapter 3, "Testing U4154B Performance" tells how to verify the U4154B performance with specifications.

Chapter 4, "Calibrating" contains calibration instructions for the module (if required).

Chapter 5, "Troubleshooting" contains explanations of self-tests and flowcharts for troubleshooting the module.

Chapter 6, "Returning and Replacing a U4154B Module or its cables" explains how to replace the module, its circuit board and cables and how to return these to Keysight Technologies.

### Contents

```

Keysight U4154B Logic Analyzer - At a Glance

In This Service Guide

1 General Information

Accessories

10

Probing Accessories

U4201A Pod Connector Cables

10

Chassis and software

10

Specifications

Characteristics

12

2 Preparing for Troubleshooting or Performance Testing

To set up the U4154B module

To test the U4154B module

15

To clean the module

3 Testing U4154B Performance

Perform the Self-Tests

19

Equipment Required for the Performance Test

Assemble the SMA/Flying Lead Test Connectors

Set Up the Test Equipment

Connect the Test Equipment

Connect the Logic Analyzer Pod to the Pulse Generator

27

Test the U4154B Module

30

Configure the Logic Analysis System

Determine maximum clock rate

Adjust sampling positions using Eye Scan

Test Pod 1

Test Pod 2

42

Test Pods 3

43

Other Pods

44

```

### Performance Test Record 45

### 4 Calibrating

Calibration Strategy 48

### 5 Troubleshooting

To use the flowcharts 50

**Self-Test Descriptions** 52

PC Board Revision Test 52

Interface FPGA Version Test 52

Interface FPGA Register Test 52

FPGA to FPGA Communication Test 52

SPI Bus Communication Test 52

EEPROM Test 52

Probe ID Read Test 52

Chip Registers Read/Write Test 52

Freq Synth Lock Detect Test 52

Acquisition Chip BIST Test 53

Resource Bus Connection Test 53

Comparator Programming Test 53

Comparator/DAC Test 53

Comparator Delay Test 53

Comparator Zero-Hold Cal Test 53

Comparator Calibrations Test 53

Acquisition Memory Write/Read Test 53

Acquisition Memory Cell Test 53

ATB (AXIe Trigger Bus) Test 54

To run the self tests 55

To exit the test system 55

To test the cables 56

### 6 Returning and Replacing a U4154B Module or its cables

To remove the U4154B module 64

To remove the logic analyzer cable 64

To install the U4201A logic analyzer cable 64

To replace the circuit board 65

To return the U4154B module or cable for Repair/Exchange 66

Index

## 1 General Information

Accessories / 10 Chassis and software / 10 Specifications / 11 Characteristics / 12

This chapter lists the accessories and some of the specifications and characteristics for testing and servicing the U4154B logic analyzer.

### Accessories

One or more of the following accessories, sold separately, are required to set up and operate the U4154B logic analyzer module for testing and servicing it.

### **Probing Accessories**

For information about probing accessories for logic analyzers with 90-pin pod connectors, see the *Probing Solutions for Logic Analyzers Catalog*, literature part number 16850-92002, available on Keysight's web site (www.keysight.com).

### U4201A Pod Connector Cables

The Keysight U4201A 90-pin pod connector cable is used to connect the U4154B module with the probes which then connect to the DUT/SUT. You need four U4201A pod cables for a U4154B module. Refer to the AXIe based Logic Analysis & Protocol Test Modules Installation Guide to learn more about these cables.

### Chassis and software

The U4154B logic analyzer requires:

- M9502A or M9505A Keysight AXIe chassis that provides slots for installing the U4154B module.

- A host PC which is a laptop or a desktop PC with a PCIe interface. The host PC connects to the Keysight AXIe chassis via PCIe interface and is used to host all the required software components of the U4154B module for configuring, controlling, and using this module.

- Keysight Logic Analyzer software version 06.00 or higher to configure, control, and use the U4154B module.

Refer to the AXIe based Logic Analysis & Protocol Test Modules Installation Guide to learn more about AXIe chassis, host PC, and the Logic Analyzer software installation.

### Specifications

The specifications are the performance standards against which the product is tested.

| U4154B Logic Analyzer Specifications |               |                                                |  |  |

|--------------------------------------|---------------|------------------------------------------------|--|--|

| Parameter                            | 2.5 Gb/s mode | Notes                                          |  |  |

| Maximum state data rate              | 2.5 Gb/s      |                                                |  |  |

|                                      | 1.4 Gb/s mode | (DDR, 1.25 GHz clock), specified at probe tip. |  |  |

| Maximum state data rate              | 1.4 Gb/s      |                                                |  |  |

### Characteristics

For a full listing of all specifications and characteristics, see the *Keysight U4154B Logic Analyzer Data Sheet*, literature part number 5992-0108EN available on Keysight's web site (www.keysight.com).

## 2 Preparing for Troubleshooting or Performance Testing

To set up the U4154B module / 14 To test the U4154B module / 15 To clean the module / 15

This chapter gives you instructions for preparing the U4154B logic analyzer module for troubleshooting or servicing it.

### Operating Environment

The operating environment specifications are listed in the *Keysight U4154B Logic Analyzer Data Sheet*, literature part number 5992-0108EN available on Keysight's web site (www.keysight.com).

Note the non-condensing humidity limitation. Condensation within the instrument can cause poor operation or malfunction. Provide protection against internal condensation.

The logic analyzer module will operate at all specifications within the temperature and humidity range. However, reliability is enhanced when operating the module within the following ranges:

Temperature: +20°C to +35°C (+68°F to +95°F)

Humidity: 20% to 80% non-condensing

### To set up the U4154B module

To set up the U4154B module for troubleshooting/servicing, you first need to install it in one of the slots of the AXIe chassis. Then connect the chassis to the host PC via a PCIe link. On the host PC, install the Logic and Protocol Analyzer (6.0 or higher) application to configure and control the U4154B module. Connect the U4154B module to a probe using the U4201A pod connector cables.

You can find the detailed instructions for configuring and installing the U4154B module into the AXIe chassis in the AXIe based Logic Analysis & Protocol Test Modules Installation Guide.

### To test the U4154B module

The U4154B logic analyzer module does not require an operational accuracy calibration or adjustment. After installing the module, you can test and use the module.

- If you require a test to verify logic analyzer's performance with the specifications, see "Testing U4154B Performance" on page 17.

- If you require a test to verify correct module operation, see "To run the self tests" on page 55.

- If the module does not operate correctly, see "Troubleshooting" on page 49.

### To clean the module

- With the AXIe chassis turned off and unplugged, use a cloth moistened with a mixture of mild detergent and water to clean the front panel of the module.

- Do not attempt to clean the module's circuit board.

2 Preparing for Troubleshooting or Performance Testing

## 3 Testing U4154B Performance

Perform the Self-Tests / 19

Equipment Required for the Performance Test / 20

Assemble the SMA/Flying Lead Test Connectors / 21

Set Up the Test Equipment / 25

Connect the Test Equipment / 27

Test the U4154B Module / 29

Performance Test Record / 45

This chapter tells you how to test the performance of the U4154B logic analyzer against the specifications listed on page 11.

To ensure the U4154B logic analyzer module is operating as specified, software tests (self-tests) and a manual performance test is done. The logic analyzer is considered performance-verified if all of the software tests and the manual performance test have passed.

The specifications for the U4154B module define a maximum state data rate at which data can be acquired in state mode. The manual performance test (maximum state data rate test) verifies that the logic analyzer meets these specifications.

### **AXIe Chassis**

You must test the U4154B logic analyzer module in a M9502A or M9505A AXIe chassis.

### **Test Strategy**

Only specified parameters are tested. Specifications are listed on page 11. The test conditions defined in this procedure ensure that the specified parameter is as good as or better than specifications. No attempt is made to determine performance which is better than specifications. Not all channels of the logic analyzer will be tested; a sample of channels is tested. The calibration laboratory may choose to elaborate on these tests and test all channels at their discretion.

NOTE

A U4154B module that is licensed with the base speed option needs to be tested at a Keysight Service Center. The Service Center has the capability to test the module at up to the 2.5 Gb/s state speed to ensure that the calibration will remain valid even after upgrading it to the -02G license.

Eye Scan is used to adjust the sampling position on every channel. Eye scan must be used to achieve maximum state data rate performance.

The 2.5 Gb/s state logic analyzer will be tested. All eight pods will be tested, one pod at a time.

The logic analyzer acquires data on both edges of the clock, so the test frequency is set to half of the acquisition speed.

### One-card Module

To perform a complete test on a one-card module, start at the beginning of the chapter and follow each procedure.

### Multi-card Module

To perform a complete test on a multi-card module, perform the self-tests with the cards connected. Then, remove the multi-card module from the chassis and configure each card as a one-card module. Install the one-card modules into the chassis and perform the performance verification tests on each card. When the tests are complete, remove the one-card modules, reconfigure them into their original multi-card module configuration, reinstall into the chassis and perform the self-tests again. These steps are necessary to ensure that the clocks are tested on each module.

Instructions for removing and installing the module can be found in the AXIe based Logic Analysis & Protocol Test Modules Installation Guide.

### Test Interval

Test the performance of the U4154B module against its specifications at two-year intervals.

### **Test Record Description**

A Performance Test Record for recording the results of each procedure is provided in this chapter. You may want to make copies of the form, and fill-in a copy each time you test the module.

### Test Equipment

A list of the recommended test equipment is provided. You can use any equipment that satisfies the specifications given. However, the instructions are written with the presumption that you are using the recommended test equipment.

### Perform the Self-Tests

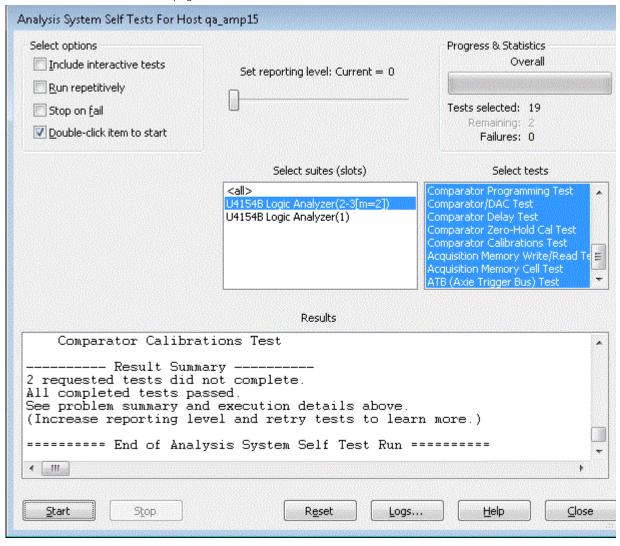

Once you have connected all the hardware components for the U4154B module and created a logical module for U4154B in the Keysight Logic Analyzer application, you are ready to run the self tests on U4154B.

- 1 Before performing the self-tests, disconnect all probes from the logic analyzer module.

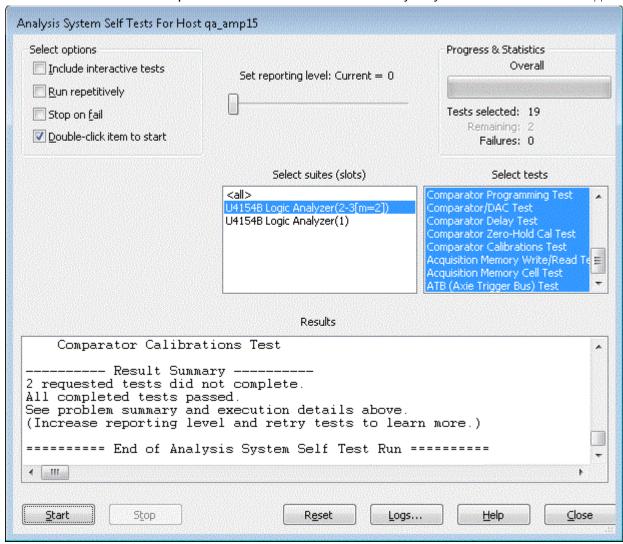

- 2 Select Help->Self-Test... from the main menu. The Analysis System Self Tests window will appear.

- 3 In the Select suites list, select U4154B. Then, select All in the Select tests list.

- 4 Select Start. This will perform a complete system self-test.

The progress of the self tests is displayed in the Results area of the window.

- 5 When the self-tests are complete, check the Results window to ensure that the Result Summary says that all tests passed. If all tests did not pass, refer to "To use the flowcharts" on page 50.

- 6 Select the Close button to close the Analysis System Self Tests window.

- 7 If all module self-tests pass, then record "PASS" in the "Logic Analysis System Self-Tests" section of the Performance Test Record (page 45).

### Equipment Required for the Performance Test

The following equipment is required for the performance test procedure.

Table 1 Equipment Required

| Equipment                                                                        | Critical Specification                                                                                                                                           | Recommended Model/Part                                           |

|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Pulse Generator                                                                  | ≥ 1275 MHz, two channels, differential outputs, 150-180 ps rise/fall time (if faster, use transition time converters)                                            | Keysight 81134A or equivalent                                    |

| 150 ps Transition Time Converter (Qty 4)                                         | Required if pulse generator's rise time is less than 150 ps. (Pulse generator conditions: Voffset=1V, $\Delta$ V=250 mV.) Required for 81134A or 8133A opt. 003. | Keysight 15435A                                                  |

| Flying Lead Probe Set (Qty 2)                                                    | A combination of U4201A & E5382A can be used.                                                                                                                    | Keysight U4203A                                                  |

| SMA/Flying Lead test connectors, (f) SMA to (f) SMA to Flying Lead Probe (Qty 4) | no substitute                                                                                                                                                    | See "Assemble the SMA/Flying Lead Test<br>Connectors" on page 21 |

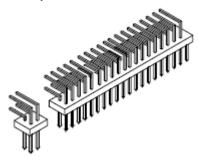

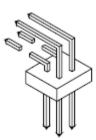

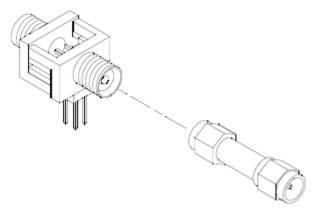

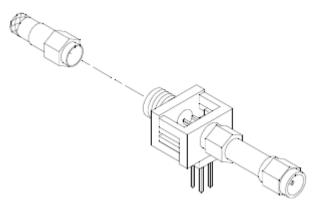

### Assemble the SMA/Flying Lead Test Connectors

The SMA/Flying Lead test connectors provide a high-bandwidth connection between the logic analyzer and the test equipment. The following procedure explains how to fabricate the four required test connectors.

Table 2 Materials Required for SMA/Flying Lead Test Connectors

| Material                                          | Critical Specification                                                                                           | Recommended Model/Part                                    |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

| SMA Board Mount Connector (Qty 8)                 |                                                                                                                  | Emerson 142-0701-801 (see www.emersonconnectivity.com)    |

| Pin Strip Header (Qty 1, which will be separated) | 0.100" X 0.100" Pin Strip Header, right angle, pin length 0.230", two rows, 0.120" solder tails, 2 X 40 contacts | 3M 2380-5121TN or similar 2- row with 0.1" pin spacing    |

| SMA 50 ohm terminators (Qty 2)                    | Minimum bandwidth 2 GHz                                                                                          | Emerson 142-0801-866 50 ohm Dummy Load Plug<br>or similar |

| SMA m-m adapter (Qty 4)                           |                                                                                                                  | Emerson 142-0901-811 SMA Plug to Plug or similar          |

3

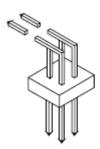

- 1 Prepare the pin strip header:

- a Cut or cleanly break a 2 x 2 section from the pin strip.

b Trim about 1.5 mm from the pin strip inner leads and straighten them so that they touch the outer leads.

c Trim about 2.5 mm from the outer leads.

d Using a very small amount of solder, tack each inner lead to each outer lead at the point where they are touching.

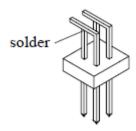

- 2 Solder the pin strip to the SMA board mount connector:

- a Solder the leads on the left side of the pin strip to the center conductor of the SMA connector as shown in the diagram below.

- b Solder the leads on the right side of the pin strip to the inside of the SMA connector's frame as shown in the diagram below. Use a small amount of solder.

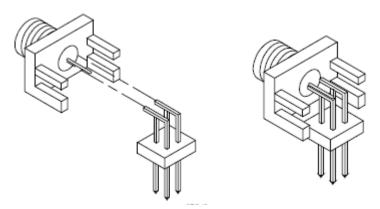

- 3 Attach the second SMA board mount connector:

- a Re-heat the solder connection made in the previous step, and attach the second SMA connector, as shown in the diagram below. Note that the second SMA connector is upside-down, compared to the first. Add a little solder to make a good connection.

- b Solder the center conductor of the second SMA connector to the center conductor of the first SMA connector and the leads on the left side of the pin strip.

- c Rotate the assembly 180 degrees and solder the two SMA board mount connector frames together.

- 4 Check your work:

- a Ensure that the following four points have continuity between them: The two pins on the left side of the pin strip, and the center conductors of each SMA connector.

- b Ensure that there is continuity between each of the two pins on the right side of the pin strip, and the SMA connector frames.

- c Ensure that there is NO continuity between the SMA connector center conductor and the SMA connector frame (ground).

3

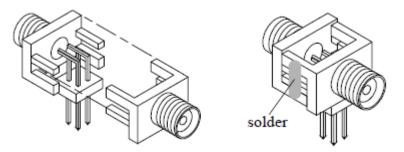

- 5 Finish creating the test connectors:

- a Attach an SMA m-m adapter to one end of each of the four SMA/Flying Lead test connectors.

b Attach a 50 ohm terminator to the other end of two of the SMA/Flying Lead test connectors.

c The finished test connector is shown in the pictures below.

### Set Up the Test Equipment

This section explains how to set up the test equipment for the maximum state data rate test.

- 1 Connect Transition Time Converters to each of the four outputs of the pulse generator: Channel 1 OUTPUT, Channel 1 OUTPUT (not), Channel 2 OUTPUT, Channel 2 OUTPUT (not).

- 2 Connect the four SMA/Flying Lead test connectors (see "Assemble the SMA/Flying Lead Test Connectors" on page 21) with 50 ohm terminators to the Transition Time Converters on the 4 pulse generator outputs. (If Transition Time Converters are not required, connect the SMA/Flying Lead test connectors directly to the pulse generator outputs.

- 3 Turn on the Pulse Generator. Let all of the test equipment and the logic analyzer warm up for 30 minutes before beginning any test.

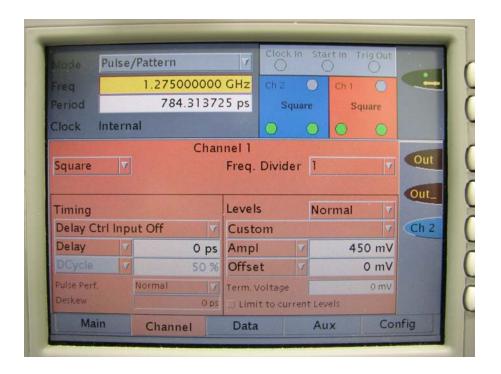

- 4 Load the default configuration into the 81134A Pulse Generator.

- · Select Main

- · Hit Recall

- Press 0

- 5 Setup the pulse generator according to the following.

- a Set the frequency of the pulse generator:

In this test procedure, the logic analyzer uses both edges of the clock to acquire data. The test frequency is half the test clock rate because data is acquired on both the rising edge and the falling edge of the clock. Set the frequency to:

- Base Option: temporally License the module to full speed and test at 1250 MHz plus 2% (1275 MHz)

- Option 02G: 1250 MHz plus 2% (1275 MHz)

This includes the frequency uncertainty of the pulse generator, plus a test margin.

If you are using an 81134A pulse generator, the frequency accuracy is ±0.005% of setting.

b Set the rest of the pulse generator parameters to the values shown in one of the following tables.

Table 3 81134A Pulse Generator Setup

| Main                        | Channel 1                           | Channel 2                           |

|-----------------------------|-------------------------------------|-------------------------------------|

| Mode: Pulse/Pattern         | Mode: Square ÷ 1                    | Mode: Square ÷ 1                    |

| Freq: set in previous step. | Timing                              | Timing                              |

| Clock Internal              | Delay Ctrl Input Off                | Delay Ctrl Input Off                |

|                             | Delay 0 ps                          | Delay 0 ps                          |

|                             | Pulse Perf: Normal                  | Pulse Perf: Normal                  |

|                             | Deskew: 0 ps                        | Deskew: 0 ps                        |

|                             | Levels: Normal, Custom              | Levels: Normal, Custom              |

|                             | Ampl: 450 mV                        | Ampl: 450 mV                        |

|                             | Offset: 0 mV                        | Offset: 0 mV                        |

|                             | Term Voltage: 0 mV                  | Term Voltage: 0 mV                  |

|                             | Limit to current Levels: unselected | Limit to current Levels: unselected |

|                             | Output: Enable (LED on)             | Output: Enable (LED on)             |

|                             | Output: Enable (LED on)             | Output: Enable (LED on)             |

### Connect the Test Equipment

Connect the Logic Analyzer Pod to the Pulse Generator

- 1 Connect one U4203A Flying Lead Probe Set to Pods 1/2 of the U4154B module.

- 2 Connect the Pod 1 U4203A Flying Lead Probe Set's CLK lead to the pin strip of the SMA/Flying Lead connector at the pulse generator's Channel 1 OUTPUT.

NOTE

On all connection be sure to use the black ground clip (supplied with the U4203A Flying Lead Probe Set) and orient the leads so that the black clip is connected to one of the SMA/Flying Lead connector's ground pins!

- 3 Connect the Pod 1 U4203A Flying Lead Probe Set's CLK (NOT) lead to the SMA/Flying Lead connector at the pulse generator's Channel 1 OUTPUT (NOT). Again, be sure to use the black ground clip and orient the leads so that the black clip is connected to ground.

- 4 Connect the Pod 1 U4203A Flying Lead Probe Set's bits 2 and 10 to the SMA/Flying Lead test connector's pin strip connector at the pulse generator's Channel 2 OUTPUT.

- 5 Connect the Pod 1 U4203A Flying Lead Probe Set's bits 6 and 14 to the SMA/Flying Lead test connector's pin strip connector at the pulse generator's Channel 2 OUTPUT (NOT).

### Test the U4154B Module

The following sections explain how to test the maximum state data rate.

- 1 Record the logic analyzer's model and serial number in the Performance Test Record (see page 45). Record your work order number (if applicable) and today's date.

- 2 Record the test equipment information in the "Test Equipment Used" section of the Performance Test Record.

- 3 Turn on the AXIe chassis.

### NOTE

Before testing the performance of the module, warm-up the logic analyzer and the test equipment for 30 minutes.

- a Plug in the power cord to the power connector on the rear panel of the AXIe chassis.

- b Press the ON/Standby button on the front panel of the chassis to power on the logic analyzer.

- 4 After the AXIe chassis is fully booted, power on the host PC if it is not part of the AXIe chassis.

- 5 Start the Keysight Logic and Protocol Analyzer application if it is not started already.

### Configure the Logic Analysis System

- 1 In the *Keysight Logic and Protocol Analyzer* application, choose **File→New**. This puts the logic analysis system into its initial state.

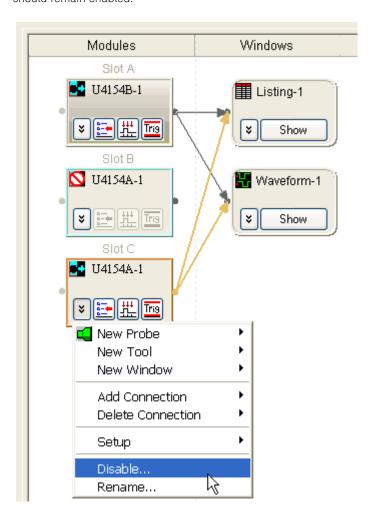

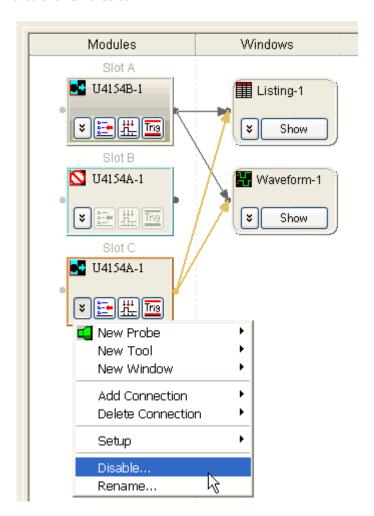

- 2 Disable all logic analyzers other than the analyzer under test.

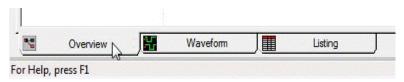

- a Select the **Overview** tab at the bottom of the main window.

b Click on each unused logic analyzer and select disable. Only the logic analyzer to be tested should remain enabled.

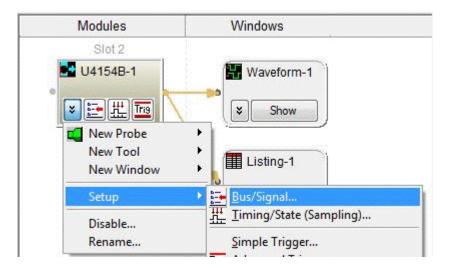

- 3 Set up the bus and signals:

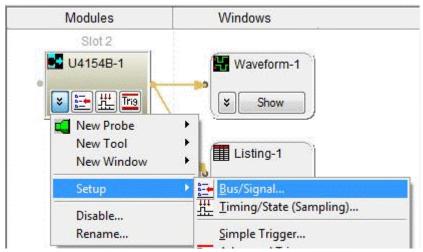

- a In the Overview window, select **Setup**→**Bus/Signal...** from the logic analyzer's drop-down menu.

NOTE

The E5382A probe must be connected to the logic analyzer pod as described on page 27.

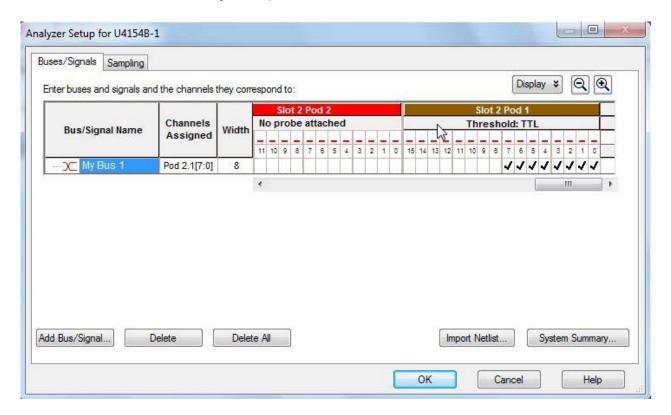

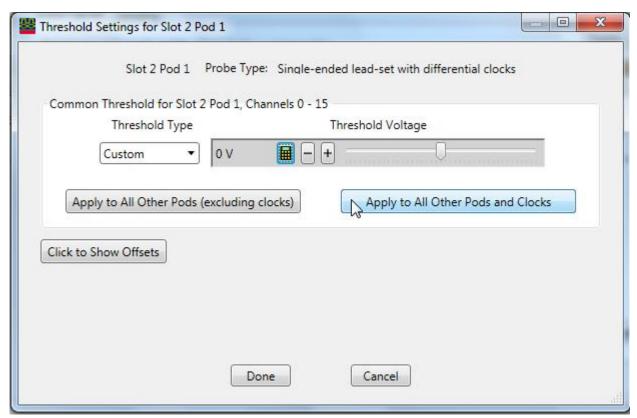

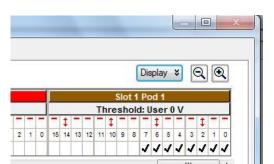

b In the Analyzer Setup window, choose the **Threshold** button for Pod 1.

The Threshold Settings window appears.

c Set the threshold value for Pod 1 of the logic analyzer to **0 V**. Click **Apply to All Other Pods**. Then, click **Done** to close the dialog.

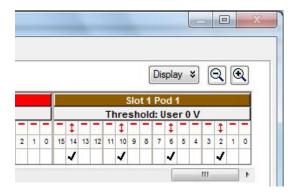

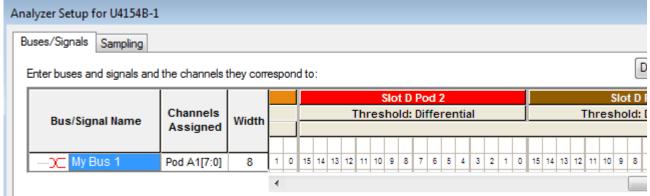

d The activity indicators now show activity on the channels that are connected to the pulse generator. Un-assign all channels. You can do this quickly by clicking on the left-most check

mark and dragging to the right across all of the other check marks.

e Click to select channels 2, 6, 10, and 14 as shown in the picture above.

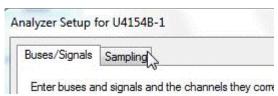

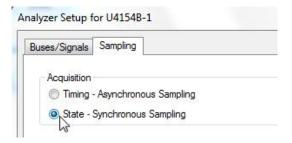

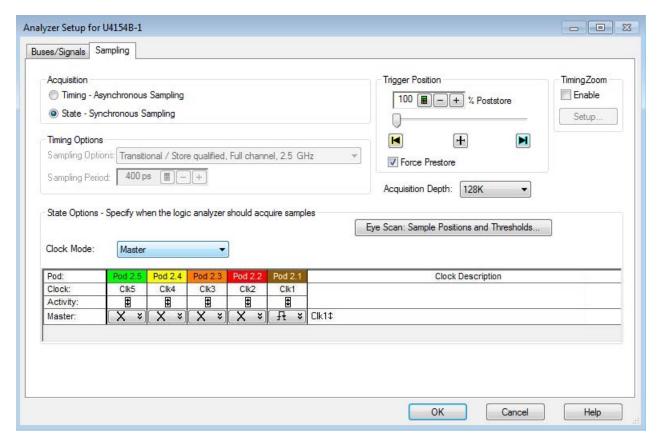

- 4 Select the State sampling mode and set the State Clock options:

- a Select the Sampling tab of the Analyzer Setup window.

b Select State - Synchronous Sampling.

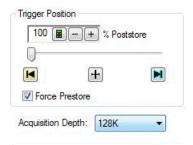

- 5 Set the trigger position and acquisition memory depth:

- a Set the Trigger Position to 100% Poststore.

- b Set the Acquisition Depth to 128K.

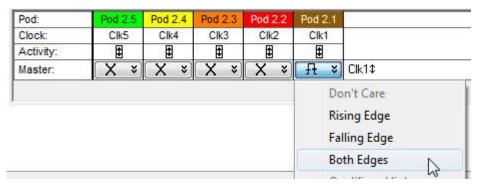

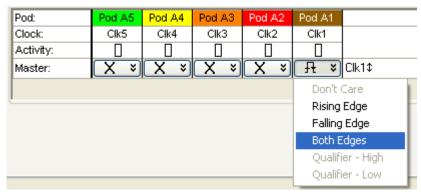

c Set Clk1 to Both edges clocking. The following screen displays this state clock setting.

6 Hit **OK** to close the setup window.

#### Determine maximum clock rate

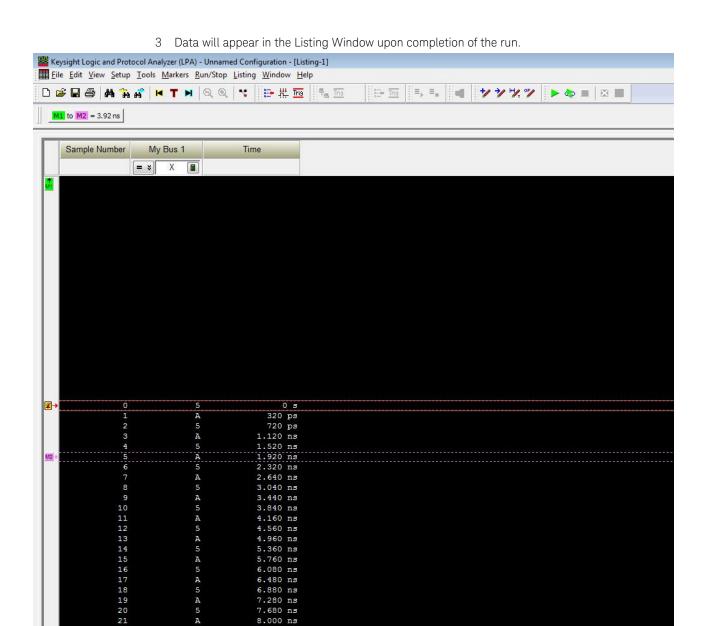

- 1 Switch to the Listing window by selecting the **Listing** tab at the bottom of the main window.

- 2 Click the **Run Repetitive** toolbar button to start a repetitive run on the logic analyzer for acquiring data repeatedly.

- Acquired data will start appearing in the Listing window.

- 3 Start increasing the frequency on the pulse generator by 1 MHz increments while simultaneously observing the logic analyzer data acquisition status.

- 4 When the logic analyzer displays an error that the data could not be displayed, decrease the pulse generator frequency by 1 MHz.

- Close the displayed error dialog by clicking **OK**.

- 6 Wait for logic analyzer to complete 100 acquisitions at the new pulse generator frequency without displaying any error. If an error is displayed, decrease the pulse generator frequency by 1 MHz and then again wait for 100 acquisitions at this new frequency without any error. Repeat this step until you get 100 acquisitions without any error display.

- 7 Click the **Stop** toolbar button to stop the data acquisition.

### Determine PASS/FAIL for the Pulse Generator Frequency test

If you get 100 acquisitions without any error display at a pulse generator frequency (including uncertainty) greater than 1250 MHz, then the logic analyzer passes this portion of the test. For example, a frequency of 1280 MHz - 2% uncertainty = 1254.4 MHz indicates a PASS result for the test. Record PASS/FAIL result of this test in the "Pulse Generator Frequency Test" section of the Performance Test Record (page 45).

### NOTE

If any of tests described later in this chapter fail, decrease the pulse generator frequency by 1 MHz and wait for logic analyzer to complete 100 acquisitions at this new pulse generator frequency without displaying any error. Repeat this step until you get 100 acquisitions without any error display.

### Final pulse generator frequency

If the remaining tests described in this chapter PASS, record the final pulse generator frequency in the "Final Pulse Generator Frequency" section of the Performance Test Record (page 45). Recording this final frequency provides a traceable measurement that is expected to be unique for each U4154B Logic Analyzer module.

Adjust sampling positions using Eye Scan

- 1 Open the sampling setup window.

- 2 Select the Eye Scan: Sample Positions and Thresholds... button.

The Eye Scan - Sample Positions and Threshold Settings dialog will appear.

3

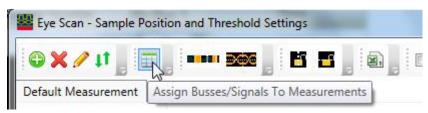

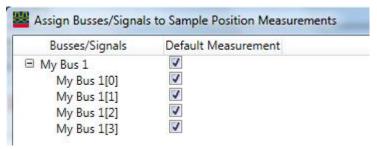

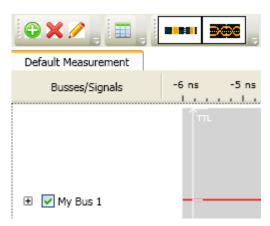

3 Select the Assign Busses/Signals Dialog.

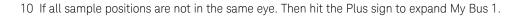

4 In the Busses/Signals section of the dialog, ensure that the check box next to "My Bus 1" is checked and the 4 data bits 0-3. Hit **0K**.

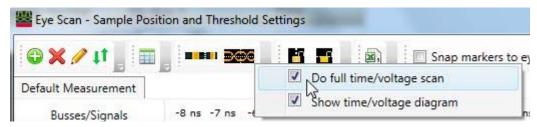

5 Select the Full time/voltage scan dialog box.

6 In the dialog box, set Do full time/voltage scan and Show time/voltage scan.

7 Run Eye Scan by hitting the **Run This Measurement** button.

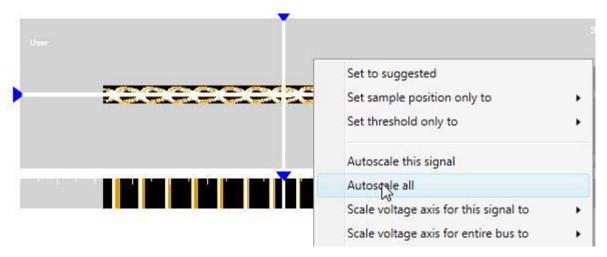

8 If the scan does not fill the scan area, right click in the scan area and select **Autoscale all**.

The waveform should now fill the Eye Scan area.

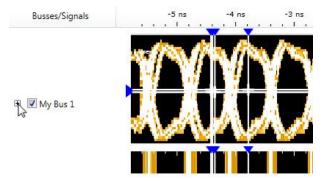

Use the mouse to grab the bits that are not in the eye near -4.5 ns. Drag them into the correct eye.

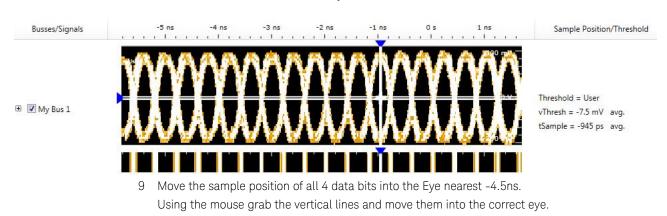

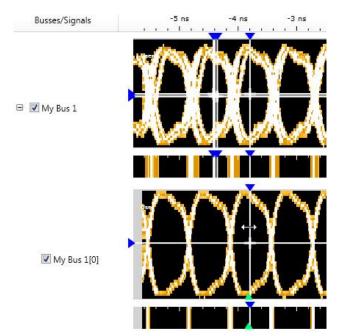

11 After all bit sample positions are in the correct eye. Right click in the My Bus 1 Scan area and select **Set to Suggested**.

Busses/Signals -5 ns -4 ns -3 ns

12 After setting to suggested all bits should be centered in their own eye near -4.5 ns.

#### Test Pod 1

The steps that follow include pass/fail criteria.

#### Determine PASS/FAIL (1 of 2 tests) Eye Scan Location

- 1 PASS/FAIL: If an eye exists near -4.5 ns for every bit, and Eye Scan places the sample position in the eye for each bit, then the logic analyzer passes this portion of the test. Record the result in the "Eye Scan locates an eye for each bit" section of the Performance Test Record (page 45).

- 2 If an eye does not exist near -4.5 ns for every bit or Eye Scan cannot place the blue bar in the eye, then the logic analyzer fails the test. Record the result in the "Eye Scan locates an eye for each bit" section of the Performance Test Record (page 45).

#### Close the Eye Scan and Analyzer Setup Windows

- 1 Select **OK** to close the Eye Scan Sample Positions and Threshold Settings dialog.

- 2 Select **OK** to close the Analyzer Setup window.

#### Configure the markers

Data must be acquired before the markers can be configured. Therefore, you need to run the analyzer to acquire data.

- 1 Switch to the Listing window by selecting the **Listing** tab at the bottom of the main window.

- 2 Select the Run icon

8.000 ns 8.400 ns

If the data values are not "A"s and "5"s, you may need to set the sampling positions in different eyes.

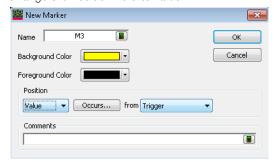

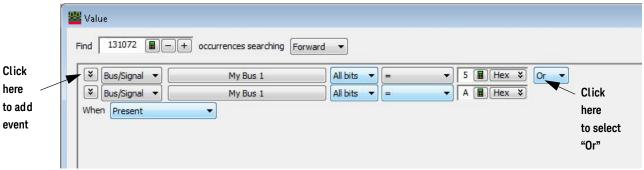

4 From the Main Menu, choose Markers→New.

- a You can accept the default name for the new marker.

- b Change the Position field to Value.

c Select the Occurs... button and create the marker setup shown below.

- 5 In the Value window, select the **Properties...** button.

- 6 In the Value Properties window, select **Stop repetitive run** when value **is not found**.

- 7 Select **OK** to close the marker Value Properties window.

- 8 Select **OK** to close the marker Value window. The system will search the display for the occurrences specified.

- 9 Select **OK** to close the New Marker window.

#### Determine PASS/FAIL (2 of 2 tests)

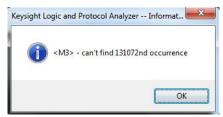

Pass/Fail Point: The Listing window is set up to search for the appropriate number of A's and 5's in the acquisition. If the logic analyzer does not detect the correct number of A's and 5's, an error window will appear.

1 Select the Run Repetitive icon . Let the logic analyzer run for about one minute. The analyzer will acquire data and the Listing Window will continuously update.

If the "can't find occurrence" window appears, then the logic analyzer fails the test.

Check your test setup. If the failure is not the result of a problem with the test setup, record the failure in the "Maximum State Data Rate" section of the Performance Test Record.

# NOTE

Be sure that the black ground clip is making good contact with the ground pin on the test connector.

2 After about one minute, select the **Stop** button to stop the acquisition.

If the "can't find occurrence" window does not appear, then the analyzer passes the test. Record "Pass" in the "Maximum State Data Rate" section of the Performance Test Record.

#### Test Pod 2

- 1 Disconnect the U4203A Flying Lead Probe Set Pod1 from channel 2 of the 81134A pulse generator output (Bits 2, 6, 10, 14). Leave the Pod 1 clock connected to channel 1.

- 2 Connect the probe set from Pod 2 of logic analyzer to the pulse generator channel 2 outputs. (The clock input on Pod 1 remains the clock input when testing Pod 2.)

- · Bits 2 & 10 to Channel 2 Output

- Bits 6 & 14 to Channel 2 Output (not)

- 3 In the Overview window, select **Setup** → **Bus/Signal...** from the analyzer's drop-down menu.

- 4 Scroll to the right and unassign all Pod 1 bits.

- 5 Set the Pod 2 threshold to 0 V (just as you did for Pod 1 on Set the threshold value for Pod 1 of the logic analyzer to).

6 Assign bits 2, 6, 10, and 14 of Pod 2.

7 Adjust the sampling positions using Eye Scan. Set sample position near -4.5 ns. Realign any stray channels if necessary.

In Eye Scan - Open Assign Busses and assign 4 bits to My Bus.

- 8 Determine pass or fail (1 of 2 tests). See page 39.

- 9 Select **OK** to close the "Analyzer Setup" window.

- 10 Switch to the Listing window by selecting the Listing tab at the bottom of the main logic analyzer window.

- 11 Select the Run Repetitive icon

- 12 Determine pass or fail (2 of 2 tests). See page 42.

#### Test Pods 3

- 1 Disconnect the U4203A Flying Lead Probe Set Pod2 from channel 2 of the 81134A pulse generator output. Leave the Pod 1 clock connected to channel 1.

- 2 Connect a second U4203A to the Pod 3 / 4 connector on the Logic Analyzer frame.

- 3 Set the Pod 3 threshold to 0 V. Apply to All Other Pods and Clocks (just as you did for Pod 1 on Set the threshold value for Pod 1 of the logic analyzer to).

- 4 Assign bits 2, 6, 10, and 14 of Pod 3.

5 Adjust the sampling positions using Eye Scan. Set sample position near -4.5 ns. Realign any stray channels if necessary.

In Eye Scan - Open Assign Busses and assign 4 bits to My Bus.

- 6 Determine pass or fail (1 of 2 tests). See page 39.

- 7 Select **OK** to close the "Analyzer Setup" window.

- 8 Switch to the Listing window by selecting the **Listing** tab at the bottom of the main logic analyzer window.

- 9 Select the Run Repetitive icon

- 10 Determine pass or fail (2 of 2 tests). See page 42.

#### Other Pods

Repeat the above steps for testing pods 4 to 8. Upon completion, the logic analyzer is completely tested.

#### Conclude the State Data Rate Tests

Do the following steps to properly shut down the logic analyzer session after completing the state mode tests.

- 1 End the test.

- a From the Main Menu, choose  ${\bf File} \rightarrow {\bf Exit}$ . At the dialog "Do you want to save the current configuration?" select  ${\bf No}$ .

- b Disconnect all cables and adapters from the pulse generator.

# Performance Test Record

| LOGIC ANALYZER MODEL NO.: U4154B |                                               |  |

|----------------------------------|-----------------------------------------------|--|

| Logic Analyzer Serial No.        | Work Order No.                                |  |

| Date:                            | Recommended Test Interval - 2 Year/4000 hours |  |

|                                  | Recommended next testing:                     |  |

| TEST EQUIPMENT USED                   |

|---------------------------------------|

| Pulse Generator Model No.             |

| Pulse Generator Serial No.            |

| Pulse Generator Calibration Due Date: |

# MEASUREMENT UNCERTAINTY

Clock Rate

Pulse Generator Frequency Accuracy: 81134A: ±0.005% of setting. 2% = uncertainty + at least 1% test margin.

Base option: (should be tested to the Option 02G level at the service

center)

Option 02G: 1250 MHz + 2% = 1275 MHz

| TEST RESULTS                                  |                                                     |                                                       |  |

|-----------------------------------------------|-----------------------------------------------------|-------------------------------------------------------|--|

| Logic Analysis System Self-Tests (Pass/Fail): |                                                     |                                                       |  |

| Performance Test: Maximum State Data Rate:    |                                                     |                                                       |  |

| Pulse Generator Settings                      | Freq: Option 02G: 1250 MHz + 2% = 1275 N            | Freq: Option 02G: 1250 MHz + 2% = 1275 MHz            |  |

|                                               | Square wave.                                        |                                                       |  |

| Pulse Generator Frequency Test (Pass/Fail)    |                                                     |                                                       |  |

| Final Pulse Generator Frequency               |                                                     |                                                       |  |

| Test Criteria                                 | Test 1 of 2<br>Eye Scan locates an eye for each bit | Test 2 of 2<br>Correct number of occurrences detected |  |

| Pod 1 Results (pass/fail):                    |                                                     |                                                       |  |

| Pod 2 Results (pass/fail):                    |                                                     |                                                       |  |

| Pod 3Results (pass/fail):                     |                                                     |                                                       |  |

| Pod 4 Results (pass/fail):                    |                                                     |                                                       |  |

| Pod 5 Results (pass/fail):                    |                                                     |                                                       |  |

| TEST RESULTS               |  |

|----------------------------|--|

| Pod 6 Results (pass/fail): |  |

| Pod 7 Results (pass/fail): |  |

| Pod 8 Results (pass/fail): |  |

Keysight U4154B Logic Analyzer Service Guide

# 4 Calibrating

Calibration Strategy / 48

This chapter gives you instructions for calibrating the U4154B logic analyzer.

#### 4 Calibrating

# Calibration Strategy

The U4154B logic analyzer does not require any periodic adjustments or calibration by the user to ensure operational accuracy.

However, Keysight recommends that performance of the U4154B logic analyzer be tested against its specifications at two-year intervals. This testing is required in order to obtain calibration certification.

You can refer to Chapter 3, "Testing U4154B Performance to find detailed information on how to test the performance of the U4154B logic analyzer.

# 5 Troubleshooting

To use the flowcharts / 50

To run the self tests / 55

Self-Test Descriptions / 52

To exit the test system / 55

To test the cables / 56

This chapter provides instructions for troubleshooting a U4154B module that is not operating correctly.

The troubleshooting consists of flowcharts, self-test instructions, and a cable test.

If you suspect a problem, start at the top of the first flowchart. During the troubleshooting instructions, the flowcharts will direct you to perform the self-tests or the cable test.

The service strategy for the U4154B module is the replacement of defective assemblies. You can return this module to Keysight Technologies for all service work, including troubleshooting. Contact your nearest Keysight Technologies Sales Office for more details.

**CAUTION**

Electrostatic discharge can damage electronic components. Use grounded wrist-straps and mats when you perform any service to this instrument or to the modules in it.

#### To use the flowcharts

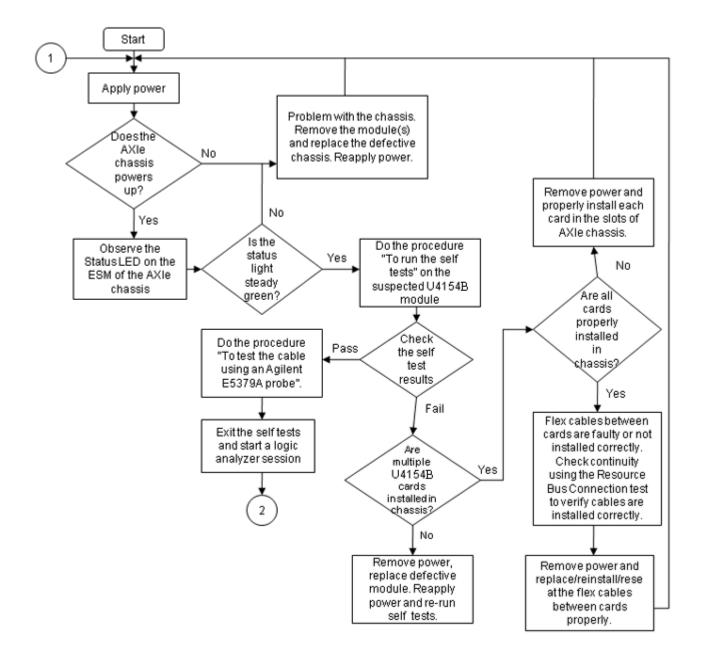

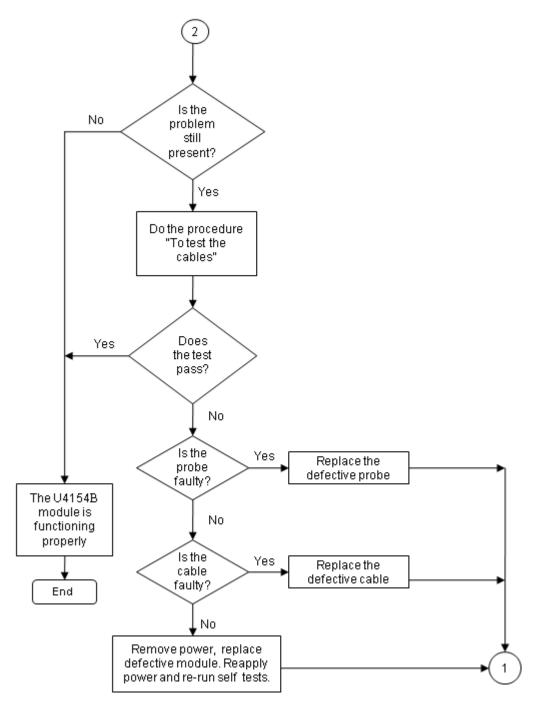

Flowcharts are the primary tool used to isolate defective assemblies. The flowcharts refer to other tests to help isolate the problem. The circled numbers on the charts indicate connections with the other flowchart. Start your troubleshooting at the top of the first flowchart.

Figure 3 Troubleshooting Flowchart 1

Figure 4 Troubleshooting Flowchart 2

## Self-Test Descriptions

The self-tests for U4154B logic analyzer identify the correct operation of major functional areas in the U4154B module.

#### PC Board Revision Test

This tests that the FPGA is communicating with the backplane and that the board under test is a supported version.

#### Interface FPGA Version Test

This test verifies that the FPGA program is a version that the software can use. This is necessary because new features will be added to the U4154B that will require both new software and new FPGA bits

#### Interface FPGA Register Test

The purpose of this test is to verify that the backplane interface can communicate with the backplane FPGA. The FPGA must be working before any of the other circuits on the board will work. Also, the FPGA generates the board ID code that is returned to identify the module and slot.

#### FPGA to FPGA Communication Test

This test is only run if there are two or more U4154B logic analyzer cards installed in a chassis and connected together with the flex cables. The purpose of this test is to verify that the FPGAs can drive and receive the signals correctly.

#### SPI Bus Communication Test

The purpose of this test is to verify communications over the SPI bus from the Interface FPGA to various devices attached to the SPI bus.

#### **EEPROM Test**

The purpose of this test is to verify:

- · The address and data paths to the EEPROM.

- That each cell in the EEPROM can be programmed high and low.

- · That individual locations can be independently addressed.

- · The EEPROM can be block erased.

#### Probe ID Read Test

The purpose of this test is to verify that the Probe ID values can be correctly read and to verify the functionality of the Digital to Analog Converter by testing the two Probe ID DAC outputs at various voltage levels.

#### Chip Registers Read/Write Test

The purpose of this test is to verify that each bit in each register of the Analysis chip can be written with a 1 and 0 and read back again. The test also verifies that a chip reset sets all registers to their reset condition (all 0s for most registers).

#### Freq Synth Lock Detect Test

This test determines if all the voltage-controlled oscillators (VCOs) are working properly.

#### Acquisition Chip BIST Test

Tests the Timing Zoom memory and other internal memories on the acquisition chip.

#### Resource Bus Connection Test

This test is only run if there are two or more U4154B logic analyzer cards in adjacent slots in a chassis.

This test verifies whether or not the flex cables are squarely and firmly inserted into the connectors.

#### Comparator Programming Test

The purpose of this test is to verify the programming path to each of the comparators.

#### Comparator/DAC Test

This test is executed only if all probes are detached.

This test uses the pod, bonus, and calibration DACs, the calibration oscillator (implemented in the interface FPGA), the comparators, the connections between the comparators and the Analysis chip, and the activity indicators in the Analysis chip. We verify that we can use the DACs to control the data input to the comparators. We verify that each comparator data channel produces output. We verify that each comparator output is connected to each ASIC data input.

#### Comparator Delay Test

The comparator delay test verifies the integrity of all the delay line elements for each delay line in the comparators. Each delay line consists of 11 delay elements. When set for maximum delay, all 11 elements are connected in series. If any element is faulty, then data will not propagate through the comparator. If this is the only test failing, then it is almost certainly a bad comparator.

#### Comparator Zero-Hold Cal Test

Tests the delay elements for each delay line in the comparators. It tests that each delay line can increase its delay in a linear way through a range of delay values.

#### Comparator Calibrations Test

The purpose of this test is to verify that each of the comparator one-time calibrations can successfully be performed. This verifies that all of the calibration circuitry and components are within the tolerance limits required for proper calibration. This test is executed only if all probes are detached.

#### Acquisition Memory Write/Read Test

This test checks that each acquisition chip can write data to DDR acquisition memory and read the same data back.

#### Acquisition Memory Cell Test

Tests every bit of the DDR acquisition memory. The test verifies that every bit can be written to 0 and written to 1 and read back accurately.

#### 5 Troubleshooting

#### ATB (AXIe Trigger Bus) Test

This test verifies the ATB signal connections between the acquisition chips, the interface FPGA and the two 8-bit transceiver chips.

#### To run the self tests

You can run self tests on the U4154B module to verify if the module is operating correctly. Before running self tests, ensure that:

- you have connected all the hardware components for the U4154B module

- created a logical module for U4154B in the Keysight Logic Analyzer application.

- · disconnected all probes from the logic analyzer module.

You use the **Analysis System Self Tests** window to run self tests. Refer to the topic "Perform the Self-Tests" on page 19 to know how to run these tests.

If all tests did not pass, refer to "To use the flowcharts" on page 50.

## To exit the test system

1 Close the self-test window. No additional actions are required.

#### To test the cables

This test allows you to functionally verify U4201A logic analyzer cables and Keysight E5379A probes.

Table 4 Equipment Required to Test Cables

| Equipment           | Critical Specification | Recommended Part |

|---------------------|------------------------|------------------|

| Stimulus Board      | No Substitute          | 16760-60001      |

| Differential Probes | No Substitute          | E5379A (Qty 2)   |

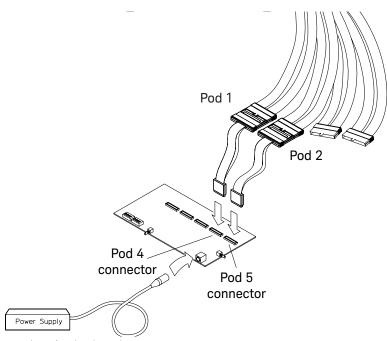

- 1 Connect the U4154B logic analyzer to the stimulus board.

- a Connect the Keysight E5379A 90-pin differential probes to the logic analyzer cable (also called "Pods") to be tested. Start with Pods 1 and 2.

- b Connect the E5379A probe from logic analyzer Pod 1 to connector "Pod 4" on the stimulus board

- c Connect the E5379A probe from logic analyzer Pod 2 to connector "Pod 5" on the stimulus board.

- d Connect the stimulus board power supply output to the stimulus board power supply connector J82.

- e Plug in the stimulus power supply to line power. The green LED DS1 should illuminate showing that the stimulus board is active.

- 2 Set up the stimulus board

- a Configure the oscillator select switch S1 according to the following settings:

- S1 0 (Off).

- S2 1 (On).

- S3 0 (Off).

- · Int.

- b Configure the data mode switch S4 according to the following settings:

- Even.

- Count.

- c Press the Resynch VCO button, then the Counter RST (Counter Reset) button.

- 3 In the *Keysight Logic Analyzer* application, choose **File→New**. This puts the logic analysis system into its initial state.

- 4 Disable all analyzers except the one being tested. This simplifies the instructions and makes module initialization faster.

- a Select the **Overview** tab at the bottom of the main window.

b Click on each unused logic analyzer and select disable. Only the logic analyzer to be tested should remain enabled.

- 5 Set up the bus:

- a In the **Overview** window, select **Setup -> Bus/Signal...** from the module's drop-down menu.

b Scroll if necessary to view the pods you are testing.

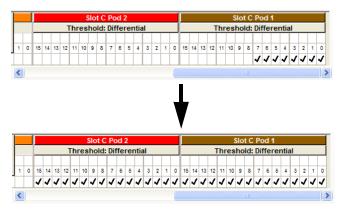

c Verify that the pod threshold buttons say "Threshold: Differential", as shown above. If they don't, make sure the correct probes (E5379A) are attached to pods 1 and 2. The threshold is set to Differential automatically when E5379A probes are attached.

d Channels 7 through 0 are already assigned by default. Assign pod 2 channels 15 through 0 and pod 1 channels 15 through 8 by clicking and dragging from the left-most channel box to the right-most channel box. Your display should look like the lower picture when you are done.

- 6 Select the State sampling mode and set the State Clock options:

- a Select the **Sampling** tab of the Analyzer Setup window.

- b Select State Synchronous Sampling.

- c For State Clock, select Pod A1 Clock and Both edges.

- 7 Set the trigger position and acquisition memory depth:

- a Set the Trigger Position to 100% Poststore.

- b Set the Acquisition Depth to 8K.

- 8 Adjust sampling positions:

- a Select the **Eye Scan: Thresholds and Sample Positions** button. The Eyescan Sample Positions dialog will appear.

- b In the "Busses/Signals" section of the Eyescan Sample Positions dialog, make sure the check box next to "My Bus 1" is checked.

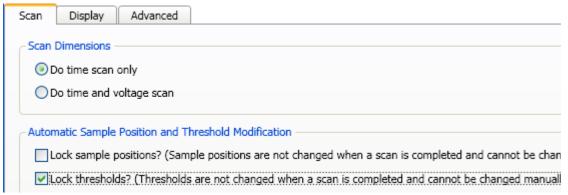

c Click **Edit** and select the **Do time scan only** option as the scan dimension and the **Lock Thresholds** checkbox.

d Select the Run This Measurement button in the Eyescan - Sample Positions dialog.

- e Make sure the sampling positions are set properly, and re-align any stray channels if necessary.

- f Select **OK** to close the **Eyescan Sample Positions** window.

- g Select **OK** to close the **Analyzer Setup** window.

- 9 Switch to the Listing window by selecting the Listing tab at the bottom of the main window.

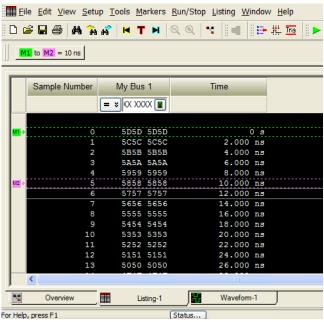

- 10 Select the Run icon . The listing should look similar to the figure below when you scroll down a bit.

Scroll down at least 256 samples to verify the data. **My Bus 1** shows four 8-bit binary counters decrementing by 1. If the listing does not look similar to the figure, there is a possible problem with the cable or probe. Cause for cable test failures include:

- Open channel.

- Channel shorted to a neighboring channel.

- Channel shorted to either ground or a supply voltage.

If the test data is not correct, then perform the following step to isolate the failure.

- 11 Verify the failure:

- a Swap the E5379A probes so that the pod 1 cable remains connected to the stimulus board's pod 4 connector and the pod 2 cable remains connected to the stimulus board's pod 5 connector just using different probes.

- b Select the **Run** icon .

If the failure is the same (that is, the error follows the cable) then the cable is faulty.

If the failure switches pods (that is, the error follows the E5379A probe) the probe is faulty.

- 12 Repeat the cable test for pods 3 and 4:

- a Connect the logic analyzer's pod 3 cable to the stimulus board's pod 4 connector.

- b Connect the logic analyzer's pod 4 cable to the stimulus board's pod 5 connector.

- c In the **Busses/Signals** tab of the Analyzer Setup window, assign the pod 3 and 4 channels to "My Bus 1".

- d In the Sampling tab of the Analyzer Setup window, for State Clock, select Both edges.

- e Adjust sampling positions.

- f Select the **Run** icon . In the Listing window, check at least 256 samples for failures; if necessary, verify any failures by swapping the E5379A probes.

- 13 Repeat the cable test (step12) for pod pairs 5 and 6 and 7 and 8 connecting the odd pod cable to the stimulus board's pod 4 connector and the even pod cable to the stimulus board's pod 5 connector:

Return to the troubleshooting flowchart.

# 6 Returning and Replacing a U4154B Module or its cables

To remove the U4154B module / 64

To remove the logic analyzer cable / 64

To install the U4201A logic analyzer cable / 64

To replace the circuit board / 65

To return the U4154B module or cable for Repair/Exchange / 66

This chapter contains the instructions for removing and replacing the U4154B logic analyzer module, and the probe cables of the module as well as the instructions for returning defective parts to Keysight Technologies.

CAUTION

Turn off the AXIe chassis before installing, removing, or replacing a module in the chassis.

The enclosure surface of the U4154B module may become hot during use. If you need to remove the module, first power down the AXIe chassis, allow the module to cool, and then pull the module out of the chassis.

**CAUTION**

Electrostatic discharge can damage electronic components. Use grounded wriststraps and mats when performing any service to this module.

#### 6

#### To remove the U4154B module

If the U4154B module or any of its parts are faulty, remove the faulty module from the AXIe chassis, return it to Keysight Technologies for repair/exchange. On getting a replaced module, install it in the AXIe chassis.

Instructions for removing or installing the module into the AXIe chassis can be found in the AXIe based Logic Analysis & Protocol Test Modules Installation Guide.

# To remove the logic analyzer cable

There are four cables for each U4154B logic analyzer module. One cable is for pods 1 and 2, the other cable is for pods 3 and 4, and so on till pod 8 of the U4154B module. The following figure displays three cables attached to pods 3, 4, 5, 6, 7, and 8 of the U4154B module.

To remove the logic analyzer cable:

- 1 Remove power from the AXIe chassis

- a Turn off the chassis.

- b Disconnect the power cord.

- 2 Remove the logic analyzer pod cable.

- a Remove the two thumb screws that secure the logic analyzer cable to the pods in the front panel of the module.

- b Disengage thumb screws completely from the module.

- 3 Pull the cable straight out from the front panel of the module.

If the logic analyzer cable is faulty, return it to Keysight Technologies for repair/exchange or order a new cable which is available as a replaceable part, and follow the next procedure to install the replaced logic analyzer cable.

# To install the U4201A logic analyzer cable

Perform the following steps to connect the new/replaced logic analyzer cable to the front panel of the U4154B module.

- 1 Attach cable connector to the pod input on the front panel of the module.

- 2 Tighten the two thumb screws on both sides of the U4201A cable to retain the cable tightly inside the relevant pod input. Do not over tighten the thumb screws. Hand tightening is recommended or maximum torque of 3in-lb.

# To replace the circuit board

If the circuit board of the U4154B module is found faulty, perform the following steps to get it repaired/replaced.

- 1 Remove the logic analyzer cables using the "To remove the logic analyzer cable" procedure on page 64.

- 2 Remove the U4154B module with the faulty circuit board from the AXIe chassis. Refer to the AXIe based Logic Analysis & Protocol Test Modules Installation Guide to learn how to remove the module from chassis.

- 3 Send the U4154B module to Keysight Technologies to repair or replace the faulty circuit board with a new circuit board.

# To return the U4154B module or cable for Repair/Exchange

Before returning the U4154B module or a logic analyzer cable to Keysight Technologies, contact your nearest Keysight Technologies Sales Office for additional details. Information on contacting Keysight can be found at <a href="https://www.keysight.com">www.keysight.com</a>.

- 1 Write the following information on a tag and attach it to the module/cable.

- · Name and address of owner.

- · Model number.

- · Serial number.

- · Description of service required or failure indications.

- 2 Remove accessories from the module.

Only return accessories to Keysight Technologies if they are associated with the failure symptoms.

3 Package the module/cable.

You can use either the original shipping containers, or order materials from an Keysight Technologies sales office.

# CAUTION

For protection against electrostatic discharge (ESD), package the module in ESD-safe material.

4 Seal the shipping container securely, and mark it FRAGILE.

# Index

| Α                                                                                                                                                                                                                                                   | clean, 15<br>remove, 64                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| accessories, 10 acquisition, 52                                                                                                                                                                                                                     | test, 15 multi-card module test, 18                                                                                                                                            |

| С                                                                                                                                                                                                                                                   | 0                                                                                                                                                                              |

| cable install, 64 remove, 64 test E5379A cable, 56 calibrating see also testing performance calibration, 47 strategy, 48 characteristics, 12 chassis, 10 circuit board replace, 65 clean module, 15 cleaning the instrument, 3 connectors, test, 21 | one-card module configure, 14 test, 18 operating environment, 13  P performance testing, 17 probing accessories, 10  R                                                         |

| environment operating, 13 equipment test, 18 eye finder adjusting, 35 eye scan, 35                                                                                                                                                                  | remove logic analyzer cable, 64 module, 64 replace circuit board, 65 replacing module, 63 return module, 66                                                                    |

| F                                                                                                                                                                                                                                                   | self-test, 19,55<br>description, 52<br>set up                                                                                                                                  |

| features, 4 flowcharts, 50                                                                                                                                                                                                                          | one-card module, 14 specifications, 11                                                                                                                                         |

| G                                                                                                                                                                                                                                                   | Т                                                                                                                                                                              |

| general information, 9                                                                                                                                                                                                                              | test connectors, 21                                                                                                                                                            |

| I install logic analyzer cable, 64 instrument, cleaning the, 3  M module                                                                                                                                                                            | E5379A cables, 56 equipment, 18 interval, 18 module, 15 multi-card module, 17 one-card module, 17 performance record, 45 record description, 18 self-test, 19, 55 strategy, 17 |

|                                                                                                                                                                                                                                                     | onatogy, 17                                                                                                                                                                    |

testing performance, 17

equipment, 18

interval, 18

multi-card module, 18

test record, 45

troubleshooting, 49

Index