FEBRUARY 1995

VOLUME V NUMBER 1

#### IN THIS ISSUE . . .

The LTC<sup>®</sup> 1410 Converts Twelve Bits at 1.25MSPS ...... 1 Dave Thomas

Editor's Page ...... 2 Richard Markell

LTC in the News ...... 2

DESIGN FEATURES New LTC1266 Switching Regulator Provides High Efficiency at 10A Loads...... 3 Greg Dittmer

The LTC1265: a New, Highefficiency Monolithic Buck Converter ...... 10 San-Hwa Chee

The LT<sup>®</sup> 1175: Negative, Low-Dropout Regulator ..... 13 Carl Nelson

**Power Factor Correction ... 17** Dale Eagar

**Power for Pentium™ ...... 19** Craig Varga

PCMCIA Socket Voltage Switching Matrix with SafeSlot<sup>™</sup> Protection ...... 22 Doug La Porte

DESIGN INFORMATION LTC's RS232 Transceivers for DTE-DCE Switching .... 24 Gary Maulding

#### **DESIGN IDEAS**

|                            | 29-36 |

|----------------------------|-------|

| (complete list on page 29) |       |

|                            |       |

New Device Cameos ...... 39

## The LTC1410 Converts Twelve Bits at 1.25MSPS

#### Introduction

Until now, designers of high-speed data acquisition systems have had to make some tough compromises when picking 1MSPS 12-bit A/D converters. The parts with the best performance were hybrids in large packages, which consumed 1W or more and cost \$100.00 or more. A few manufactures offered monolithic solutions, but they didn't perform as well as hybrids. Some of the monolithic parts had poor AC performance but good DC performance, whereas others had good AC and inferior DC performance. Now, LTC has a monolithic, 1.25MSPS 12-bit ADC with the performance of the best hybrids but with the power, size, and cost of a monolithic part. Some of the key features of this new device include:

- □ 1.25 MSPS throughput

- □ Low-power—150mW typical from 5V supplies

- □ NAP and SLEEP power-shutdown modes

- □ Small package—28-pin SSOP

Not only does this device match or beat the performance of expensive hybrids, it also offers some new features they never had, like true differential inputs and two power shutdown modes. These features can help improve the performance of current data-acquisition systems and open up new applications that were not previously possible because of high power consumption.

## by Dave Thomas

#### High-Accuracy Conversions: AC or DC

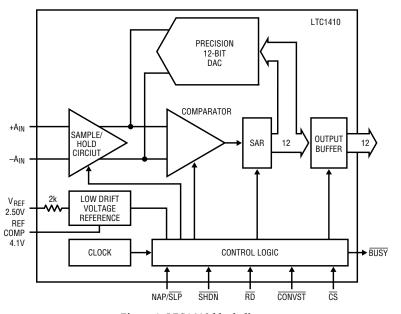

Figure 1 is a block diagram of the LTC1410. A high-performance differential sample-and-hold circuit combined with an extremely fast, successive-approximation ADC and an on-chip reference deliver a previously unattainable combination of AC and DC performance. A digital interface allows easy connection to microprocessors, FIFOs, or DSPs.

The DC specifications include a 0.8LSB maximum differential linearity error and 0.5LSB maximum integral linearity error guaranteed over temperature. The gain of the ADC is held nearly constant over temperature with an on-chip 10ppm/°C curvature-corrected bandgap reference.

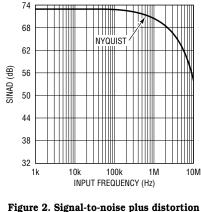

The sample-and-hold circuit sets the dynamic performance of the ADC. The LTC1410 has a wide bandwidth and very low distortion differential sample-and-hold. Specifications include total harmonic distortion of -84dB for a 625kHz input and an input bandwidth of 30MHz for the sample-and-hold.

#### High-Impedance Inputs Speed Data Acquisition

High speed ADCs are often used to sample many different channels in multiplexed systems. The LTC1410 is well suited to these applications. The high-impedance inputs are easy to switch through a MUX without continued on page 37

⊥ , LTC and LT are registered trademarks and SafeSlot is a trademark of Linear Technology Corporation. Pentium is a trademark of Intel Corporation.

## LT EDITOR'S PAGE

## **Remembering the Six-Transistor Radio**

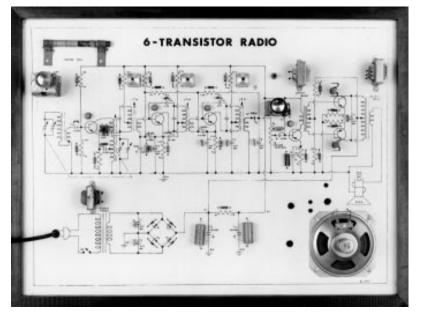

Figure 1. The classic six-transistor radio

How many years has it been since the demise of the six-transistor radio? How many of us at LTC remember our electronics class in junior high school or even high school? I have fond memories of walking around the neighborhood with my crystal radio, testing water pipes, fences, metalframed buildings, and the tree next to my window, to see which would give the best reception.

Nerd visions of the past? Perhaps, but I think winding a tuning coil on a used toilet paper roll teaches one more than calling up the "coil" icon in Crystal RadioBuilder for Windows<sup>TM</sup>. The six-transistor radio (Figure 1) was not only a great tool for learning electronics, but it taught many "teeners" how to troubleshoot and, perhaps, even how to think. I hope today's kids have their equivalent of the six-transistor radio.

Our lead article highlights the LTC1410, a new 12-bit, 1.25MSPS analog-to-digital converter specifically designed for both AC and DC accuracy. This part consumes only 150 milliwatts from a ±5 volt supply. We also introduce three new digitalto-analog converters, the LTC1451, LTC1452, and LTC1453. These parts

Windows is a trademark of Microsoft Corporation.

bring 12-bit performance, single-supply operation, and rail-to-rail voltage output performance using a three-wire serial interface to the evergrowing LTC product line.

The LTC1472, a complete  $V_{CC}$  and VPP PCMCIA switch-matrix IC is the subjects of a feature article. This issue also introduces several new switching regulators. The LTC1266 is a synchronous, step-down switching regulator that can drive two external, N-channel MOSFETs. The LTC1266 can achieve high efficiency at loads to 10A or more. The LTC1265 is a stepdown converter in a 14-pin SOIC package, capable of operating at frequencies to 700kHz, that can supply output currents up to 1.2 Amps. The LTC1265 requires only 160 microamps of quiescent current, which decreases to only 5 microamps in shutdown conditions.

The LTC1267 is a dual switchingregulator controller with extremely wide, 4V-to-40V input operating range and reduced supply currents. This dual controller provides efficiencies better than 90% in a space-saving 28-pin SSOP package.

Additional new LTC products featured in this issue include the LT1175, a negative low-dropout regulator. We

## by Richard Markell

have articles that detail several circuits for powering the Pentium  $^{\mbox{\tiny TM}}$  microprocessor.

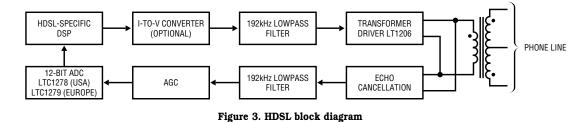

Also, we begin a series of articles on power-factor correction. We present Design Information on components for HDSL and on RS232 transceivers for DTE-DCE switching. Our Design Ideas section is, as usual, overflowing.  $\bot$

### LTC in the News

#### Linear Technology Reports Record Quarterly Sales, Increases Quarterly Dividend

Thanks to your support of Linear Technology's products, our sales reached a record \$62.1 million for the second quarter of fiscal 1995, ended January 1, 1995—an increase of 29% over the same quarter last year. Net income for the quarter was \$19.2 million, an increase of 47% over last year. A quarterly cash dividend of \$0.07 was paid on February 15, 1995 to shareholders of record on January 27, 1995.

In its November 7th, 1994 issue, *Forbes* magazine again named Linear Technology one of its "Best 200 Small Public Companies in America." This marks the fifth year in a row that the Company has been included. This year Linear Technology ranked 97th, up from 102nd last year.

In a separate story in the same issue, entitled "Small Footprints, Big Impressions," *Forbes* pointed out that LTC is one of only two companies on the list to have a capitalized value greater than a billion dollars. Among 200 companies in the listing, LTC is 40th in sales growth, seventh in net income, and fifth in market value. All in all, a very impressive showing.

LTC received the Emerging Company Award for 1995 from the Silicon Valley Chapter of Association for Corporate Growth.  $\checkmark$

## New LTC1266 Switching Regulator Provides High Efficiency at 10A Loads

#### Introduction

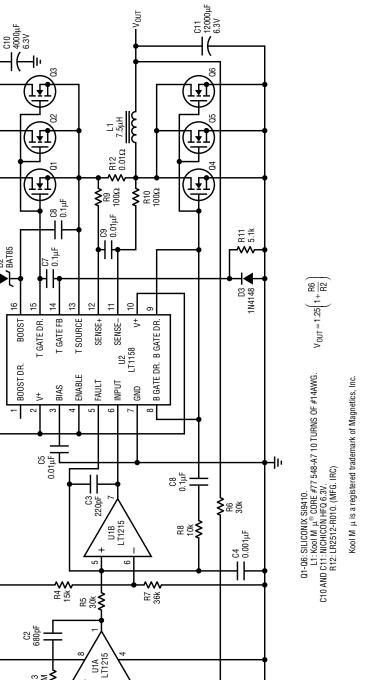

The new LTC1266 is a synchronous, stepdown switching-regulator controller that can drive two external, N-channel MOSFET switches. The superior performance of N-channel MOSFETs enables the LTC1266 to achieve high efficiency at loads of 10A or more with few additional components. Burst Mode<sup>™</sup> operation provides high efficiency at light loads—efficiency is greater than 90% for loads from 10mA to 10A. The ability to provide 10A at high efficiency is critical for supplying power to Pentium<sup>™</sup> applications.

The LTC1266 is based on the LTC1148 architecture, and has most of the features of this successful product, including constant off-time, current-mode architecture with automatic Burst Mode operation. As with the LTC1148, current-mode control provides excellent line and load transient response, inherent shortcircuit protection, and controlled startup current with minimal voltage overshoot. Pin-selectable shutdown reduces the DC supply current to 40 microamps. The LTC1266 also has a pin-selectable phase option, which allows it to drive a P-channel top-side switch, instead of an N-channel, as in the case of the LTC1148.

Other new features of the LTC1266 not available in the LTC1148 include an on-chip low-battery comparator, pin-defeatable Burst Mode, a wider voltage supply range (3.5V to 20V), 1% load regulation, and a higher maximum frequency of 400kHz.

### N-Channel versus P-Channel

The key to the LTC1266's ability to drive large loads at high efficiencies is its ability to drive both top-side and bottom-side N-channel MOSFETs. The rest of the LTC1148 family controllers require a P-channel MOSFET for the top-side switch. For load currents above about 5 amps, there are few P-channel MOSFETs available that can do the job at reasonable efficiencies.

The superiority of N-channel MOSFETs over P-channels is due to the lower  $R_{DS(ON)}$  and lower gate ca-

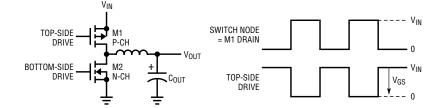

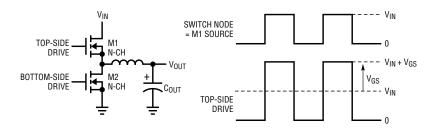

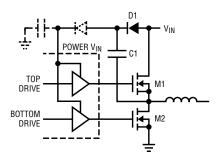

Figure 1a. Drive requirements for all N-channel MOSFET buck converter

Figure 1b. Drive requirements for complementary MOSFET buck converter

Burst Mode is a trademark of Linear Technology Corporation.

## by Greg Dittmer

pacitance achievable in the N-channel parts. The lower R<sub>DS(ON)</sub> results from the higher mobility of electrons, the majority carrier in N-channel devices, compared to holes, the majority carrier in P-channel devices. To compensate for the higher  $R_{DS(ON)}$  of the P-channel, the channel width is usually made larger, resulting in higher gate capacitance. Efficiency is inversely proportional to both  $R_{DS(ON)}$ and gate capacitance. Higher R<sub>DS(ON)</sub> decreases efficiency due to higher I<sup>2</sup>R losses and limits the maximum current the MOSFET can handle without exceeding thermal limitations; higher gate capacitance increases losses due to the increased charge required to switch the MOSFETs on and off during each switching cycle. Even with these performance advantages, the N-channel MOSFETs are generally cheaper than P-channel.

#### **Driving N-Channel MOSFETs**

If N-channels are so superior to Pchannels, why are the rest of the LTC1148 family of synchronous controllers designed to drive P-channels? The answer is that P-channels have a distinct advantage-simplicity of the gate drive. This is clear when comparing the waveforms in Figures 1a and 1b. Because of the negative threshold of the P-channel, the gate potential must decrease below the source (which is at  $V_{IN}$ ) by at least V<sub>GS(ON)</sub> to turn it on. Hence, the topside MOSFET can be gated between the available supply rail,  $V_{IN}$ , and ground.

On the other hand, driving an Nchannel top-side MOSFET isn't so straightforward. When the top-side MOSFET is turned on, the source is pulled up to  $V_{IN}$ . Because the N-channel has a positive threshold voltage, the gate must be above the source by at least  $V_{GS(ON)}$ . Thus, the top-side drive must swing between ground and  $V_{IN}$  +  $V_{GS(ON)}$ . This requires a second, higher supply rail equal to at least  $V_{IN}$  +  $V_{GS(ON)}$ .

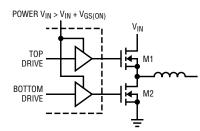

There are two ways to obtain this higher rail. The most straightforward way is if a higher rail is already available, as is the case in most desktop systems that have 12V supplies. This configuration is shown in Figure 2a. Note that the Power  $V_{\rm IN}$  input to the LTC1266 is dedicated to powering the internal drivers and is separate from the main supply input. The Power  $V_{\rm IN}$  voltage cannot exceed 18V (20V max), limiting the input voltage to

Figure 2a. Simplified schematic of all Nchannel converter with additional supply voltage (Power  $V_{IN} > V_{IN} + V_{GS(ON)}$ )

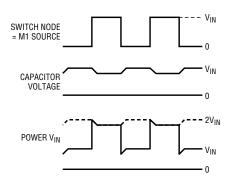

Figure 2b. Simplified schematic of all N-channel converter with charge pump

Figure 2c. Waveforms for charge pump circuit in Figure 2b

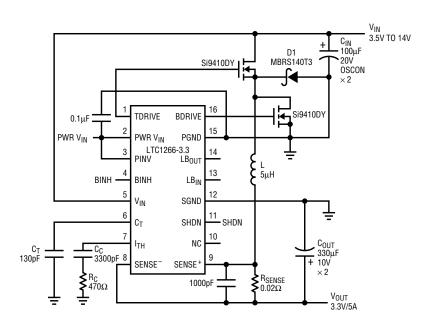

Figure 3a. All N-channel 3.3V/5A regulator with external power  $V_{\mbox{\scriptsize IN}}$

18 –  $V_{GS(ON)}.$  For a converter with logic-level MOSFETs, this limits  $V_{\rm IN}$  to about 14V. The Power  $V_{\rm IN}$  voltage must also meet its minimum requirement of  $V_{\rm IN}$  +  $V_{GS(ON)}$  (about 10V for a 5V to 3.3V converter) in order not to burn up the high-side MOSFET due to insufficient conductance at larger output loads.

If this higher rail is not available, a charge-pump circuit can be used to pump  $V_{IN}$  to the required level, as shown in Figure 2b. During the off cycle, when M2 is on, capacitor C1 is charged to V<sub>IN</sub> through D1. Power V<sub>IN</sub> and the gate of the bottom-side MOS-FET are therefore at  $V_{IN}$ . When the on-cycle commences, the internal driver places the charge-pump capacitor voltage across the gate-source of M1 and, as the source rises to  $V_{IN}$ ,  $V_{GS}$  remains constant at  $V_{IN}$ . There will be a small reduction of  $V_{GS}$  as some charge is transferred from the charge-pump capacitor to the gate capacitance of M1, although, for a charge-pump capacitor of 0.1 microfarad or larger, this reduction is almost negligible. During the on cycle, the voltage at the LTC1266 Power  $V_{IN}$  pin rises to twice  $V_{IN}$ . Since the absolute maximum at this pin is 20V, this limits  $V_{IN}$  to 9V in this circuit configuration. A higher  $V_{\rm IN}$  (about 13V) is allowable if C1 is charged from a fixed 5V source. For voltages above 13V, a P-channel top-side switch must be used, since in this configuration, the gate drive needs only to swing from  $V_{\rm IN}$  to ground. Multiple P-channel MOSFETs may need to be paralleled, however, to meet the load requirements.

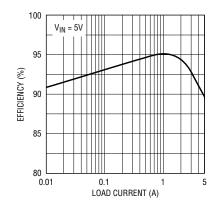

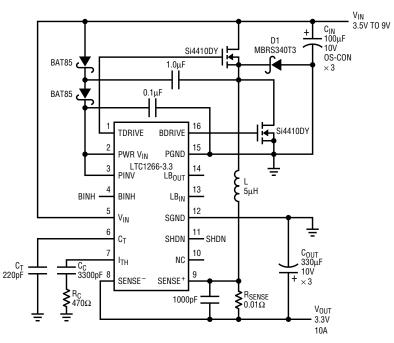

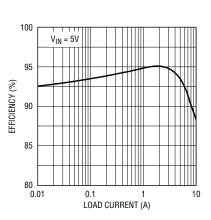

Figures 3, 4, and 5 show the three basic circuit configurations for the LTC1266. The all-N-channel, external Power V<sub>IN</sub> circuit shown in Figure 3 is a 3.3V/5A surface-mount converter. The current-sense resistor value is chosen to set the maximum current to 5A, according to the formula  $I_{OUT}$  = 100mV/R<sub>SENSE</sub>. With V<sub>IN</sub>

Figure 3b. Efficiency for Figure 3a's circuit

Figure 4a. All N-channel single-supply 5V to 3.3 V/10 amp regulator

= 5V, the 5 $\mu$ H inductor and 130pF timing capacitor provide an operating frequency of 175kHz and a ripple current of 1.25A. The V<sub>GS(ON)</sub> of the Si9410 N-channel MOSFETs is 4.5V; thus the minimum allowable voltage at the external Power V<sub>IN</sub> is V<sub>IN</sub> MAX + 4.5V. At the other end, Power V<sub>IN</sub> should be kept under the maximum safe level of 18V, limiting V<sub>IN</sub> to 18V – 4.5V = 13.5V.

Figure 4 shows an LTC1266 in the charge-pump configuration designed

to provide a 3.3V/10A output. The Si4410s are new logic-level, surfacemount, N-channel MOSFETs from Siliconix that provide a mere 20 milliohms of on-resistance at  $V_{GS}$  = 4.5V, and thus provide a 10A solution with minimal components. The efficiency plot shows that the converter still is close to 90% efficient at 10A. Because the charge-pump configuration is used, the maximum allowable  $V_{IN}$  is 18V/2 = 9V. See the LTC1266 data sheet for a charge-pump circuit

Figure 4b. Efficiency for Figure 4a's circuit

that allows input voltages above 9V. Due to the high AC currents in this circuit, we recommend low ESR OS-CON input/output capacitors to maintain efficiency and stability.

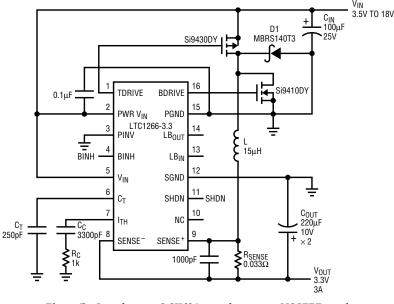

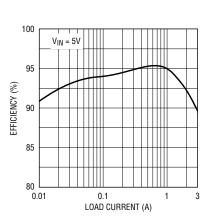

Figure 5 shows the conventional Pchannel, topside switch circuit configuration for implementing a 3.3V/3A regulator. The P-channel configuration allows the widest possible supply range of the three basic circuit configurations, 3.5V to 18V, and provides extremely low dropout, exceeding that of most linear regulators. The low dropout results from the LTC1266's ability to achieve a 100% duty cycle when in P-channel mode. In N-channel mode, the duty cycle is

Figure 5a. Low-dropout 3.3V/3A complementary MOSFET regulator

Figure 5b. Efficiency for Figure 5a's circuit

## ▲ DESIGN FEATURES

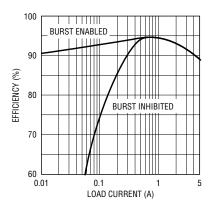

Figure 6. Efficiency comparison: Burst Mode enabled/disabled

limited to less than 100% to ensure proper startup, and thus the dropout voltage for the all N-channel converters is slightly higher.

The three application circuits demonstrate the fixed 3.3V version of the LTC1266. The LTC1266 is also available in fixed 5.0V and adjustable versions. All three versions are available in 16-pin narrow SOIC and DIP packages.

#### **Burst Mode Inhibit**

The LTC1266 also provides a function to disable Burst Mode with a CMOS logic high applied to pin 4. When observing the performance of a regulator at light loads with and without Burst Mode (see Figure 6), the performance enhancement that Burst Mode offers is immediately obvious. So why disable Burst Mode? There are certain conditions when the disadvantages of Burst Mode outweigh the advantages, and it is useful to have an easy way to disable this feature. The most common reasons for disabling Burst Mode are: 1) at light loads, the long burst cycles cause operating frequencies in the audio range, causing audible noise; 2) Burst Mode puts certain restrictions on the maximum ESR of the output capacitor, since excessive ESR (relative to the sense resistor) may falsely trigger Burst Mode. If Burst Mode is disabled, this restriction can be relaxed, at the expense of efficiency; and 3) If the circuit uses auxiliary winding(s), which depend

VOLTAGE COMP-HYSTERISIS VOUT

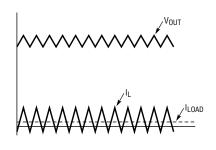

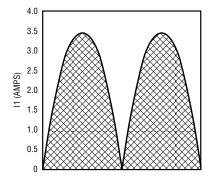

Figure 7a. Inductor current and output voltage waveforms: Burst Mode enabled

on continuous switching in the primary to transfer energy to the secondary, disabling Burst Mode guarantees this switching, independent of the primary load.

Figure 7 shows the difference between LTC1266 operation at light loads, with Burst Mode enabled and disabled. When Burst Mode is enabled (Figure 7a), the lower limit of the current-trip threshold (25mV/ R<sub>SENSE</sub>) prevents the current comparator from regulating a load below this value. The output will slowly rise until the hysteretic voltage comparator trips, at which time sleep mode commences. During sleep mode, both MOSFETs are turned off and the output capacitor supplies the load current until it discharges to the lower threshold of the voltage comparator. When this lower threshold is reached, the main loop turns on briefly again to recharge the capacitor.

When Burst Mode is disabled, the lower limit of the current trip threshold is allowed to go below zero (instead of 25mV/R<sub>SENSE</sub>). This allows the current comparator to regulate the output voltage down to zero load without having to rely on the voltage comparator for regulation. At zero load, the inductor-current waveform will be symmetrical around zero, so that the average current equals zero. During the negative current phase of the cycle, current is reversing, that is, flowing out of the output capacitor back through the inductor to ground or to the supply, in order to keep the

Figure 7b. Inductor current and output voltage waveforms: Burst Mode disabled

average current zero. The voltage comparator is not required when Burst Mode is disabled; Therefore, to ensure that it doesn't interfere with the current comparator operation, the upper threshold is raised up to take it out of the picture; however, it is still present to prevent the output voltage from overshooting.

#### Low-Battery Comparator

The LTC1266 also includes a lowbattery comparator. This comparator compares the voltage applied to pin 13 to an internal 1.25V reference and provides an open-drain output at pin 14. This 1.25V reference is dedicated to the low-battery comparator and is active even when the rest of the chip is shut down or nonfunctional due to low supply voltage. This comparator can operate down to a supply voltage of 2.5V, whereas the rest of the chip stops functioning at about 3.5V.

#### Conclusion

The new LTC1266 synchronous stepdown regulator controller is the first LTC synchronous controller with the ability to exploit the superior performance of N-channel MOSFETs to maximize efficiency and provide a low-cost, compact solution for converters. The extra features also provided in this product—Burst Mode inhibit and a low-battery comparator—make it ideal in a wide variety of applications.  $\boldsymbol{\varDelta T}$

## The LTC1267 Dual Switching-Regulator Controller Operates from High Input Voltages by Re

by Randy G. Flatness

### Introduction

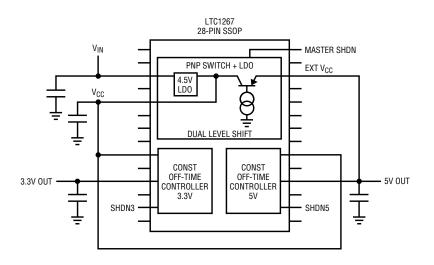

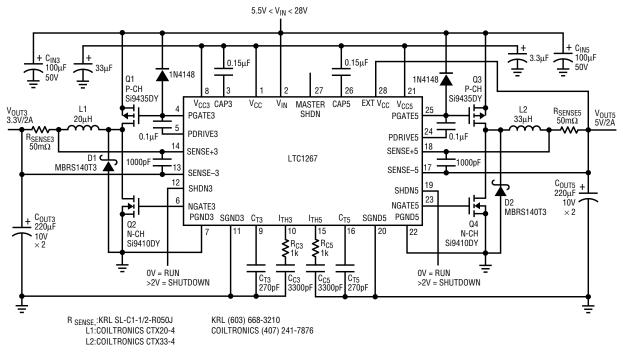

The LTC1267 dual switching regulator controller is the latest addition to Linear Technology's family of better than 90% efficient step-down DC/ DC converters. The LTC1267 features an extremely wide, 4V-to-40V input operating-voltage range and reduced supply currents. The quiescent current is a low 250 microamps, and current in shutdown mode drops to less than 20 microamps. The combination of low supply currents and high input-voltage capability is ideal for battery-powered applications that require high-voltage AC wall adapters.

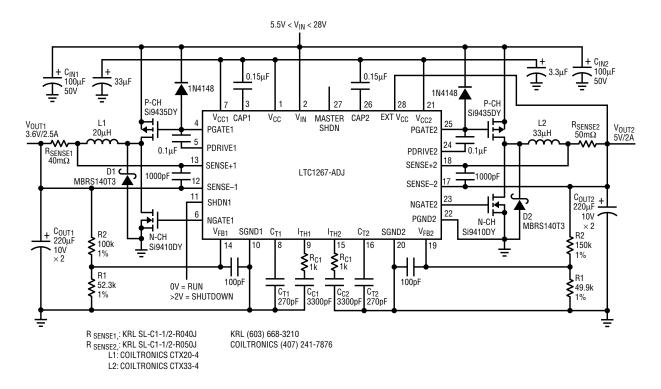

LTC offers two versions of the LTC1267, both in space-saving 28pin SSOP packages. The LTC1267 provides fixed output voltages of 3.3V and 5V with individual shutdown capability. The adjustable LTC1267-ADJ provides two user-programmable output voltages, set by external resistive dividers.

#### High Efficiency with Dual Output Voltages

To boost efficiency, a unique EXT  $V_{CC}$  pin on the LTC1267 (also present on the single output LTC1159) allows the MOSFET drivers and control circuitry to be powered from an external source, such as the output

Figure 1. Simplified block diagram, LTC1267

of the regulator itself. Obtaining control and driver power from  $V_{\rm OUT}$  improves efficiency at high input voltages, since the resulting current drawn from  $V_{\rm IN}$  is scaled by the duty cycle of the regulator. During start-up and short-circuit conditions, operating power is supplied by an internal 4.5V low-dropout regulator. This regulator automatically turns off when the EXT  $V_{\rm CC}$  pin rises above 4.5V. Figure 1 is a simplified block diagram of the control circuitry.

This 28-pin controller shares the same high performance, currentmode architecture and Burst Mode<sup>™</sup>

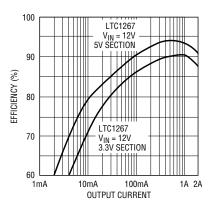

Figure 2. LTC1267 efficiency versus output current of Figure 3 circuit

| Table 1. Dual-output switching-regulator controllers |                 |                 |                 |                 |                     |                     |  |  |

|------------------------------------------------------|-----------------|-----------------|-----------------|-----------------|---------------------|---------------------|--|--|

|                                                      | LTC1142         | LTC1142HV       | LTC1142HV-ADJ   | LTC1143         | LTC1267             | LTC1267-ADJ         |  |  |

| Minimum input voltage                                | 4V              | 4V              | 4V              | 4V              | 5V                  | 5V                  |  |  |

| Maximum input voltage (Abs M                         | ax) 16V         | 20V             | 20V             | 16V             | 40V                 | 40V                 |  |  |

| Output voltage                                       | 3.3V & 5V       | 3.3V & 5V       | (2) ADJ         | 3.3V & 5V       | 3.3V & 5V           | (2) ADJ             |  |  |

| Maximum switching frequency                          | 250kHz          | 250kHz          | 250kHz          | 400kHz          | 400kHz              | 400kHz              |  |  |

| MOSFET gate-drive voltage                            | V <sub>IN</sub> | V <sub>IN</sub> | V <sub>IN</sub> | V <sub>IN</sub> | EXT V <sub>CC</sub> | EXT V <sub>CC</sub> |  |  |

| Synchronous?                                         | YES             | YES             | YES             | NO              | YES                 | YES                 |  |  |

| Package                                              | 28 SSOP         | 28 SSOP         | 28 SSOP         | 16 SOIC         | 28 SSOP             | 28 SSOP             |  |  |

Figure 3. LTC1267 dual output 3.3V and 5V high-efficiency regulator

Figure 4. LTC1267 dual, adjustable, high-efficiency regulator circuit. Output voltages set at 3.6V and 5V

operation as the LTC1142HV (see the comparison in Table 1). The LTC1267 automatically switches to Burst Mode<sup>TM</sup> operation at low output currents to maintain greater than 90% efficiency over two decades of load current range. The wide operating range is illustrated by the typical efficiency curve of Figure 2. Battery life is extended by providing high efficiencies at load currents from a few milliamps (when the device is in standby or sleep modes) to Amps (under full power conditions).

pin for only one of its two outputs.

The higher input-voltage capability of the LTC1267 is required by battery-powered systems that use many cells in series to provide more power and longer battery life for highperformance portable systems. For 12-cell and larger applications, the AC adapter voltage can be as high as 30V, well below the 40V maximum of the LTC1267, allowing operation directly from the AC adapter. (If the application uses an AC adapter voltage of 18V or less, the dual output

All members of the LTC1142/LTC1267 family are capable of 100% duty cycle, providing very low dropout operation lower than that of most linear low-dropout regulators — and all have built-in current limiting

### Description

Both regulator blocks in the LTC1267 use a constant off-time current-mode architecture. This results in a power supply that has very high efficiency over a wide load current range, fast transient response, and very low dropout. The LTC1267 is ideal for applications that require 3.3V and 5V to be implemented with the highest conversion efficiencies over a wide load current range in a small board space. The LTC1267-ADJ has two externally adjustable outputs, which allow remote load sensing and user-customized output voltages.

Each regulator section employs a pair of external, complementary MOSFETs and a user-programmable current sense resistor for setting the operating current level to optimize performance for each application. A master shutdown pin turns off both main outputs and the 4.5V LDO. Both outputs in the LTC1267 have individual shutdown capability, whereas the LTC1267-ADJ has a shutdown LTC1142HV or LTC1142HV-ADJ can be used.) At low input voltages, the internal 4.5V low-dropout regulator stays in regulation with only a 5V input voltage, extracting the maximum possible energy from the battery pack.

All members of the LTC1142/ LTC1267 family are capable of 100% duty cycle, providing very low dropout operation (lower than that of most linear low-dropout regulators), and all have built-in current limiting. As the input voltage on the LTC1267 drops, the loop extends the on-time for the P-channel switch (off-time is constant), thereby keeping the inductor ripple current constant. Eventually the on-time extends so far that the P-channel MOSFET is on at DC or 100% duty cycle. Load and line regulation are excellent for a wide variety of conditions, including making the transition from Burst Mode<sup>TM</sup> operation to continuousmode operation.

### **Typical Applications**

## Fixed Output 3.3V and 5V Converter

A fixed LTC1267 application circuit creating 3.3V/2A and 5V/2A is shown in Figure 3. The operating efficiency, shown in Figure 2, exceeds 90% for both the 3.3V and 5V sections. The 3.3V section of the circuit in Figure 3 comprises the main switch Q1, synchronous switch Q2, inductor L1, and current shunt R<sub>SENSE3</sub>.

The 5V section is similar and comprises Q3, Q4, L2, and R<sub>SENSE5</sub>. Each current-sense resistor (R<sub>SENSE</sub>) monitors the inductor current and is used to set the output current according to the formula  $I_{OUT} = 100 \text{mV/R}_{\text{SENSE}}$ . Advantages of current control include excellent line and load transient rejection, inherent short-circuit protection, and controlled startup currents. Peak inductor currents for L1 and L2 are limited to 150mV/  $R_{\text{SENSE}}$  or 3.0A. The EXT  $V_{\text{CC}}$  pin is connected to the 5V output, increasing efficiency at high input voltages. The maximum input voltage is limited by the MOSFETs and should not exceed 28V.

#### Adjustable Output 3.6V and 5V Converter

The adjustable output LTC1267-ADJ shown in Figure 4 is configured as a 3.6V/2.5A and 5V/2A converter. The resistor divider composed of R1 and R2 sets the output voltage according to the formula  $V_{OUT} = 1.25V$ (1 + R2/R1). The input voltage range for this application is 5.5V to 28V.

#### Conclusion

The LTC1267 adds even more versatility to Linear Technology's family of high-efficiency step-down regulator controllers. Providing for up to 40V input voltage, the LTC1267 allows the use of higher voltage wall adapters. The 28-pin SSOP package and associated external components make dual output voltage, high-efficiency DC-to-DC conversion feasible in the extremely small board space available in today's portable electronics. **L7**

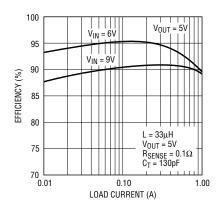

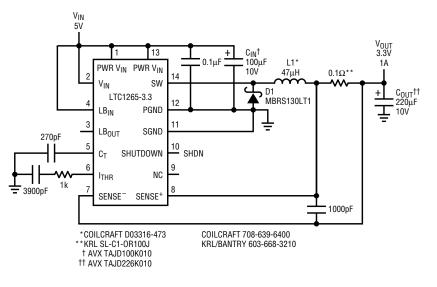

## The LTC1265: a New, High-Efficiency Monolithic Buck Converter by San-Hwa Chee

#### Introduction

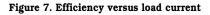

The LTC1265 is a 14-pin SOIC stepdown converter (also available in a DIP package), capable of operating at frequencies up to 700kHz. High-frequency operation permits the use of a small inductor for size-sensitive applications. The LTC1265 has an internal  $0.3\Omega$  (at a supply voltage of 10V) P-channel power MOSFET

The LTC1265 uses a constant off-time, currentmode architecture. This results in a power supply that has very high efficiency over a wide load-current range

switch, which is capable of supplying up to 1.2A of output current. With no load, the converter requires only 160 $\mu$ A of quiescent current; this decreases to a mere 5 $\mu$ A in shutdown conditions. In dropout mode, the internal P-channel power MOSFET switch is turned on continuously (at DC), thereby maximizing the life of the battery source. The part is protected from output shorts by its built-in current limiting. In addition to the features already mentioned, the LTC1265 incorporates a lowbattery detector.

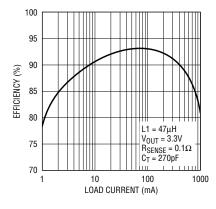

Figure 2. Efficiency versus load current

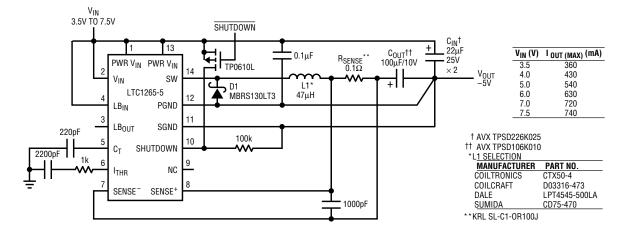

Figure 1. High-efficiency step-down converter

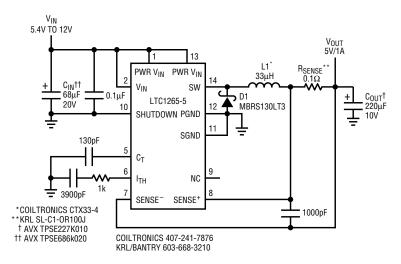

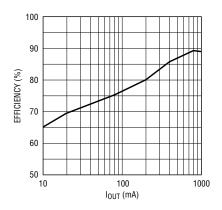

The LTC1265, like the LTC1147, is a current-mode DC-to-DC converter with Burst Mode<sup>TM</sup> operation. The current-mode architecture gives the LTC1265 excellent load and line regulation. Burst Mode results in high efficiency with both high and low load currents. The LTC1265 comes in three versions: the LTC1265-5 (5V output), the LTC1265-3.3 (3.3V output), and the LTC1265 (adjustable). All versions operate down to an input voltage of 3.5V and up to an absolute maximum of 13.5V.

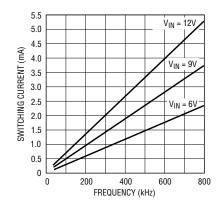

### **High-Frequency Operation**

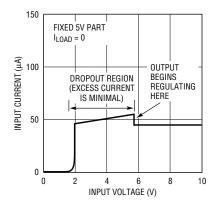

Although the LTC1265 is capable of operating at frequencies up to 700kHz, the highest efficiency is achieved at an operating frequency of about 200kHz. As the frequency increases, losses due to the gate charge of the P-channel power MOSFET increase (see Figure 3). In spacesensitive applications, high frequency operation allows the use of smaller components at the cost of four to five efficiency points.

#### Efficiency

Figure 1 shows a typical LTC1265-5 application circuit. The efficiency curves for two different input voltages are shown in Figure 2. Note that the efficiency for a 6V input exceeds 90% over a load range from less than 10mA to 850mA. This makes the LTC1265 attractive for all battery operated products and efficiencysensitive applications.

Figure 3. Gate charge losses versus frequency

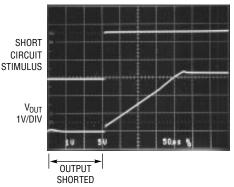

Figure 4. Short-circuit and start-up response of the LTC1265

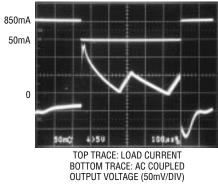

Figure 5. Load transient response

#### Constant Off-Time Architecture

The LTC1265 uses a constant offtime, current-mode architecture. This results in a power supply that has very high efficiency over a wide load-current range, fast transient response, and very low dropout characteristics. The off-time is set by an external capacitor, and is constant whenever the output is in regulation. When the output is not in regulation, the off-time is inversely proportional to the output voltage. By using a constant off-time scheme, the inductor's ripple current is predictable and well controlled under all operating conditions, making the selection of the inductor much easier. The inductor's peak-to-peak ripple current is inversely proportional to the inductance in continuous mode. If a lower ripple current is desired, a larger inductor can be used for a given value of external capacitor.

Figure 6. High-efficiency 5V to 3.3V converter

Figure 8. 2.5mm-high, 5V-to-3.3V converter (500mA output current)

Figure 9. Efficiency versus load current

## 100% Duty Cycle in Dropout Mode

When the input voltage decreases, the switching frequency decreases. With the off-time constant, the ontime is increased to maintain the same peak-to-peak ripple current in the inductor. When the input-to-output voltage differential drops below 1.5V, the off-time is reduced. This prevents the operating frequency from dropping below 20kHz as the regulator approaches dropout. As the input voltage drops further, the P-channel switch is turned on for 100% of the cycle. The dropout voltage is governed by the switch resistance, load current, and current-sense resistor.

#### Good Start-Up and Transient Behavior

The LTC1265 exhibits excellent start-up behavior when it is initially

powered-on or recovering from a short circuit. This is achieved by making the off-time inversely proportional to the output voltage when the output is still in the process of reaching its regulated value. When the output is shorted to ground, the off-time is extended long enough to prevent inductor current run-away. When the short is removed, the output capacitor begins to charge and the off-time gradually decreases. Note the absence of overshoot when the output comes out of a short-circuit, as shown in Figure 4. The initial power-up waveform is similar.

In addition, the LTC1265 has excellent load-transient response. When the load current drops suddenly, the feedback loop responds quickly by turning off the internal P-channel switch. Sudden increases in output current will be met initially by the output capacitor, causing the output voltage to drop slightly. Tight control of the inductor's current, as mentioned above, means that output-voltage overshoot is virtually eliminated (see Figure 5).

### **Typical Applications**

#### 5V-to-3.3V Converter

Figure 6 shows the LTC1265 configured for 3.3V output with 1A output-current capability. This circuit operates at a frequency of 100kHz. Figure 7 is the efficiency plot of the circuit. At a load current of 100mA, the efficiency is at 92%; the efficiency falls to 82% at a 1A output.

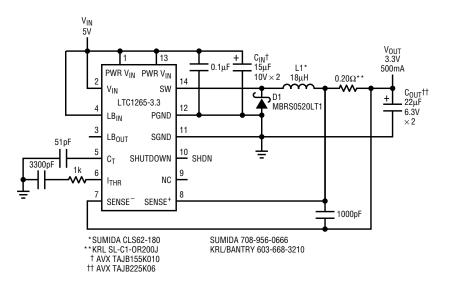

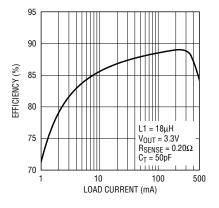

#### 2.5mm Typical-Height 5V-to-3.3V Regulator

Figure 8 shows the schematic for a very thin 5V-to-3.3V converter. For the LTC1265 to be able to source 500mA output current and yet meet the height requirement, a small-value inductor must be used. The circuit operates at a high frequency (500kHz typically), increasing the gate charge losses. Figure 9 is the efficiency curve for this application.

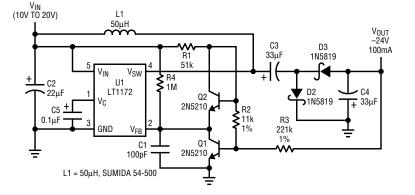

#### Positive-to-Negative Converter

Besides converting from a positive input to positive output, the LTC1265 can be configured to perform a positive-to-negative conversion. Figure 10 shows the schematic for this application.

#### Conclusion

The LTC1265, with its low dropout and high efficiency, is ideal for battery-operated products and efficiency-sensitive applications. In addition, its ability to operate at high frequencies allows the use of small inductors for size-sensitive applications.  $\boldsymbol{\Delta}$

Figure 10. Positive (+3.5 to 7.5V) to negative (-5V) converter

## The LT1175: Negative, Low-Dropout Regulator Complements LT1121/LT1129 Series by Cal

### Introduction

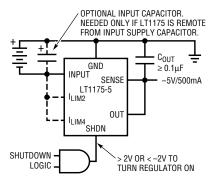

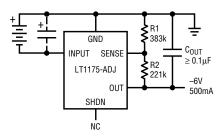

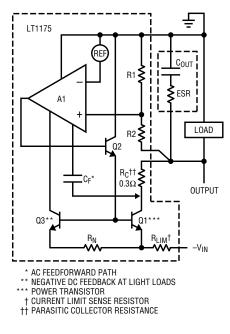

The LT1175 is a micropower, negative, low-dropout regulator that can supply up to 500mA load current. It is intended for regulating negative voltages between –3.8V and –20V, with input voltages up to –30V. Several new design techniques make the LT1175 easy to use and very tolerant of variations in the quality and size of the output capacitor. A low-dropout configuration, using an NPN pass transistor, gives the LT1175 the linear dropout characteristics of a large area FET design but with much smaller die area.

Figure 1a shows the basic configuration of the LT1175. In addition to the three terminals needed for a simple regulator, it has an output Sense pin, a Shutdown pin, and two current-limit-set pins ( $I_{LIM}$ ). The total pin count is seven, allowing two pins on the 8-pin SO or DIP packages to be connected internally to the die-attach paddle. This gives much lower thermal resistance, allowing higher power dissipation in the regulator. For even higher power dissipation, the LT1175 is available in the 5-pin, surface-mount TO-220 package. The adjustable version of the part is shown in Figure 1b. Both I<sub>LIM</sub> pins are internally connected to the input pin when the 5-pin package is used.

Figure 1a. Typical LT1175 circuit

In the adjustable version, the Sense pin allows custom selection of output voltage, with an external divider set to generate 3.8V at the Sense pin. The fixed 5V version uses the Sense pin to give true Kelvin connections to the load or to drive an external pass transistor for higher output currents. A separate Sense pin also allows for a new loop compensation technique described in more detail later.

#### Shutdown

The Shutdown pin is especially configured to be driven from either positive-voltage logic or with negative-only logic. Forcing the Shutdown pin two volts either above or below the ground pin will turn the regulator "on." This makes it simple to connect directly to positive logic signals for active-low shutdown. If no positive voltages are available, the Shutdown pin can be driven below the ground pin to turn the regulator "on." When left open, the Shutdown pin will default low to a regulator "on" condition. For all voltages below the absolute maximum ratings, the shutdown pin draws only a few microamperes of current.

In shutdown conditions, the LT1175 draws only about 10 microamps. Special circuitry is used to minimize increases in shutdown current at high temperatures, but a slight increase is seen above 125°C. One option not taken was to actively pull down on the output during shutdown. This is normally a good thing when the regulator is used by itself, but it prevents the user from shutting down the regulator when a second source of output power is connected to the LT1175 output. If active output pulldown is needed in shutdown conditions, this can be added externally with a few simple components.

## by Carl Nelson

### **Better Anti-Saturation**

The NPN bipolar pass transistor used in the LT1175 gives small die area with low saturation resistance, but without precautions, this could cause quiescent supply current to be very high under certain conditions. When the regulator input voltage is too low to maintain a regulated output, the pass transistor is driven hard by the error amplifier as it tries to maintain regulation. The current drawn by the driver transistor (Q2 in Figure 3) could be tens of milliamperes with little or no load on the output. This was the case for older IC designs that did not actively limit driver current when the power transistor saturated. The LT1175 uses a new anti-saturation technique that prevents high driver current, yet allows the power transistor to approach its theoretical saturation limit. Using parallel feedback to the base of the driver and the error amplifier controls operating points for the antisaturation circuitry much more precisely and achieves good loop stability. Very little increase in quiescent current is seen as the regulator enters the dropout condition.

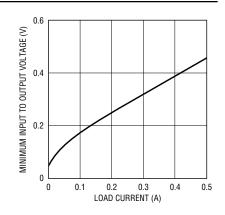

Figures 2a and 2b, respectively, show the dropout and quiescentoperating-current characteristics of the LT1175. Note that the new antisaturation circuitry keeps the dropout

Figure 1b. Higher power LT1175 circuit: Adjustable LT1175 is available in TO-220 package

Figure 2a. LT1175 dropout characteristics

characteristics close to the optimal resistive shape, with very little excess quiescent current in dropout conditions.

#### **Current Limit**

The LT1175 uses two  $\mathrm{I}_{\mathrm{LIM}}$  pins to set the current limit at 200, 400, 600, or 800mA. This allows users to select current limits tailored to specific applications. Fixed-current-limit designs often result in short circuit currents three to ten times higher than full load current, and this can create problems with input overload or excessive power dissipation in a faulted load. Current limit is 200mA with both  $I_{LIM}$  pins floating.  $I_{LIM2}$  adds 200mA of available current and  $I_{LIM4}$ adds 400mA. The LT1175 is guaranteed to be "blowout proof," regardless of the current-limit setting. Internal power limiting (also known as foldback current limiting) and thermal shutdown protect the device from destructive junction temperatures.

### An Improved Feedback Loop

Several new regulator design techniques make the LT1175 extremely tolerant of output capacitor variations. Like most low-dropout designs, which use a collector or drain of the power transistor to drive the output node, the LT1175 uses the output capacitor as part of the overall loop compensation. This generally requires the output capacitor to have a minimum value of 1–100 $\mu$ F, a maximum ESR (effective series resistance) of 0.1–1 $\Omega$ , and a minimum ESR in the range of 0.03–0.3 $\Omega$ . These restrictions usually could be met only with

good-quality solid-tantalum capacitors. Aluminum capacitors have problems with high ESR unless much higher values of capacitance (physically large capacitors) are used. Ceramic or film capacitors have too low an ESR, which makes the capacitance/ESR zero frequency too high to maintain phase margin in the regulator. Even with optimum capacitors, loop-phase margin was very low in previous designs when output current was low. These problems led to a new design technique for the LT1175 error amplifier and internal frequency compensation, as shown in Figure 3.

A conventional regulator loop consists of error amplifier A1, driver transistor Q2, and power transistor Q1. Added to this basic loop are secondary loops generated by Q3 and  $C_{\rm F}$ . A DC negative feedback current fed into the error amplifier through Q3 and  $R_N$  results in very low overall loop gain at light load currents. This is not a problem because very little gain is needed at light loads. The combination of low gain at light loads and the DC feedback moves the parasitic pole frequency at Q2's base out in frequency. The combination of these two effects dramatically improves loop phase margin at light loads, and makes the loop tolerate large ESR in the output capacitor. With heavy loads, loop phase and gain are not nearly as troublesome, and the negative feedback could degrade regulation. The logarithmic behavior of the base-emitter voltage of Q1 reduces Q3's negative feedback at heavy loads to prevent poor regulation.

In a conventional design, even with the nonlinear feedback, poor loop phase margin would occur at medium to heavy loads if the ESR of the output capacitor fell below  $0.3\Omega$ . This condition can occur with ceramic or film capacitors, which often have ESRs under  $0.1\Omega$ . The user is forced to add a resistor in series with the capacitor to guarantee loop stability. The LT1175 uses a unique AC feedforward technique to eliminate this problem. C<sub>F</sub> is a conventional feedforward capacitor, often used in regulators to cancel the pole formed

Figure 2b. LT1175 quiescent operating current

by the output capacitor. It would normally be connected from the regulated output node to feedback node at the R1-R2 junction, or to an internal node on the amplifier, as shown in Figure 3. In this case, however, it is connected to the internal structure of the power transistor. RC is the unavoidable parasitic collector resistance of the power transistor. Access to the node at the bottom of RC is available only in monolithic structures, where Kelvin connections can be made to the NPN buried-collector layer. The loop now responds as if RC were in series with the output capacitor, and good loop stability is achieved

continued on page 38

Figure 3. Block diagram of LT1175 illustrating new design techniques for internal frequency compensation and the error amplifier designs

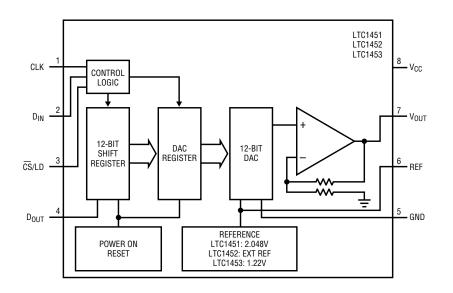

## The LTC1451, LTC1452, and LTC1453: 12-Bit, Rail-to-Rail, Micropower DACs in SO-8 Packages

by Hassan Malik and Jim Brubaker

#### Flexible, Micropower **DACs Offer True Rail-to-Rail Performance**

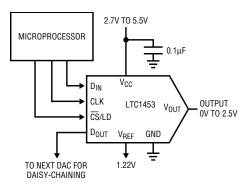

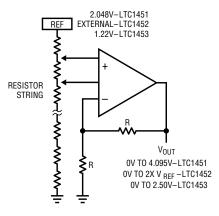

The LTC1451, LTC1452, and LTC1453 are complete 12-bit, singlesupply, rail-to-rail, voltage-output digital-to-analog converters. They include an output buffer amplifier and a Serial-Peripheral Interface (SPI) compatible, three-wire serial interface; a data-output pin makes daisy chaining possible. These DACs are guaranteed to have a DNL error of less than 0.5LSB. The typical DNL error is about 0.2LSB. A built-in power-on reset clears the output to zero scale. The output amplifier can swing to within 5 millivolts of  $V_{CC}$ when unloaded and can source or sink 5mA at a 4.5V supply. These DACs come in 8-pin PDIP and SO-8 packages.

The LTC1451 has an onboard reference of 2.048V and a nominal output swing of 4.095V. It operates from a single 4.5V to 5.5V supply dissipating 2mW ( $I_{CC}$  typical = 400 $\mu$ A).

The LTC1452 is a multiplying DAC with no onboard reference and a fullscale output of twice the reference input. It operates from a single supply that can range from 2.7V to 5.5V. It dissipates 1.125 mW (I<sub>CC</sub> typical = 225µA) at a 5V supply and a mere 0.5 mW (I<sub>CC</sub> typical = 160µA) at a 3V supply.

The LTC1453 has a 1.22V onboard reference and a convenient full scale of 2.5V. It can operate on a single supply with a wide range of 2.7V to 5.5V. It dissipates 0.75mW (I<sub>CC</sub> typical =  $250\mu$ A) with a 3V supply.

Figure 1. Block diagram, LTC1451 family

Figure 2. The 3V LTC1453 is SPI compatible and communicates with both 5V and 3V processors

### **Circuit Topology**

#### Easy-to-Use, Space-Saving Serial I/O

Figure 1 shows a block and pin diagram of the LTC1451. The three digital inputs, CLK, DIN, and  $\overline{CS}/LD$ are TTL-level compatible. Data is shifted into the input shift register, MSB first, on the rising edge of CLK. When  $\overline{\text{CS}}/\text{LD}$  is high, the DAC registers are loaded from the shift register and the CLK is disabled internally to prevent noise. Data is latched in the DAC registers on the falling edge of  $\overline{\text{CS}}$ /LD, and is shifted out MSB first through the D<sub>OUT</sub> pin. Multiple DACs can be daisy chained by connecting the  $D_{OUT}$  pin of one DAC to the DIN pin of the next. The digital inputs can swing to 5V, even when the DAC's  $V_{CC}$ is at 3V. This allows more flexibility when interfacing to the DAC. Figure 2shows how these DACs are typically used with a 3V or 5V supply.

#### Patented Architecture Guarantees Excellent DNL

Figure 3 shows a block diagram of the DAC core. The LTC1451 family uses a proprietary architecture first used in the LTC1257 and described in more detail in Volume III, Number 3 of *Linear Technology*. In this architecture, the MSBs are decoded using a resistor ladder and the LSBs are decoded using a proprietary amplifier input stage. It requires no laser trimming and is inherently monotonic, with a typical DNL error of 0.2LSB.

#### **Rail-to-Rail Output**

The output amplifier is connected in a gain-of-two configuration, which means that the output at full scale is twice the reference voltage connected to the resistor ladder. The references on both the LTC1451 and LTC1453 can be overdriven to a higher voltage to increase the full-scale output. The opamp can swing to within 5mV of  $V_{CC}$  when unloaded, giving these rail-to-rail DACs an exceptional output-swing capability. The op amp can source or sink 5mA, even at a 4.5V supply, and has an output impedance of 50 $\Omega$  when swinging to the rails. It has a wide input commonmode range that extends from ground to  $V_{CC}$  – 1.5V. The output glitch at midscale is 20nV-s and the digital feedthrough is a negligible 0.15nV-s.

#### A Wide Range of Applications

Some of the applications for this family include digital calibration, industrial process control, automatic test equipment, cellular telephones, and portable, battery-powered applications, where low supply current is essential.

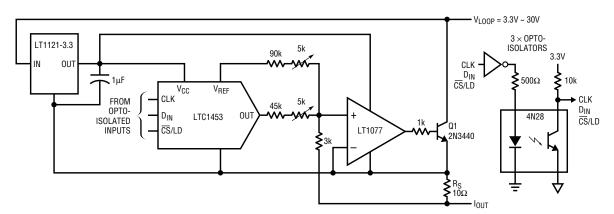

#### Loop-Powered 4–20mA Process Controller

Figure 4 shows how to use an LTC1453 to make an opto-isolated digitally controlled 4–20mA process controller. The controller circuitry, including the opto-isolation, is powered by the loop voltage, which can have a wide range of 3.3V to 30V. The 1.22V reference output of the LTC1453 is used for the 4mA offset current and  $V_{OUT}$  is used for the digitally controlled 0–16mA current. R<sub>S</sub> is a sense resistor and the op amp modulates the transistor Q1 to provide the 4–20mA current through this resistor. The potentiometers allow for

offset and full-scale adjustment. The control circuitry dissipates well under the 4mA budget at zero scale.

#### Conclusions

The LTC1451, LTC1452, and LTC1453 are the most flexible, micropower, stand-alone DACs that offer true rail-to-rail performance. This flexibility, along with the tiny SO-8 package, allows these parts to be used in a wide range of applications where size, power, DNL, and single-supply operation are important. **L7**

Figure 3. Proprietary op amp input stage ensures excellent DNL

Figure 4. Opto-isolated 4-20 milliamp process controller

## **Power Factor Correction: Part I**

#### Introduction

The term "power-factor correction" (PFC) refers to the reduction of the harmonic content, and/or the aligning of the phase angle of incoming current so that it is in phase with the line voltage required to operate an electronic device. PFC is considered very beneficial to the environment because it makes more efficient use of existing power plants. PFC is sub-

Figure 1a. Input line voltage

Figure 1b. Current drawn by a pure resistive load

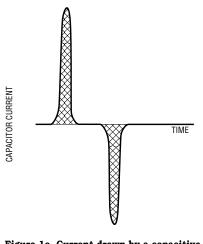

Figure 1c. Current drawn by a capacitiveinput power supply

ject to legislation and policy making throughout the industrialized world.

The European standard (IEC 555) sets maximum permissible values for the harmonics of the input line current that may be produced by equipment meeting these standards. By 1996, TV sets and other consumer equipment will be required to incorporate PFC. The benefit of PFC is realized as energy savings seen throughout the power distribution system. With PFC implemented throughout the industry, fewer new power plants will need to be built to meet projected energy demands. Consumers will pay more for "poor power factor" power at the power meter; it is hoped that, as a result, they will choose the beneficial "green" or PFCequipped devices to save energy dollars.

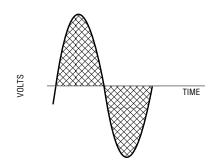

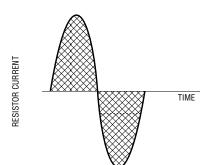

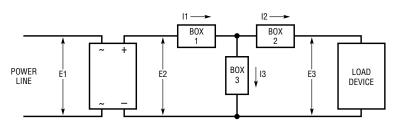

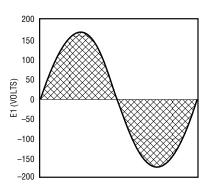

Equipment that uses DC voltages derived from the AC line generally have a poor power factor because of the capacitive input to the DC power section. The waveforms in Figure 1 show the "evils" of capacitor input power supplies. Figure 1a represents the input line voltage; Figure 1b represents a "nice" waveform of current as drawn by a resistive load; Figure 1c represents the harmonic-rich current waveform drawn by a capacitive-input power supply.

#### How PFC Performs Its Magic

The trick behind PFC is simple: make the input look as much like a resistor as possible. Resistors have the perfect power factor (unity). From the power utility company's viewpoint, unity power factor is the load of choice, a load that allows their power distribution system to operate at its maximum efficiency.

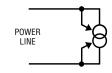

#### **Emulating a Resistor**

A resistor is emulated at the input port of a PFC by loading the incoming power line with a programmable current sink that is programmed with a voltage proportional to the instanta-

### by Dale Eagar

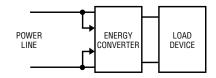

neous line voltage (Figure 2a.) The programmable current sink is the input characteristic of a "lossless energy converter" (detailed in Figure 2b). The energy converter intercepts instantaneous power from the power line, which is the product of the instantaneous voltage and the instantaneous current entering the energy converter. All energy intercepted by the energy converter is delivered to the load device.

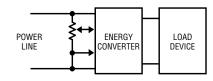

Although the devices detailed in Figures 2a and 2b emulate resistors, they provide no means of controlling the overall level of power intercepted from the power line. The circuit in Figure 2c allows for variation in both line voltage and load power. The "load device" detailed in Figures 2b and 2c is invariably a low AC impedance device; such devices include, but are not limited to, capacitors, batteries, and voltage sources.

The overall goal of PFC is to transfer power from a "wiggly" source such as an AC power line to a relatively benign DC voltage. This task must be performed without stuffing a bunch of harmonic junk back on the AC power line.

Figure 2a. Programmable current sink

Figure 2b. Non-programmable energy converter (aka PFC)

Figure 2c. Programmable energy converter (aka PFC)

Figure 3. Detailed block diagram of energy converter

#### The Energy Converter Box

#### How it Works

The energy converter shown in Figure 2b obeys the laws of conservation of energy (as we all must). As the energy intercepted at the input is transformed from one voltage to another, the current is also transformed from one value to another. The energy stays the same.

The "guts" inside the energy converter block of Figure 2b are further detailed in Figure 3. Regardless of the circuitry in boxes 1–3, we can be sure that Kirkhoff will have his way: II + I2 + I3 = 0. Further, we shall assume that whatever occupies the three boxes is lossless (a pretty good as-

sumption in a PFC with better than 95% efficiency). Since the energy intercepted from the input power line E1 cannot be dissipated in the lossless contents of Boxes 1, 2, and 3, it will be losslessly transferred to the output E3.

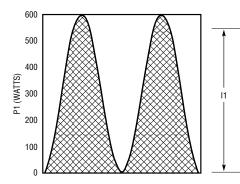

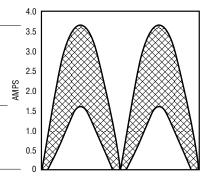

Figure 4 illustrates the waveforms of a 300W, 120V-to-382VDC power conditioner (refer also to Figure 3). Figure 4a shows E1, the input power line voltage of  $120V_{RMS}$ . Figure 4b details E2, the full-wave-rectified sine wave.

The energy converter does magic things in the three boxes to cause the waveshape of the input current I1 (Figure 4c) to be a replica of the input voltage E2, with only the magnitude **PFC:** (Power Factor Correction)— The process used to make capacitors look like resistors. PFC became popular in the early 1990's when the earthlings realized that about 10% of the power they harnessed on their planet was being converted to heat. This heat, which was dissipated through their power distribution network, become a contributing factor in their global warming trend. (see *History of the Sol System*, Vol. 17, pp. 137,657–137,698.)

being different. The power intercepted from the input is P1:

$P1 = I1 \times E2$  (see Figure 4d).

Note that the input power is a sinusoidal waveshape, is always positive, and is at twice the line voltage frequency. This is exactly what the waveshape and frequency of the power delivered from a sine wave source to a resistive load looks like.

All of the power intercepted by the energy converter circuit is transferred continued on page 21

Figure 4a. E1, input voltage waveform: 300W idealized PFC

Figure 4d. P1, power intercepted from the input (P1 =  $I1 \times E2$ ): 300W idealized PFC

200 175 150 (S1 70) 21 100 25 0 25 0

Figure 4b. E2, full-wave-rectified sinewave: 300W idealized PFC

13

12

Figure 4e. Input current, I1, and output current, I2. I3 is obtained by subtraction. 300W idealized PFC

Figure 4c. I1, input current: 300W idealized PFC

Figure 4f. Input current, 11, and current through Box 3, I3. I2 is obtained by subtraction. 300W idealized PFC

## Power for Pentium<sup>™</sup>

## by Craig Varga

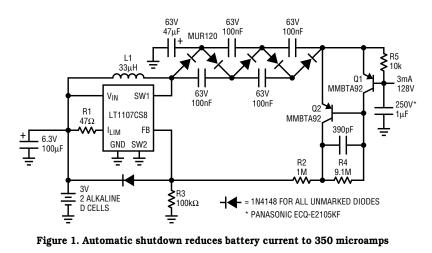

#### Introduction

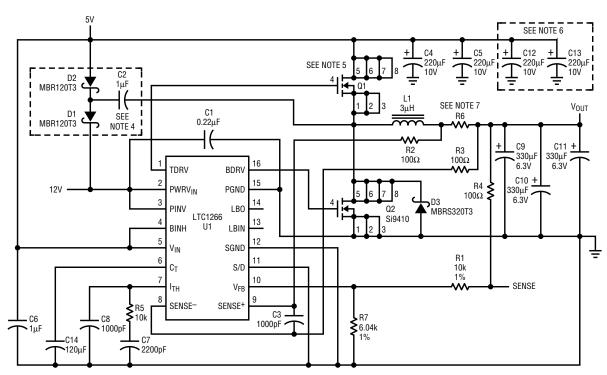

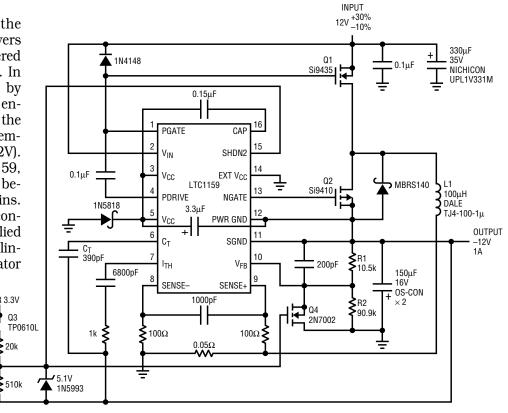

Providing power for the Pentium microprocessor family is not a trivial task by any means. In an effort to simplify this task we have developed a new control circuit and spent considerable time developing an optimized decoupling network. Here are several circuits using the new LTC1266 synchronous buckregulator control chip to provide power for the P54C, P54C-VR, and P54C-VRE microprocessors. The P54C has a supply requirement of  $3.3V\pm5\%$ , the P54C-VR requires 3.3V+5%/-0%, and the P54C-VRE requires  $3.525V \pm 75mV$ .

#### LTC1266 Drives N-Channel MOSFETs

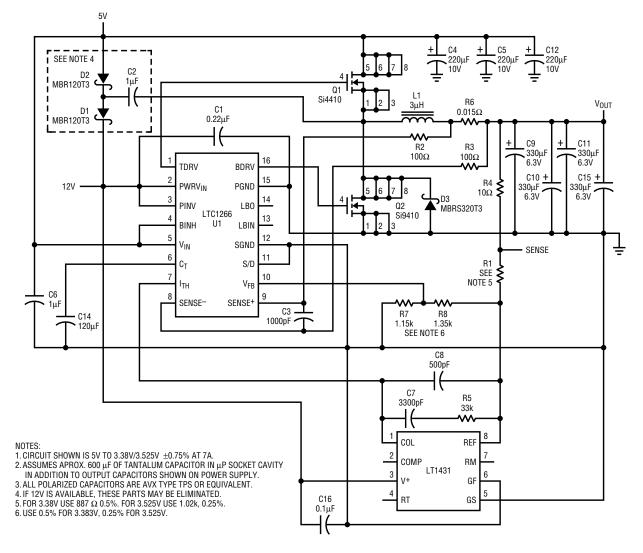

The LTC1266 controller offers several advantages over its predecessors. First, it will drive all N-channel **MOSFETs** instead of requiring P-FETs for the high side switches. This lowers cost and improves efficiency. It also has an improved, higher-gain error amplifier, which results in better load regulation, compared to that of the LTC1148 family. There is also an undedicated comparator, which may be used for a "power-good" monitor or an overvoltage detector in these applications. There is a shutdown pin and a new burst-inhibit function. Burst mode is inhibited on all the designs shown here, but for the P54C supplies, (non-VR/VRE parts) burst may be enabled if desired, resulting in improved light-load efficiency. This is done by tying pin 4 low. The reference tolerance available on the LTC1266 (or on any other PWM controller, for that matter) is not accurate enough for the -VR or -VRE specifications. The LT1431, however, has a sufficiently accurate reference for these applications, and permits very effective remote sensing (see Figure 2). Do not enable Burst Mode on the

NOTES:

1. CIRCUIT SHOWN IS 5V TO 3.3V AT 5A OR 10A,  $\pm 5\%$

ASSUMES APROX. 400 μF OF TANTALUM CAPACITOR IN μP SOCKET CAVITY IN ADDITION TO OUTPUT CAPACITORS SHOWN ON POWER SUPPLY.

3. ALL POLARIZED CAPACITORS ARE AVX TYPE TPS OR EQUIVALENT.

4. IF 12V IS AVAILABLE, THESE PARTS MAY BE ELIMINATED.

5. FOR 5A OUTPUT USE Si9410, FOR 10A, USE Si4410.

6. PARTS MAY BE ELIMINATED IN 5A DESIGN.

7. VALUE FOR 5A IS 0.02 Ω. FOR 10A USE 0.01Ω

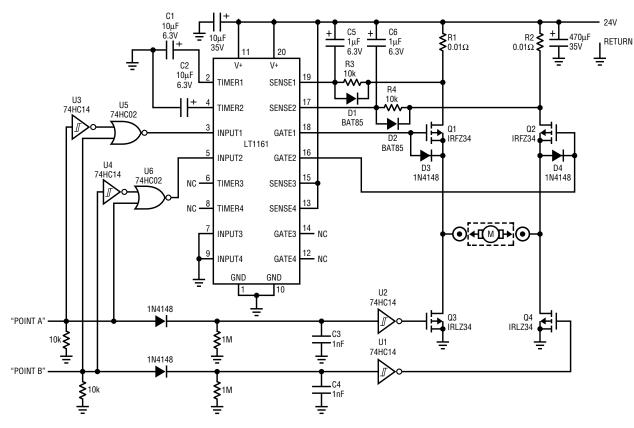

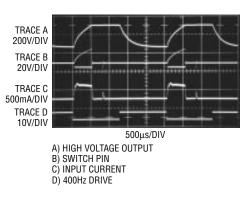

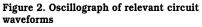

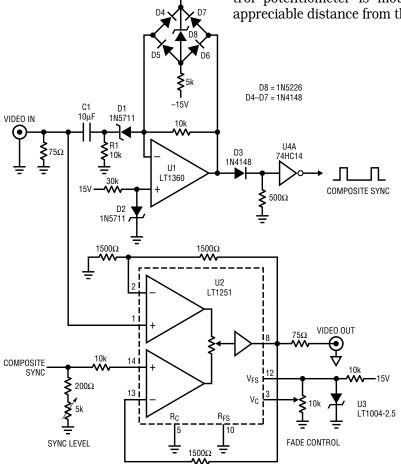

Figure 1. Pentium P54C 5/10 amp power supply circuit

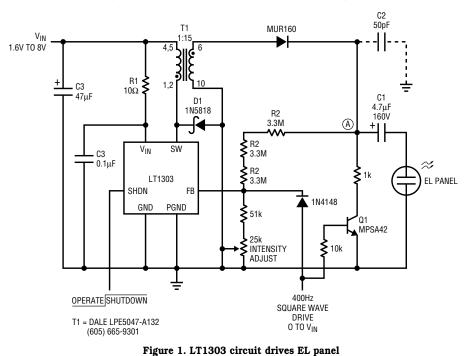

Figure 2. Pentium P54C-VR and P54C-VRE 7 amp power supply circuit

circuits designed for the P54C-VR or -VRE using the LT1431-based supplies, as the designs shown will not operate correctly at no load.

#### Handling the Load Transients

The Pentium processor has several nasty habits that require careful attention if the circuit is to be reliable. The main problem is the load transients that the processor generates. It can go from a low power (200mA) state to nearly 4 Amps in two clock cycles or 20 nanoseconds. While all this is going on, the supply voltage must be held within the spec limits. For the P54C-VR spec, the set point is 3.38V with a 2.5% tolerance. The -VRE spec is even tighter. These specs include line, load, and temperature regulation and initial set-point tolerances, as well as transient response. As may be imagined, meeting this requirement is not a trivial task. With only 2% total deviation from the ideal voltage allowed, the static specifications (line, load, temperature, and initial set-point) must be held to approximately  $\pm 1\%$  if any amount of transient response is to be permitted.

Realistically, approximately 40mV peak transient response is obtainable. To achieve this, a large number of low-ESR tantalum capacitors must be installed as close to the processor as possible. The microprocessor socket cavity is the best place. As an absolute minimum, use six 100 $\mu$ F, 10V AVX type TPS tantalums. If more height is available, as with a ZIF

socket, it is preferable to use six  $220\mu$ F, 10V parts instead. With the 100µF parts there is very little margin in the design. Do not reduce the quantity of the capacitors if going to a larger value. The ESR specs are the same for the 100µF, 220µF, and 330µF capacitors. The reason for paralleling six caps is to reduce the ESR as well as to provide bulk capacitance. In the case of standard P54C applications, a slightly larger transient can be tolerated, so somewhat less capacitance can be used. We recommend that vou use at least four 100µF AVX tantalums. In all cases there should be ten 1µF ceramic capacitors to decouple the high-frequency components of the transient.

#### Circuit-Board Layout Considerations

All the capacitors in the decoupling network should be installed on powerand ground-plane areas on the top side of the board. An absolute minimum of one feedthrough per end for each capacitor into the internal power and ground plane should be used. It is preferable to use two feedthroughs per capacitor end (64 total). Any more than that proves to be of no benefit, but at 30 total, expect about a 2mV increase in transient droop. This is about a 5% degradation in performance. Decoupling capacitors should be connected with planes rather than traces, since the traces will be far too inductive. The total network ESR must be less than 6.5 milliohms and the total ESL less than 0.07 nanohenry for the P54C-VR.

#### **Input Capacitance**

Another important consideration is the amount of capacitance on the power supply input. The ripple-current rating must be high enough to handle the regulator input ripple. In addition, this capacitance will decouple the load transients from the 5V supply. If insufficient capacitance is used, the disturbance on the 5V supply will exceed the 5% specification for the TTL logic powered by this voltage. Because the magnitude of this disturbance is quite dependent upon the nature of the 5V power supply and because the performance of these supplies varies widely, it is difficult to say just how much capacitance is needed. In general, however, if enough capacitance is present to

handle the ripple current, the disturbance on the 5V supply will be acceptable. Good transient response on the 5V supply translates to a need for less input capacitance. If sufficient bulk capacitance is present on the motherboard for the 5V supply, less additional capacitance will be required on the processor supply input. As a minimum, there should be at least one low-ESR capacitor within an inch of the regulator. Be careful to look at the level of disturbance on the 5V supply to make sure it remains within specifications.

### Powering the P54C

The same basic circuit is used for both the 5 Amp and the 10 Amp designs. The necessary substitutions are shown on the schematic (Figure 1). If 12V is available to power the LTC1266, the bootstrap capacitors and diodes can be eliminated. The 12V solution is preferred, as it is simpler and somewhat more efficient. If no 12V is available, use the bootstrap circuit. Note also that different MOSFETs are specified for the 5 Amp and 10 Amp circuits. The Si4410 is a new part from Siliconix, which offers less than half the on-resistance of the Si9410 used in the 5 Amp circuit.

#### High-Accuracy Solution— Basics of Operation

The solution for the P54C-VR and -VRE shown in Figure 2 relies on the accuracy of the LT1431. The internal reference is specified at  $2.5V \pm 0.4\%$  (worst case) at  $25^{\circ}$ C. The LT1431 consists of a precision reference and a wide-bandwidth amplifier with an

open-collector output. The feedback divider is set to place the reference input pin at 2.5V with the desired output present. The 2.5V is further divided to 1.15V to drive the LTC1266s VFB pin. In a normal application, this pin will servo to 1.25V. Hence, the LTC1266 sees the output as being too low and forces its internal error amplifier to the positive rail, which, in this case, is 2.0V. This output shows up as a current out of the  $I_{TH}$  pin. The open collector of the LT1431 draws enough current from this pin to set the output of the supply at the desired voltage. Since this constitutes a high-gain servo loop, the output is regulated very accurately. Loop compensation is accomplished by R5, C7, and C8. The internal error amplifier of the LTC1266 will act as an overvoltage protection loop should the LT1431 ever fail.

### Conclusion

The Pentium microprocessor offers some interesting challenges to the power system designer. To operate the microprocessor at higher clock speeds requires very stringent supply voltage specifications. Stop-clock power saving modes have introduced severe load transients not present in older generations of processors. However, with careful attention to detail both in component selection and mechanical layout, the required performance can be obtained. Also, the need for high efficiency can be met while providing the required dynamic performance. IT

#### PFC, continued from page 18

to the output. Therefore, the input power, P1, flows into the load device, E3, as output current I2. Further, since E3 is a constant voltage, I2 will have a waveshape that is identical to P1. Figure 4e details the input current I1 and the output current I2. By subtracting I2 from I1 we can see what I3 looks like. Figure 4f details the input current I1 and the current through box 3 (I3).

This is the first in a series of articles explaining power-factor cor-

rection. The next article will present more component level circuitry using the LT1248 and LT1249 PFC devices. In the meantime, if you require more information contact the LTC factory.

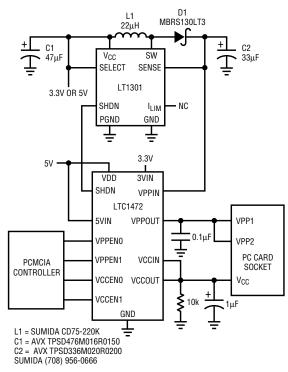

## PCMCIA Socket Voltage Switching Matrix with SafeSlot<sup>™</sup> Protection

#### Introduction

Most portable computer systems have built-in PCMCIA sockets as the sole means of expansion. The designers of these portable systems are demanding more integrated solutions for PCMCIA-socket voltage switching. In addition, many experienced designers are requiring some means of protecting their systems from meltdown when users connect damaged cards.

Host power delivery to the PC card socket flows through two paths: the main  $V_{CC}$  supply pins and the VPP programming pins. Both supplies are switchable to different voltages to accommodate a wide range of card types. The  $V_{CC}$  supply is the main supply and must be capable of providing up to 1A at either 3.3V or 5V, as well as realizing a high impedance state. The 1A rating is an absolute maximum derived from the contact rating of 500mA per pin for both  $V_{CC}$

Figure 1. Typical LTC1472 application with the LT1301 3.3V/5V boost regulator

pins. One of the most stringent actual requirements is hard-disk drive spinup current. Present hard drives require 5V at 600–800mA for a short duration during spin-up. Current draw drops to 300-420mA during read and write operations. The VPP supply must source 12V at up to 120mA, 3.3V, or 5V at lesser currents, 0V, and realize a high-impedance state. The VPP supply is intended solely for flashmemory programming. The 120mA current requirement allows erasing two flash devices and writing to two devices simultaneously, as required by many flash drives.

The host PCMCIA socket designer must also consider several other practical aspects of the design. The socket pins are exposed to the outside world and users may have little or no technical knowledge. The socket pins are vulnerable to being shorted by foreign objects, such as paper clips. In

addition, users may attempt to install damaged, possibly short-circuited, cards. In short, once the product is in the hands of the consumer, the designer and manufacturer have little control over use and abuse. To ensure a robust system and a satisfied customer, PCMCIA switch protection features such as current limiting and thermal shutdown are a necessity. These features will protect the card, socket, and main system power supply.

The nature of PC cards and portable systems requires the card to be powered on and off, as needed, to con-serve power. With many PC cards drawing over 2W, this power up/down sequencing can put demanding transient requirements on

### by Doug La Porte

the system power supply. To make the transient response of the system supply manageable, the PCMCIA switch should have break-beforemake switching with controlled rise and fall times. Controlled rise and fall times eliminate the possibility of the main supply being momentarily pulled down by a switch transient, triggering a system reset.

# LTC1472: Complete $V_{CC}$ and VPP PCMCIA Switch Matrix with SafeSlot Protection

The LTC1472 is a complete  $V_{CC}$ and VPP switch matrix that addresses all PCMCIA socket switching needs. The part is fully integrated, with no need for external switching FETs. The  $V_{CC}$  switch's  $R_{DS(ON)}$  is 140m $\Omega$  to support the current requirement of up to 1A. The  $V_{CC}$  output is switched between 3.3V, 5V and high impedance. The VPP 12V switch's  $R_{DS(ON)}$  is 0.5 $\Omega$ to support its current requirement. The VPP output pin is switched among 0V, V<sub>CC</sub>, 12V, and high impedance. Table 1 shows the V<sub>CC</sub> and VPP truth tables. The V<sub>CC</sub> logic inputs are exclusive-ORed to allow direct interfacing with both logic-high and logic-low industry standard controllers without any external glue logic. The LTC1472 is available in the spacesaving narrow 16-pin SOIC package.

The LTC1472 features SafeSlot protection. The built-in SafeSlot current-limiting and thermal-shutdown features are vital to ensuring a robust and reliable system. The  $V_{CC}$  current limit is above the 1A socket limit to maintain compatibility with all existing cards yet provide protection. For the same reason, the VPP current limit is above 120mA. All switches are break-before-make types with controlled rise and fall times for minimal system supply impact.

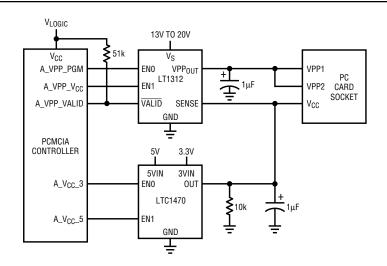

Figure 2. Typical LTC1470 application with the LT1312 VPP driver/ regulator

Figure 1 shows a typical LTC1472 application used in conjunction with the LT1301 to supply the 12V input. The LT1301 is optional. If the system already has a suitable 12V supply, it can be directly connected to the VPP  $_{\rm IN}$  pin. Be cautious when using a general purpose 12V supply; make certain that it does not have spikes or transients exceeding the flash-memory 14V maximum voltage rating and that the regulation is within the 5% flash memory tolerance.

The LTC1472 does not require a continuous 12V supply. The device has on-chip charge pumps running from the 5V supply for driving the switches. For this reason the LT1301 is usually in shutdown mode, consuming only 10 $\mu$ A. The LT1301 becomes operational only when the controller programs the LTC1472 to deliver 12V to the VPP pin. The LTC1472 also conserves power by going to a low 1 $\mu$ A standby mode when both V<sub>CC</sub> and VPP outputs are switched off. The schematic in Figure

l includes a 10k $\Omega$  pull-down resistor on the  $V_{CC\ OUT}$  pin. This resistor will ensure that, when switching the  $V_{CC}$  voltage from 5V to 3V, the voltage will not float at 5V. The current PCMCIA specification requires the voltage to be pulled down to 0.8V within 300ms. The pull-down resistor is adequate to ensure proper operation.

## LTC1470: $V_{CC}$ Switch Matrix with SafeSlot Protection

For systems where VPP switching is not required, the LTC1470 is the optimal solution. The LTC1470 is a complete  $V_{CC}$  switch matrix. It is fully integrated, with no need for external switching FETs. Performance specifications are the same as those of the  $V_{CC}$  section of the LTC1472 described above. The switch has an  $R_{DS(ON)}$  of 140m $\Omega$  to support the  $V_{CC}$  current requirements of up to 1A. Table 2 shows the truth tables for both logiclow- and logic-high-type controllers. The LTC1470 is available in the spacesaving 8-pin SOIC package. Like the LTC1472, the LTC1470 also features SafeSlot protection. The switches are break-before-make types with controlled rise and fall times for minimal system power supply impact. The built-in SafeSlot current-limiting and thermal-shutdown features are vital for a robust and reliable system.

Figure 2 shows a typical LTC1470 application with the LT1312 used to control the VPP section. The LT1312 is a linear regulator designed specifically for PCMCIA VPP voltage switching. This device requires an input voltage greater than 13V. If your application does not require VPP switching, the LT1312 can be eliminated. The LTC1470 has on-chip charge pumps for driving the switches. Only the 3.3V and the 5V inputs are required. The LTC1470 conserves power by going to a low 1µA standby mode when the output is switched off. The schematic in Figure 2 includes a  $10k\Omega$  pull-down resistor on the V<sub>CC OUT</sub> pin to guarantee that the V<sub>CC</sub> voltage will not float when turned off.

#### Conclusion

PCMCIA sockets are becoming more common as the preferred method of expansion in portable systems. As these devices proliferate to less sophisticated users, there will be greater opportunities for abuse. To counter this trend, the portable system designer must take precautions to protect the system. The high level of integration, SafeSlot protection features, and controlled rise and fall time switching make the LTC1470 and LTC1472 ideal solutions for portable systems. **L7**

|                              |             | -      |                      |             |                       |  | Table 2. LTC1470 truth table |             |      |                        |                |      |

|------------------------------|-------------|--------|----------------------|-------------|-----------------------|--|------------------------------|-------------|------|------------------------|----------------|------|

| Table 1. LTC1472 truth table |             |        | CL-PD6720 Controller |             | "365-Type" Controller |  |                              |             |      |                        |                |      |

| V <sub>cc</sub> Sv           | vitch Truth | Table  | VPP S                | witch Trutl | n Table               |  | $A_V_{CC}3$                  | $A_V_{CC}5$ |      | A_V <sub>CC</sub> _EN0 | $A_V_{CC}_EN1$ |      |

| VCCENO                       | VCCEN1      | VCCOUT | <b>VPPEN0</b>        | VPPEN1      | VPPOUT                |  | (ENO)                        | (EN1)       | OUT  | (EN0)                  | (EN1)          | OUT  |

| 0                            | 0           | OFF    | 0                    | 0           | 0V                    |  | 0                            | 0           | HiZ  | 0                      | 0              | HiZ  |

| 1                            | 0           | 5V     | 0                    | 1           | VCCIN                 |  | 1                            | 0           | 5V   | 1                      | 0              | 5V   |

| 0                            | 1           | 3.3V   | 1                    | 0           | VPPIN                 |  | 0                            | 1           | 3.3V | 0                      | 1              | 3.3V |

| 1                            | 1           | OFF    | 1                    | 1           | HiZ                   |  | 1                            | 1           | HiZ  | 1                      | 1              | HiZ  |

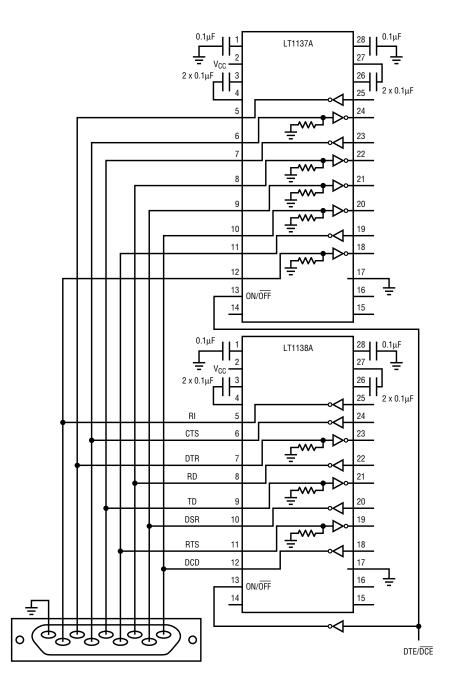

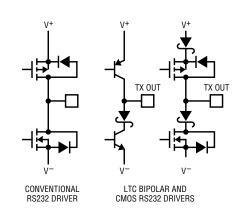

## LTC's RS232 Transceivers for DTE-DCE Switching

#### Introduction

EIA/TIA-232-E (commonly known as RS232) is the most commonly used serial data-communications standard. The standard defines signal levels and connectivity between a data terminal (DTE) and a piece of communications equipment (DCE). A cable of up to 25 lines connects the DTE and DCE. Each wire's function (data, control, or ground), pin assignment, and direction of signal flow are defined by the standard, but the software protocol used to transfer information is left unspecified.

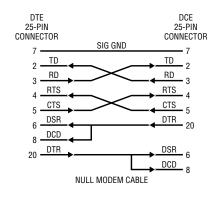

#### System Configuration

Few systems use all of the signaling lines available. The most common configuration uses nine wires, eight for signals plus one for ground. This configuration is compatible with the 9-pin serial ports on IBM PC/ATcompatible computers. Two wires are used for data transmission (one in each direction), two wires transfer control information from DTE to DCE, and four wires transfer control information from DCE to DTE. Figure 1 defines the pin assignments between a 9-pin AT connector at the DTE and a 25-pin connector at the DCE.

The EIA-232-E standard does not define whether a piece of equipment is a DTE or a DCE. In a conventional computer-to-modem link the roles

| DTE<br>9-PIN AT<br>CONNECTOR | DCD     | DCE<br>25-PIN<br>CONNECTOR |

|------------------------------|---------|----------------------------|

| ۰<br>۱                       | RD      | -                          |

| 2                            | TD      | 3                          |

| 3                            | DTR     | 2                          |

| 5                            | SIG GND | 20                         |

| 5 <u> </u>                   | DSR     | 7                          |

| 0                            | RTS     | 6                          |

| 8                            | CTS     |                            |

| Ū                            | RI      | . o                        |

| 9 —                          |         | 22                         |

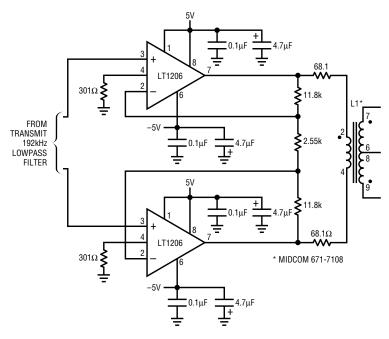

Figure 1. RS232 pin assignments: DTE 9-pin connector and DCE 25 pin connector