# INSTRUCTION MANUAL

MANUFACTURERS OF CATHODE-RAY OSCILLOSCOPES

# INSTRUCTION MANUAL

Serial Number B090834

Tektronix, Inc. • P. O. Box 500

Beaverton, Oregon

97005

Phone

644-0161

Cables: Tektronix

070-1039-00

670

# WARRANTY

All Tektronix instruments are warranted against defective materials and workmanship for one year. Tektronix transformers, manufactured in our plant, are warranted for the life of the instrument.

Any questions with respect to the warranty, mentioned above should »be taken up with your Tektronix Field Engineer or Representative.

All requests for repairs and replacement parts should be directed to the Tektronix Field Office or representative in your area. This procedure will assure you the fastest possible service. Please include the instrument Type (or Part Number) and Serial or Model Number with all requests for parts or service.

Specifications and price change privileges reserved.

Copyright <sup>(C)</sup> 1970 by Tektronix, Inc., Beaverton, Oregon. Printed in the United States of America. All rights reserved. Contents of this publication may not be reproduced in any form without permission of the copyright owner.

U.S.A. and foreign Tektronix products covered by U.S. and foreign patents and/or patents pending.

# TABLE OF CONTENTS

| SECTION 1 | 7503 SPECIFICATION                | Page  | SECTION 3   | CIRCUIT DESCRIPTION                     | Page |

|-----------|-----------------------------------|-------|-------------|-----------------------------------------|------|

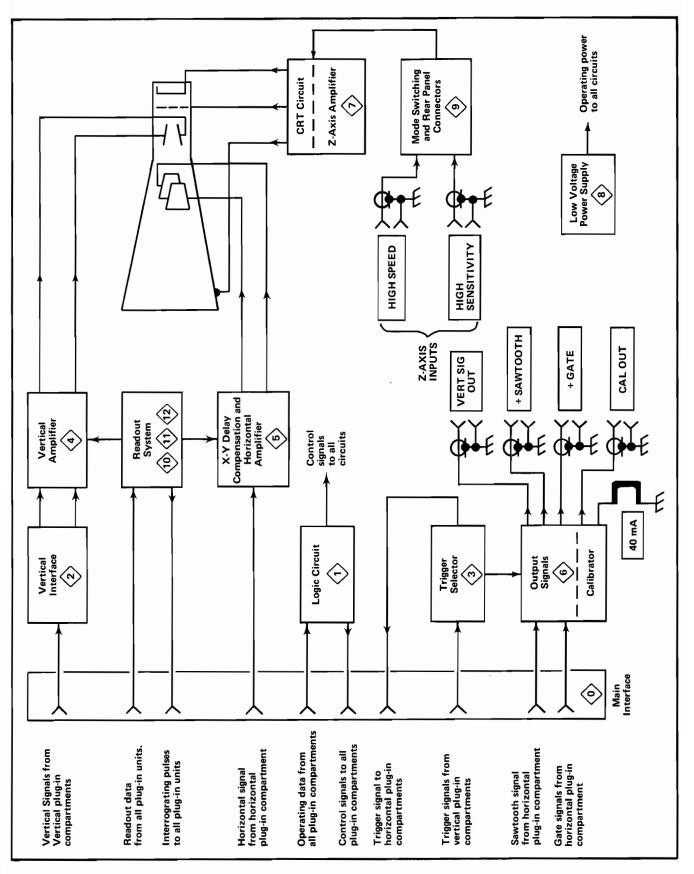

|           | Table 1-1 Electrical              | 1-1   |             | Block Diagram                           | 3-1  |

|           | Vertical Deflection System        | 1-1   |             | Circuit Operation                       | 3-3  |

|           | Triggering                        | 1-2   |             | Logic Fundamentals                      | 3-3  |

|           | Horizontal Deflection System      | 1-2   |             | Main Interface                          | 3-3  |

|           | Calibrator                        | 1-2   |             |                                         | 3-7  |

|           | External X-Axis Inputs            | 1-2   |             | Logic Circuit                           |      |

|           |                                   |       |             | Trigger Selector                        | 3-22 |

|           | Signal Outputs                    | 1-3   |             | Vertical Interface                      | 3-25 |

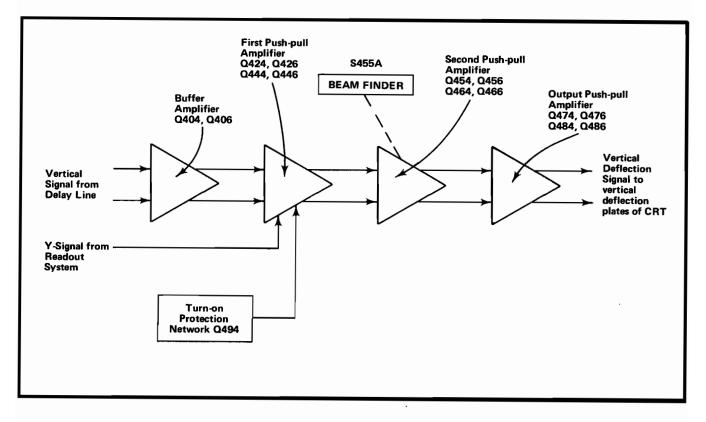

|           | Power Supply                      | 1-3   |             | Vertical Amplifier                      | 3-27 |

|           | Cathode-Ray Tube (CRT)            | 1-3   |             | X-Y Delay Compensation and Horizontal   |      |

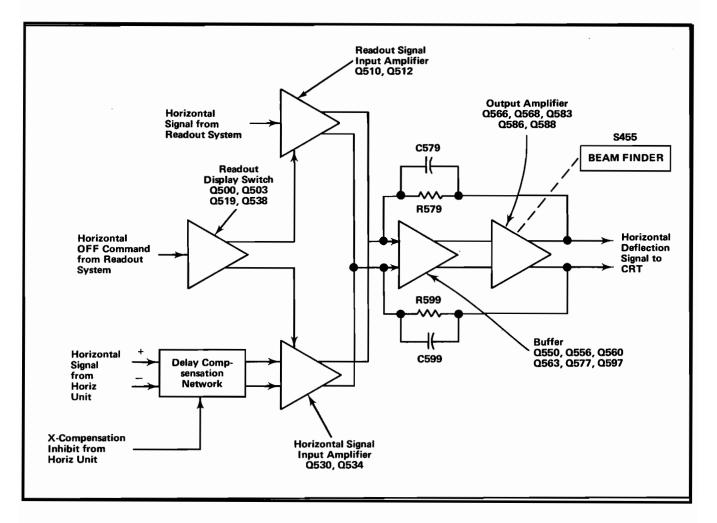

|           | Table 1-2 Environmental           | 1-4   |             | Amplifier                               | 3-28 |

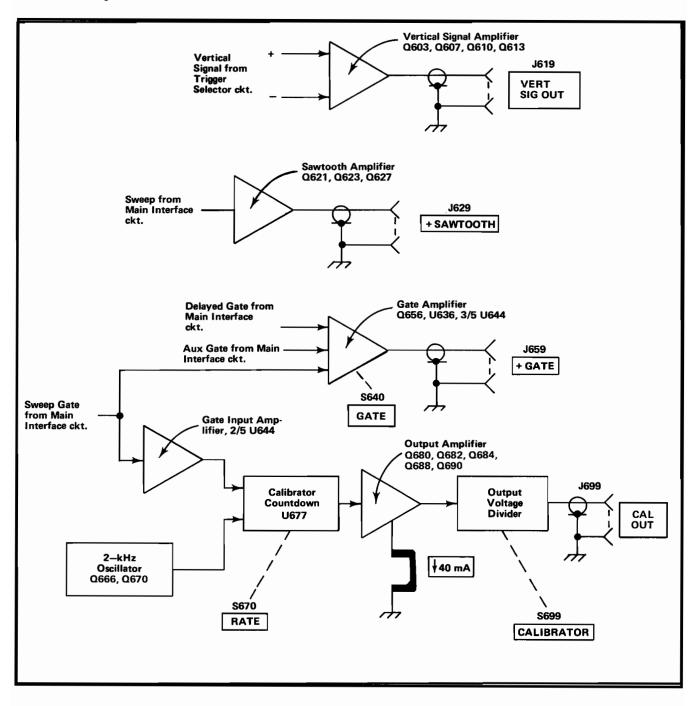

|           | Table 1-3 Physical                | 1-4   |             | Output Signals and Calibrator           | 3-31 |

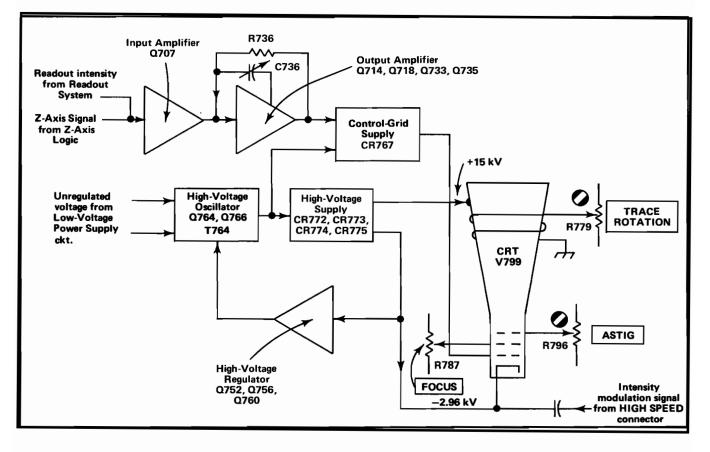

|           | Standard Accessories              | 1-5   |             | CRT Circuit                             | 3-34 |

|           | Instrument Options                | 1-5   |             | Low-Voltage Power Supply                | 3-36 |

|           | System Specifications             | . •   |             | Mode Switching and Rear-Panel           |      |

|           |                                   |       |             | Connectors                              | 3-42 |

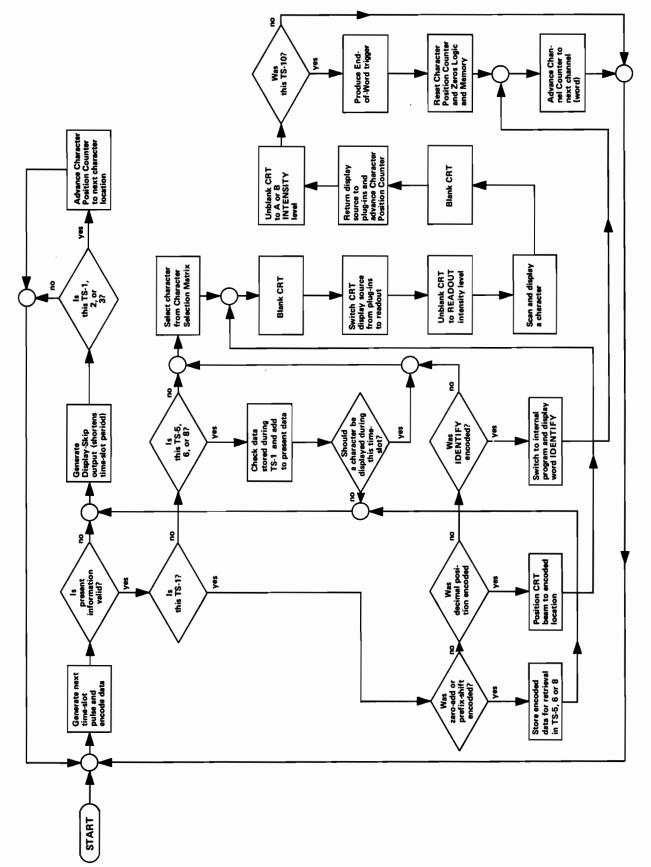

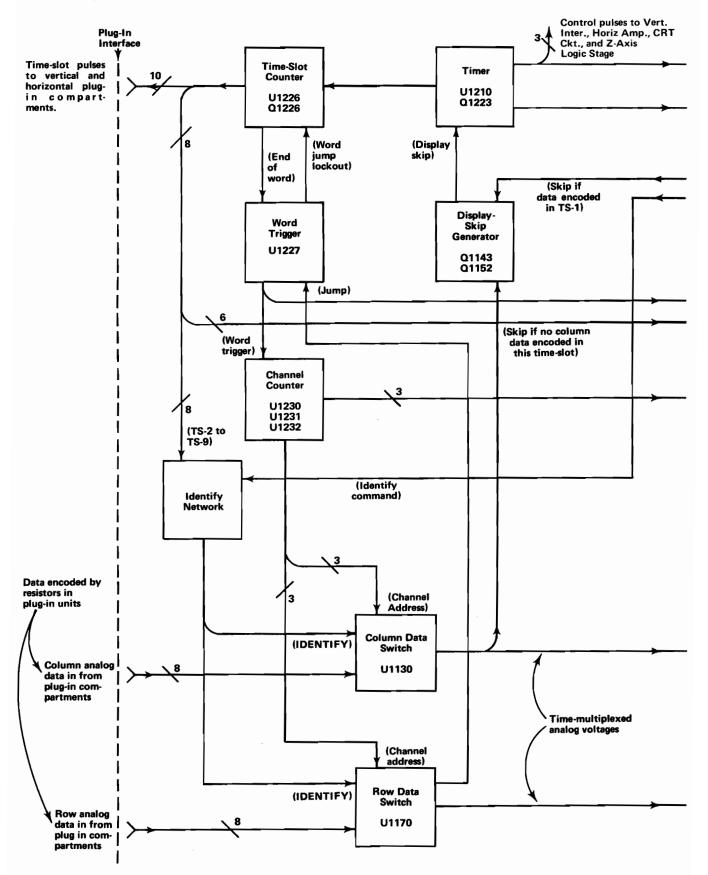

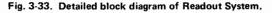

| SECTION 2 | OPERATING INSTRUCTIONS            |       |             | Readout System                          | 3-43 |

| SECTION 2 |                                   |       | SECTION 4   | MAINTENANCE                             |      |

|           | Preliminary Information           | 2-1   |             | Panel Removal                           | 4-1  |

|           | Operating Voltage                 | 2-1   |             | Power Unit Removal                      | 4-1  |

|           | Operating Temperature             | 2-2   |             | Preventive Maintenance                  | ••   |

|           | Operating Position                | 2-2   |             | Cleaning                                | 4-1  |

|           | Plug-In Units                     | 2-2   |             | Lubrication                             | 4-2  |

|           | -                                 |       |             | Visual Inspection                       | 4-2  |

|           | Controls and Connectors           | 2-3   |             | Semiconductor Checks                    | 4-3  |

|           | Cathode-Ray Tube (CRT)            | 2-3   |             | Recalibration                           | 4-3  |

|           | Mode Selectors                    | 2-5   |             | Troubleshooting                         | 4-3  |

|           | Calibrator                        | 2-5   |             | Troubleshooting Aids                    | 4-3  |

|           | Inputs                            | 2-5   |             | Troubleshooting Equipment               | 4-5  |

|           | Side Panel                        | 2-5   |             | Troubleshooting Techniques              | 4-5  |

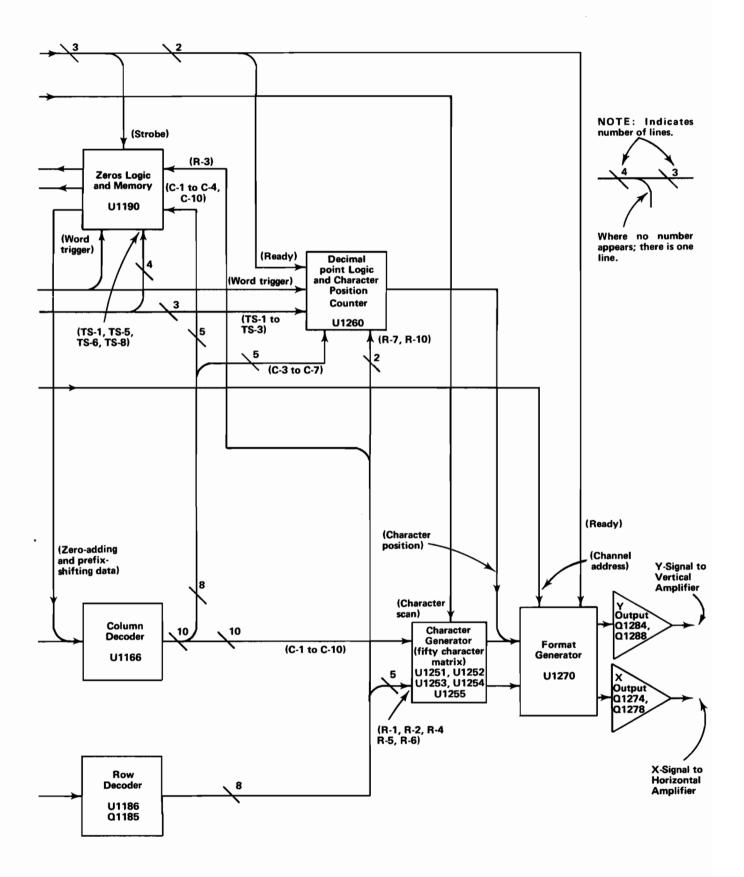

|           | Rear Panel                        | 2-6   |             | Troubleshooting the Readout System      | 4-11 |

|           | First Time Onesation              |       |             | Corrective Maintenance                  | 4-13 |

|           | First-Time Operation              | 2-6   |             | Obtaining Replacement Parts             | 4-13 |

|           | Set-Up Information                | 2-6   |             | Soldering Techniques                    | 4-13 |

|           | Calibration                       | 2-7   |             |                                         | 4-13 |

|           | Vertical Mode                     | 2-7   |             | Component Replacement                   |      |

|           | Triggering                        | 2-7   |             | Recalibration After Repair              | 4-20 |

|           | Control Illumination              | 2-7   | SECTION 5   | PERFORMANCE CHECK/CALIBRATION           |      |

|           | Readout                           | 2-7   | SECTION 5   | FERFORMANCE CHECK/CALIBRATION           |      |

|           | Beam Finder                       | 2-8   |             | Test Equipment Required                 | 5-1  |

|           | Calibrator                        | , 2-8 |             | Adjustment Tools                        | 5-2  |

|           | Z-Axis Input                      | 2-8   |             | Short-Form Procedure and Index          | 5-3  |

|           | Test Set-Up Chart                 | 2-9   |             | Performance Check/Calibration Procedure | 5-6  |

|           | General Operating Information     |       |             |                                         |      |

|           | Simplified Operating Instructions | 2-9   | SECTION 6   | ELECTRICAL PARTS LIST                   |      |

|           | Intensity Controls                | 2-11  |             | Abbreviations and Symbols               |      |

|           | Astigmatism Adjustment            | 2-12  |             | Parts Ordering Information              |      |

|           | Trace Alignment Adjustment        | 2-12  |             | Index of Electrical Parts List          |      |

|           | Graticule                         | 2-12  |             | Electrical Parts List                   |      |

|           | Light Filter                      | 2-13  |             |                                         |      |

|           | Beam Finder                       | 2-13  | SECTION 7   | DIAGRAMS AND MECHANICAL PARTS           |      |

|           | Control Illumination              | 2-13  |             | ILLUSTRATIONS                           |      |

|           | Readout                           | 2-13  |             | Di                                      |      |

|           | Vertical Mode                     | 2-14  |             | Diagrams                                |      |

|           | Trigger Source                    | 2-15  |             | Mechanical Parts Illustrations          |      |

|           | X-Y Operation                     | 2-15  |             | Accessories                             |      |

|           | Intensity Modulation              | 2-15  |             | Repackaging                             |      |

|           | Raster Displays                   | 2-16  | OF OTION O  |                                         |      |

|           | Calibrator                        | 2-16  | SECTION 8   | MECHANICAL PARTS LIST                   |      |

|           | Signal Outputs                    | 2-17  |             | Mechanical Parts List Information       |      |

|           | Probe Power Connectors            | 2-17  |             | Index of Mechanical Parts Illustrations |      |

|           | Remote Connector                  | 2-17  |             | Mechanical Parts List                   |      |

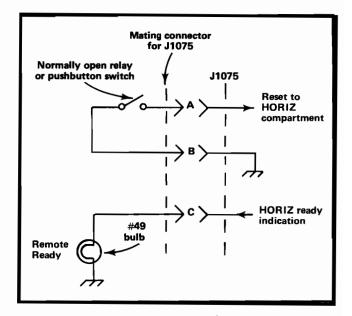

|           | Remote Single-Sweep Reset         | 2-18  |             |                                         |      |

|           | Applications                      | 2-18  | CHANGE INFO | ORMATION                                |      |

|           |                                   |       |             |                                         |      |

Abbreviations and symbols used in this manual are based on or taken directly from IEEE Standard 260 "Standard Symbols for Units", MIL-STD-12B and other standards of the electronics industry. Change information, if any, is located at the rear of this manual.

۵

i

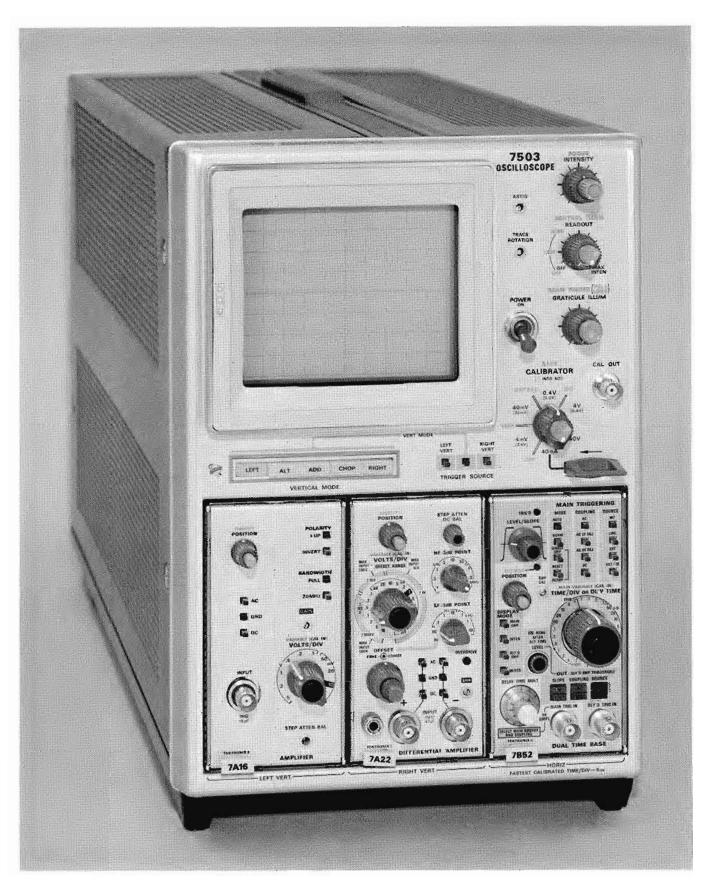

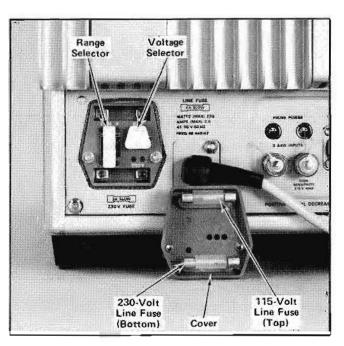

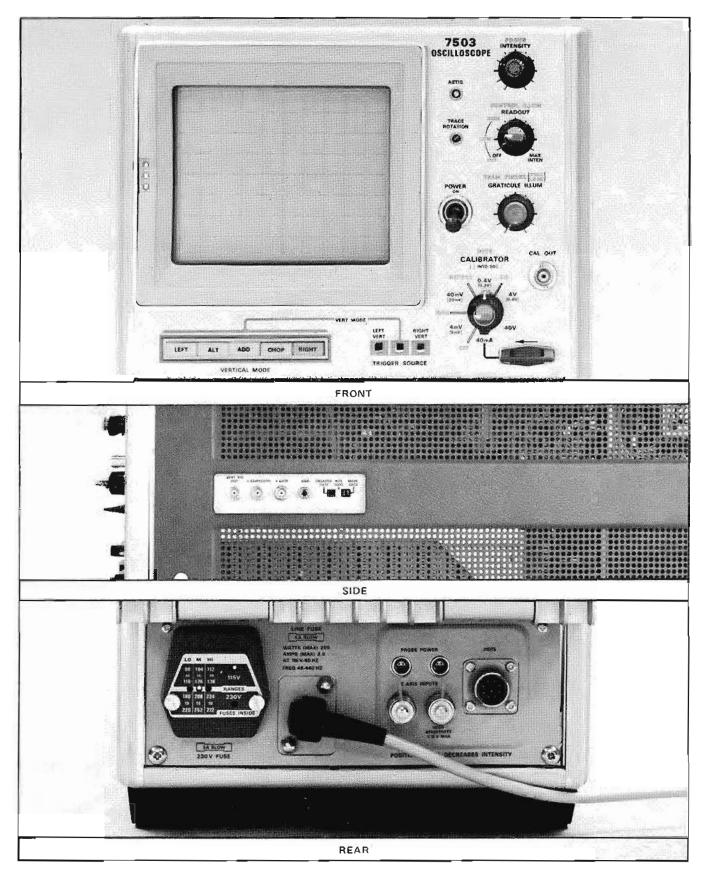

Fig. 1-1, 7503 Oscilloscope.

# **SECTION 1** 7503 SPECIFICATION

Change information, if any, affecting this section will be found at the rear of the manual.

#### Introduction

The Tektronix 7503 Oscilloscope is a solid-state, high performance instrument designed for general-purpose applications. This instrument accepts Tektronix 7-series plug-in units to form a complete measurement system. The flexibility of this plug-in feature and the variety of plug-in units available allow the system to be used for many measurement applications.

The 7503 has three plug-in compartments. The left and center plug-ins are connected to the vertical deflection system. The right plug-in is connected to the horizontal deflection system. Electronic switching between the plugins connected to the vertical deflection system allows a dual-trace vertical display. This instrument features regulated DC power supplies to assure that performance is not affected by variations in line voltage and frequency, or by changes in load due to the varying power requirements of the plug-in units. Maximum power consumption of this instrument is about 260 watts (60 Hertz, 115-volt line).

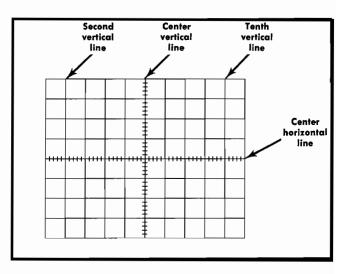

The 7503 features a CRT with an 8 X 10 centimeter graticule area with small spot size and high writing rate. Additionally, the instrument includes a readout system providing CRT display of alpha-numeric information from the plug-ins, including deflection factor, sweep rate and other encoded parameters.

This instrument will meet the electrical characteristics listed in Table 1-1 following complete calibration as given in Section 5. The performance check procedure given in Section 5 provides a convenient method of checking instrument performance without making internal checks or adjustments. The following electrical characteristics apply over a calibration interval of 1000 hours and an ambient temperature range of 0°C to +50°C, except as otherwise indicated. Warmup time for given accuracy is 20 minutes.

#### NOTE

Many of the measurement capabilities of this instrument are determined by the choice of plug-in units. The following characteristics apply to the 7503 only. See the system specification later in this section for characteristics of the complete system.

| Characteristic                   | Performance                                                                                                                                                    | Characteristic                                                     | Performance                                                                          |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| VERTIC                           | AL DEFLECTION SYSTEM                                                                                                                                           |                                                                    |                                                                                      |

| Deflection Factor                | Compatible with all 7-series plug-in units.                                                                                                                    | Time segment<br>from each<br>compartment                           | 0.4 to 0.6 microsecond.                                                              |

| Deflection Accuracy              | Less than 1% difference between                                                                                                                                | -                                                                  |                                                                                      |

|                                  | compartments.                                                                                                                                                  | Delay Line                                                         | Permits viewing of leading edge of<br>triggering signal.                             |

| Low-Frequency<br>Linearity       | 0.1 division or less compression or<br>expansion of a center-screen two-<br>division signal when positioned to<br>the top and bottom of the graticule<br>area. | Vertical Display<br>Modes (selec-<br>ted by front-<br>panel VERTI- | LEFT: Left vertical only.<br>ALT: Dual-trace, alternate be-<br>tween vertical units. |

| solation Between<br>Compartments | At least 100:1 from DC to 75 megahertz.                                                                                                                        | CAL MODE<br>switch)                                                | ADD: Added algebraically.<br>CHOP: Dual-trace, chopped be-                           |

| Chopped Mode<br>Repetition Rate  | One megahertz ±20%.                                                                                                                                            |                                                                    | tween vertical units.<br>RIGHT: Right vertical only.                                 |

# TABLE 1-1

#### Specification-7503

| Characteristic                        | Performance                                  |  |  |

|---------------------------------------|----------------------------------------------|--|--|

|                                       | TRIGGERING                                   |  |  |

| Trigger Source<br>(selected by front- | VERT MODE: Determined by ver-<br>tical mode. |  |  |

| panel TRIGGER<br>SOURCE switch)       | LEFT VERT: From left vertical unit only.     |  |  |

|                                       | RIGHT VERT: From right vertical unit only.   |  |  |

| Characteristic                                                  | Performance                                                         |              |  |

|-----------------------------------------------------------------|---------------------------------------------------------------------|--------------|--|

| Repetition Rates<br>(selected by<br>front-panel<br>RATE switch) | One kilohertz.<br>One-half repetition rate of sweep<br>gate.<br>DC. |              |  |

| One-Kilohertz<br>Accuracy                                       | +15°C to +35°C                                                      | 0°C to +50°C |  |

|                                                                 | Within 0.25%                                                        | Within 0.5%  |  |

| Duty Cycle                                                      | 50% ± 0.5%.                                                         |              |  |

| Risetime and Falltime<br>4 mV through 4 V<br>and 40 mA          | Less than 0.25 mic                                                  | rosecond.    |  |

| 40 V                                                            | Less than two microseconds with 10 pF load.                         |              |  |

#### HORIZONTAL DEFLECTION SYSTEM

| Deflection Factor                                                         | Compatible with all 7-series plug-in units.          |  |

|---------------------------------------------------------------------------|------------------------------------------------------|--|

| Fastest Calibrated<br>Sweep Rate                                          | Five nanoseconds/division.                           |  |

| Phase Shift Between<br>Vertical and Hori-<br>zontal Deflection<br>Systems |                                                      |  |

| With phase correction                                                     | Adjustable to less than 2° from DC to two megahertz. |  |

## **EXTERNAL Z-AXIS INPUTS**

| High Sensitivity<br>Input                                         |                                                                                                           |  |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|

| Sensitivity                                                       | Two volts peak-to-peak provides trace modulation over full intensity range.                               |  |

| Useful input volt-<br>age vs. repetition<br>frequency             | Two volts peak-to-peak, DC to tw<br>megahertz; reducing to 0.4 volt<br>peak-to-peak at 10 megahertz.      |  |

| Polarity of operation                                             | Positive-going signal decreases trace<br>intensity; negative-going signal in-<br>creases trace intensity. |  |

| Minimum pulse<br>width that pro-<br>vides intensity<br>modulation | 40 nanoseconds at two volts.                                                                              |  |

| Input resistance                                                  | 500 ohms ± 10%.                                                                                           |  |

| Maximum input<br>voltage                                          | 15 volts (DC + peak AC).                                                                                  |  |

| High Speed Input                                                  |                                                                                                           |  |

| Sensitivity                                                       | 60 volts peak-to-peak provides trace<br>modulation over full intensity range<br>from DC to 75 megahertz.  |  |

| Polarity of operation                                             | Positive-going signal decreases trace<br>intensity; negative-going signal in-<br>creases trace intensity. |  |

#### CALIBRATOR

| Wave Shape                                                               | Square wave.                                      |  |

|--------------------------------------------------------------------------|---------------------------------------------------|--|

| Polarity                                                                 | Positive going with baseline at zero volts.       |  |

| Output Voltage (se-<br>lected by front-<br>panel CALIBRA-<br>TOR switch) |                                                   |  |

| Open circuit                                                             | Four millivolts to 40 volts in five decade steps. |  |

| Into 50 ohms                                                             | Two millivolts to 0.4 volts in four steps.        |  |

| Output Current                                                           | 40 milliamperes through current loop.             |  |

| Amplitude Accuracy<br>(Voltage and<br>Current)                           |                                                   |  |

| +15°C to +35°C                                                           | Within 1%.                                        |  |

| 0°C to +50°C                                                             | Within 2%.                                        |  |

ļ

| Characteristic                                                    | Performance                                           |  |

|-------------------------------------------------------------------|-------------------------------------------------------|--|

| Minimum pulse<br>width that pro-<br>vides intensity<br>modulation | Five nanoseconds at 60 volts.                         |  |

| Input resistance<br>at DC                                         | 18 kilohms ± 15%.                                     |  |

| Maximum input<br>voltage                                          | 60 volts (DC + peak AC). 60 volts<br>peak-to-peak AC. |  |

#### SIGNAL OUTPUTS

| + Sawtooth                          |                                                                                                                                           |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Polarity                            | Positive-going with baseline at zero volts $\pm$ one volt (into one megohm).                                                              |

| Output voltage                      |                                                                                                                                           |

| Rate of rise                        |                                                                                                                                           |

| Into 50 ohms                        | 50 millivolts/unit of time $\pm 15\%$ . <sup>1</sup>                                                                                      |

| Into one<br>megohm                  | One volt/unit of time ±10%. <sup>1</sup>                                                                                                  |

| Peak voltage                        |                                                                                                                                           |

| Into 50 ohms                        | Greater than 500 millivolts.                                                                                                              |

| Into one<br>megohm                  | Greater than 10 volts.                                                                                                                    |

| Output resistance                   | 950 ohms ±2%.                                                                                                                             |

| + Gate                              |                                                                                                                                           |

| Source (selected<br>by Gate switch) | MAIN GATE from displayed time-<br>base; DELAYED GATE from de-<br>laying time-base unit; or AUX<br>GATE from dual-sweep time-base<br>unit. |

| Output voltage                      |                                                                                                                                           |

| Into 50 ohms                        | 0.5 volt ±10%.                                                                                                                            |

| Into one<br>megohm                  | 10 volts ±10%.                                                                                                                            |

| Risetime into 50<br>ohms            | 20 nanoseconds or less.                                                                                                                   |

| Output resistance                   | 950 ohms ±2%                                                                                                                              |

$^{1}$ Unit of time selected by time-base time/division switch.

| Characteristic         | Performance                                           |  |

|------------------------|-------------------------------------------------------|--|

| Vertical Signal Output |                                                       |  |

|                        |                                                       |  |

| Source                 | Determined by TRIGGER<br>SOURCE switch.               |  |

| Output voltage         |                                                       |  |

| Into 50 ohms           | 25 millivolts/division of vertical deflection ±25%.   |  |

| Into one<br>megohm     | 0.5 volt/division of vertical deflection $\pm 25\%$ . |  |

| Output resistance      | 950 ohms ±2%.                                         |  |

| POWER SUPPLY                    |                                                                                        |  |

|---------------------------------|----------------------------------------------------------------------------------------|--|

| Line Voltage Range<br>(AC, RMS) | Line voltage and range selected by<br>Line Voltage Selector assembly on<br>rear panel. |  |

| 115-volts nominal               | 90 to 110 volts.                                                                       |  |

|                                 | 104 to 126 volts.                                                                      |  |

|                                 | 112 to 136 volts.                                                                      |  |

| 230-volts nominal               | 180 to 220 volts.                                                                      |  |

|                                 | 208 to 252 volts.                                                                      |  |

|                                 | 224 to 272 volts.                                                                      |  |

| Line Frequency                  | 48 to 440 hertz.                                                                       |  |

| Maximum Power<br>Consumption    | 258 watts, 3.0 amperes at 60 hertz, 115-volt line.                                     |  |

## CATHODE-RAY TUBE (CRT)

| Graticule   |                                                                                            |

|-------------|--------------------------------------------------------------------------------------------|

| Туре        | Internal with variable edge lighting.                                                      |

| Area        | Eight divisions vertical by ten divisions horizontal. Each division equals one centimeter. |

| Resolution  |                                                                                            |

| Horizontal  | At least 15 lines/division.                                                                |

| Vertical    | At least 15 lines/division.                                                                |

| Geometry    | 0.1 division or less total bowing of<br>a displayed horizontal or vertical<br>line.        |

| Beam Finder | Limits display within graticule area.                                                      |

#### Specification-7503

| Characteristic                                                                    | Performance                                                                                                                |  |  |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Photographic Writing<br>Speed (without film<br>fogging techniques)                |                                                                                                                            |  |  |

| Tektronix C-51<br>Camera with<br>∱1.2 lens and<br>1:0.5 object-<br>to-image ratio | At least 2250 centimeters/<br>microsecond with Polaroid <sup>2</sup> Type<br>410 film (10,000 ASA) and P31<br>CRT phospor. |  |  |

| Tektronix C-27<br>Camera with<br>f1.5 lens and<br>1:0.5 object-<br>to-image ratio | At least 1500 centimeters/<br>microsecond with Polaroid Type<br>410 film (10,000 ASA) and P31<br>CRT phosphor.             |  |  |

#### TABLE 1-2

#### ENVIRONMENTAL

Performance

Characteristic

#### NOTE

This instrument will meet the electrical characteristics given in Table 1-1 over the following environmental limits. Complete details on environmental test procedures, including failure criteria, etc., can be obtained from Tektronix, Inc. Contact your local Tektronix Field Office or representative.

| Temperature Range |                         |  |

|-------------------|-------------------------|--|

| Operating         | 0°C to +50°C.           |  |

| Non-operating     | 55°C to +75°C.          |  |

| Altitude          |                         |  |

| Operating         | 15,000 feet.            |  |

| Non-operating     | Test limit 50,000 feet. |  |

<sup>2</sup>Registered trademark of the Polaroid Corporation.

| Characteristic                                                                                                          | Performance                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Electro-magnetic<br>Interference (EMI)<br>as tested in MIL-I<br>6181 D (when<br>equipped with EMI<br>modification only) |                                                                                                                                            |

| Radiated interfer-<br>ence                                                                                              | Interference radiated from the instrument under test within the given limits from 150 kilohertz to 1000 megahertz.                         |

| Conducted<br>interference                                                                                               | Interference conducted out of the instrument under test through the power cord within the given limits from 150 kilohertz to 25 megahertz. |

| Transportation (pack-<br>aged instruments,<br>without plug-ins)                                                         | Qualifies under National Safe<br>Transit Committee test procedure<br>1A.                                                                   |

## TABLE 1-3

#### PHYSICAL

| Characteristic                                          | Performance                                                                                                                                             |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ventilation                                             | Safe operating temperature is main-<br>tained by convection cooling. Auto-<br>matic resetting thermal cutout pro-<br>tects instrument from overheating. |

| Warmup Time                                             | 20 minutes for rated accuracy.                                                                                                                          |

| Finish                                                  | Anodized front panel. Blue-vinyl painted aluminum cabinet.                                                                                              |

| Overall Dimensions<br>(measured at max-<br>imum points) |                                                                                                                                                         |

| Height                                                  | 13.5 inches (34.2 centimeters).                                                                                                                         |

| Width                                                   | 9.2 inches (23.4 centimeters).                                                                                                                          |

| Length                                                  | 24.6 inches (62.2 centimeters).                                                                                                                         |

| Net Weight (instru-<br>ment only)                       | 47 pounds (21.3 kilograms).                                                                                                                             |

#### STANDARD ACCESSORIES

Standard accessories supplied with the 7503 are listed on the last pull-out page of the Mechanical Parts List illustrations. For optional accessories available for use with this instrument, see the Tektronix, Inc. catalog.

#### **INSTRUMENT OPTIONS**

#### General

The following options are available for the 7503 and can be installed as part of the instrument when ordered, or they can be installed at a later time. Complete information on all options for this instrument is given in this manual. For further information on instrument options, see your Tektronix, Inc. catalog, or contact your local Tektronix Field Office or representative.

#### **Option 1**

This option deletes the Readout System. Operation of the instrument is unchanged except that there is no alphanumeric display on the CRT and the READOUT control is non-functional. The Readout System can be added at any time by ordering the readout conversion kit.

#### Option 2

With option 2 installed, the instrument will meet the EMI interference specifications given in Table 1-2.

# SYSTEM SPECIFICATIONS

Your 7000-Series oscilloscope system will provide exceptional flexibility in operation with a wide variety of general and special purpose plug-in amplifiers and time bases. The Type number of a particular plug-in identifies it thus: the first digit (7) denotes the oscilloscope system (7000); the second character describes the use of the plug-in—A for amplifier, B for "real time" time base, J or K for spectrum analyzer, L for single-unit spectrum analyzer (a double-width plug-in). M for miscellaneous, S for sampling unit, and T for sampling time base. The third and fourth digits in the plug-in title are sequence numbers. The table following lists specifications that are dependent upon the system as a whole.

|             |          | 7500-   | Series | 7700-   | Series      | Deflectio | Vertical<br>n Factor A | l System<br>ccuracy* | SIG     | ουτ    | Horizontal System                                                                                                                                                                                                                       |

|-------------|----------|---------|--------|---------|-------------|-----------|------------------------|----------------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Plug-In     | Probe    | BW      | Tr     | BW      | Tr          |           | INT CAL                |                      | BW      | Tr     |                                                                                                                                                                                                                                         |

| Unit        |          |         |        |         |             | 0-50°C    | 15°-35°C               | 0-50°C               |         |        |                                                                                                                                                                                                                                         |

| <u>7A11</u> | Integral | 90 MHz  | 3.9 ns | 150 MHz | 2.4 ns      | 2%        | 3%                     | 4%                   | 60 MHz  |        | Horizontal System                                                                                                                                                                                                                       |

| 7A12        | None     | 75 MHz  | 4.7 ns | 105 MHz | 3.4 ns      | 2%        | 3%                     |                      | 55 MHz  |        | bandwidth with 2                                                                                                                                                                                                                        |

|             | P6053    | 75 MHz  | 4.7 ns | 105 MHz | '3.4 ns     | 3%        | 4%                     | 5%                   | 55 MHz  | 6.4 ns | units of the same type<br>operated X-Y with<br>phase correction is 2<br>MHz for the 7500-                                                                                                                                               |

| 7A13        | None     | 75 MHz  | 4.7 ns | 100 MHz | 3.5 ns      | 1 1/2%    | 2 1/2%                 | 3 1/2%               | 55 MHz  | 6.4 ns | Series, 3 MHz for the                                                                                                                                                                                                                   |

|             | P6053    | 75 MHz  | 4.7 ns | 100 MHz | 3.5 ns      | 1 1/2%    | 2 1/2%                 | 3 1/2%               | 55 MHz  | 6.4 ns | 7700-Series unless<br>otherwise stated.<br>Without phase correc-                                                                                                                                                                        |

| 7A14        | P6021    | 45 MHz  | 7.8 ns | 50 MHz  | 7.0 ns      | 2%        | 3%                     | 4%                   | 40 MHz  | 8.8 ns | tion the 7700-Series horizontal bandwidth                                                                                                                                                                                               |

|             | P6022    | 75 MHz  | 4.7 ns | 105 MHz | 3.4 ns      | 2%        | 3%                     | 4%                   | 50 MHz  | 7.0 ns | horizontal bandwidth<br>upper 10% down<br>point is 3 MHz; that<br>of the 7500-Series is 5                                                                                                                                               |

| 7A16        | None     | 90 MHz  | 3.9 ns | 150 MHz | 2.4 ns      | 2%        | 3%                     | 4%                   | 60 MHz  | 5.9 ns | MHz, unless otherwise                                                                                                                                                                                                                   |

|             | P6053    | 90 MHz  | 3.9 ns | 150 MHz | 2.4 ns<br>, | 3%        | 4%                     | 5%                   | 60 MHz  | 5.9 ns | indicated. X-Y phase<br>shift with correction<br>is 2° at 2 MHz for<br>both Series unless<br>otherwise stated.                                                                                                                          |

| 7A22        | None or  | 1.0 MHz | 350 ns | 1 MHz   | 350 ns      | 2%        | 3%                     | 4%                   | 1.0 MHz | 350 ns | Both the 7700- and                                                                                                                                                                                                                      |

|             | Any      | ±10%    | ±9%    | ±10%    | ±9%         |           |                        |                      | ±10%    | ±9%    | 7500-Series are speci-<br>fied as follows: Band-<br>width with phase cor-<br>rection is 800 kHz;<br>without phase correc-<br>tion bandwidth is 1<br>MHz $\pm 10\%$ ; X-Y phase<br>shift with phase cor-<br>rection is 1° at 100<br>kHz. |

#### 7000-SERIES OSCILLOSCOPE SYSTEM SPECIFICATION

\*Deflection Factor accuracy is checked as follows:

EXT CAL 0°C to 50°C, plug-in gain is set at a temperature within 10°C of operating temperature, using an external calibrator whose accuracy is within .25%.

INT CAL 15°C to 35°C, plug-in gain is set while operating within a temperature range of +15°C to +35°C, using the oscilloscope calibrator.

INT CAL 0°C to 50°C, plug-in gain is set using the oscilloscope calibrator (within 10°C of the operating temperature) in a temperature range between 0°C and +50°C.

# PLUG-IN OPTIONS MAJOR CHARACTERISTICS AMPLIFIERS

#### 7A11 FET Probe Wide Band Amplifier (All specifications at Probe tip)

| Deflection Factor | 5 mV/div to 20 V/div                        |

|-------------------|---------------------------------------------|

| Input Resistance  | 1 MΩ within 1%                              |

| Input Capacitance | 2 to 6 pF depending on Volts/div<br>setting |

| DC Offset         | Up to 400 V referred to input               |

Attenuation via integral FET Probe and/or amplifier from X1 through X400 controlled automatically by Volts/div switch to prevent display from overscaning screen.

Fig. 1, 7A11 FET Probe Wide Band Amplifier (All specifications at Probe tip).

#### 7A12 Dual Trace Wide Band Amplifier

| Deflection Factor | 5 mV/div to 5 V/div, pushbutton selected                                                                                     |

|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| Input Resistance  | 1 M $\Omega$ within 2%                                                                                                       |

| Input Capacitance | 24 pF within 1 pF for all deflection factors                                                                                 |

| DC Offset         | Equivalent to at least 1000 div                                                                                              |

| Operating Modes   | CH 1 Only, CH 2 Only, Chopped,<br>Alternate and Added. Either chan-<br>nel can be inverted for differential<br>measurements. |

Fig. 2. 7A12 Dual Trace Wide Band Amplifier.

# **AMPLIFIERS** (Cont)

#### 7A13 Differential Comparator & Differential Amplifier

| Deflection Factor                   | 1 mV/div to 5 V/div              |

|-------------------------------------|----------------------------------|

| Calibrated Compari-<br>son Voltages | 0 to +10 Volts or 0 to -10 Volts |

| Input Resistance                    | 1 M $\Omega$ within 0.15%        |

| Input Capacitance                   | 20 pF within 0.4 pF              |

Fig. 4. 7A14 Current Probe Amplifier,

# 7A13

Fig. 3. 7A13 Differential Comparator and Differential Amplifier.

#### 7A14 Current Probe Amplifier

| Deflection Factor | 1 mA/div to 1 A/div                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Input Connector   | Special BNC connector senses type<br>of probe in use and switches inter-<br>nal compensation circuit so no gain<br>adjustment is needed. |

Fig. 5. 7A16 Wide Band Amplifier.

#### 7A16 Wide Band Amplifier

| Deflection Factor | 5 mV/div to 5 V/div                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Input Resistance  | 1 M $\Omega$ within 2%                                                                                                          |

| Input Capacitance | 15 pF within 0.5 pF                                                                                                             |

| Bandwidth         | (See System Specification) Main-<br>tains full bandwidth capabilities of<br>system over complete range of<br>deflection factors |

# **AMPLIFIERS** (Cont)

| Deflection Factor | 10 µV/div to 10 V/điv                                                     |

|-------------------|---------------------------------------------------------------------------|

| Input Resistance  | 1 M $\Omega$ within 1%                                                    |

| Input Capacitance | 47 pF within 2.5 pF                                                       |

| Displayed Noise   | 16 $\mu V$ at 10 $\mu V/div$ at maximum bandwidth, tangentially measured. |

7A22 High-Gain Differential Amplifier

Fig. 6. 7A22 High-Gain Differential Amplifier.

# **REAL TIME TIME BASES**

#### 7B50 Time Base

- Sweep Rate 5 s/div to 50 ns/div (5 ns/div with X10 MAGNIFIER) in 25 calibrated steps Triggering To 100 MHz or vertical amplifier bandwidth, whichever is less. Sweep free runs providing bright baseline

- in the absence of adequate triggering signal in P-P AUTO and AUTO triggering modes

- Internal Trigger 1 ns or less at 75 MHz Jitter

- Display Mode Time-Base for normal sweep operation. Amplifier for X-Y operation

Fig. 8. 7851 Delaying Time Base.

Flg. 7. 7850 Time Base.

#### 7B51 Delaying Time Base

Used singly in 7500-Series oscilloscope as conventional time base, or in combination with Type 7B50 as delaying sweep time base.

| Sweep Rate and<br>Triggering          | Same as Type 7B50                                                 |

|---------------------------------------|-------------------------------------------------------------------|

| Delay Time Multî-<br>plier Range      | 0 to 10 times the time/div setting                                |

| Accuracy                              | 5 s/div to 1 s/div within 2% 0.5 s/<br>div to 1 μs/div within 1%. |

| Multiplier Incre-<br>mental Linearity | Within 0.2%                                                       |

| Jitter                                | 1 part or less in 50,000 of 10X the<br>TIME/DIV setting           |

# **REALTIME TIME BASES (Cont)**

#### 7B52 Dual Time Base Unit

Designed specifically for the 7500-Series Oscilloscopes but is compatible with all the 7000-Series.

- Sweep Rate 0.05 µs/div to 5 s/div (5 ns/div with 10X MAGnifier) in 25 calibrated steps.

- Triggering To 100 MHz or vertical amplifier bandwidth, whichever is less. Man sweep free runs in Auto Mode, providing bright trace in the absence of a triggering signal. Delayed sweep is triggerable after delay.

- Display Mode Main Sweep, Manix Sweep intensified during Delayed Sweep, Delayed Sweep only, and Mixed (display of Main Sweep and Delayed Sweep). Horizontal Amplifier can be used for X-Y operation.

Fig. 9. 7852 Dual Time Base.

7B70 Time Base

Fig. 10, 7870 Time Base.

| Sweep Rate   | 0.02 µs/div to 5 s/div (2 ns/div<br>with X10 MAGNIFIER) in 26 cali-<br>brated steps                                                                                                                            |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Triggering   | To 200 MHz or vertical amplifier<br>bandwidth, whichever is less. Sweep<br>free runs providing bright base line<br>in the absence of adequate trigger-<br>ing signal in P-P AUTO and AUTO<br>triggering modes. |

| Dísplay Mode | Time-Base for normal sweep opera-<br>tion. Amplifier for X-Y operation<br>and phase measurements.                                                                                                              |

# **REALTIME TIME BASES (Cont)**

Fig. 11. 7871 Delaying Time Base.

#### 7B71 Delaying Time Base

Used singly in 7700-Series oscilloscope as conventional time base, or in combination with Type 7B70 as delaying sweep time base.

| Sweep Rate and<br>Triggering          | Same as Type 7B70                                    |

|---------------------------------------|------------------------------------------------------|

| Delay Time Multiplier<br>Range        | 0 to 10 times TIME/DIV setting                       |

| Accuracy                              | 5 s/div to 1 s/div within 2%                         |

|                                       | 0.5 s/div to 1 $\mu s/div$ within 1%                 |

| Multiplier Incre-<br>mental Linearity | within 0.2%                                          |

| Jitter                                | 1 part or less in 50,000 of 10X<br>TIME/DIV setting. |

## SAMPLING UNIT

#### 7S11 Sampling Unit

Single channel sampling unit accepting all Tektronix sampling heads. Vertical characteristics set by the sampling head in use.

| DC Öffset         | ±1 volt                    |

|-------------------|----------------------------|

| Units/Div         | 2 to 200                   |

| Polarity          | Display normal or inverted |

| Output connectors | Offset & Vertical Signal   |

|                   |                            |

Internal Trigger circuits operate with sampling heads containing trigger pickoff circuitry. Will operate with a second 7S11 for dual-trace sampling, both controlled by a 7T11 Sampling Sweep Unit.

Fig. 12, 7S11 Sampling Unit.

# SAMPLING SWEEP

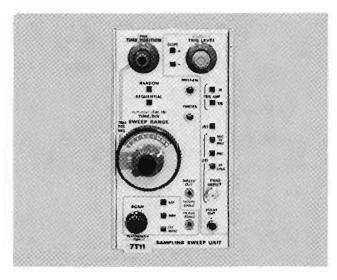

#### 7T11 Sampling Sweep Unit

Automatically provides equivalent time or real time sampling process. Random mode or sequential mode available during equivalent time sampling. Operates with one or two 7S11 Sampling Units.

| Sweep Rates                     | Equivalent time, 5 $\mu$ s/Div to 10 ps/Div Real time, 5 ms/Div to 0.1 $\mu$ s/Div |

|---------------------------------|------------------------------------------------------------------------------------|

| Time Position Ranges            | Equivalent time, 50 ns to 50 $\mu$ s<br>Real time, 0.5 ms to 50 ms                 |

| Triggering                      | Internal (except with S-3 plug-in head) or External.                               |

| Modes                           | Frequency Range                                                                    |

| Internal                        | DC to 500 MHz                                                                      |

| External, 50 Ω<br>Input         | DC to 500 MHz                                                                      |

| External, 1 ΜΩ<br>Input         | DC to 100 MHz                                                                      |

| External, 50 Ω<br>Input HF sync | 500 MHz to 12.4 GHz                                                                |

| Frequency coverage              | DC coupled through 12.4 GHz HF<br>Sync                                             |

| Sensitivity                     | 5 mV to 2 V P-P (50 mV internal)                                                   |

| Dot Density                     | Variable, 50 to 1000 dots/Div                                                      |

Fig. 13. 7T11 Sampling Sweep Unit,

# DELAY LINE

Fig. 14. 7M11 50  $\Omega$  Delay Line, Dual channel.

#### 7M11 50 Ω Delay Line, Dual Channel

| Signal Delay    | 75 ns, 30 ps or less time difference<br>between channels |

|-----------------|----------------------------------------------------------|

| Risetime        | 175 ps or less                                           |

| Attenuation     | 2X                                                       |

| Trigger Pickoff | Selectable from either channel                           |

An accessory for sequential sampling systems without internal delay lines, or for random sampling systems operated at low signal repetition rates requiring a pretrigger.

# SAMPLING HEADS **Signal Input Heads**

#### S-1 Sampling Head

#### S-2 Sampling Head

#### S-3 Sampling Head (with attached probe)

Input Resistance Risetime Random noise

**50** Ω 350 ps less than 2 mV

Input Resistance Risetime Random noise

50 Ω

25 ps

5 mV

Less than

**50** Ω 50 ps Less than 6 mV

Input Resistance 100 k $\Omega$ Input Capacitance Risetime Random noise

S-4 Sampling (3 mm input connector)

Input Resistance

Random noise

Risetime

#### S-5 Sampling Head

Input Resistance 1 MΩ Risetime (with 10X probe) Noise

1 ns Less than 500 µV

## **Special Purpose Heads**

#### S-50 Pulse Generator Head (3 mm output connector)

**Pulse Risetime Pulse Amplitude Pulse Duration**

25 ps +400 mV 100 ns, with pretrigger out

#### S-51 Trigger Countdown Head (3 mm input connector)

| Trigger Countdown  | 1 to 18 GHz   |

|--------------------|---------------|

| Input Signal Volt- | 100 mV P-P to |

| age                | 5 V P-P       |

# SECTION 2 OPERATING INSTRUCTIONS

Change information, if any, affecting this section will be found at the rear of the manual.

#### General

To effectively use the 7503, the operation and capabilities of the instrument must be known. This section describes the operation of the front-, rear-, and side-panel controls and connectors and gives first time and general operating information.

#### PRELIMINARY INFORMATION

#### **Operating Voltage**

This instrument is designed for operation from a power source with its neutral at or near earth (ground) potential with a separate safety-earth conductor. It is not intended for operation from two phases of a multi-phase system, or across the legs of a single-phase, three-wire system.

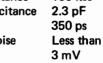

The 7503 can be operated from either a 115-volt or a 230-volt nominal line voltage source. The Line Voltage Selector assembly on the rear panel converts this instrument from one operating voltage to the other. In addition, this assembly changes the primary connections of the power transformer to allow selection of one of three regulating ranges. The assembly also includes the two line fuses to provide the correct protection for the instrument as the line voltage is changed. Use the following procedure to obtain correct instrument operation from the line voltage available.

1. Disconnect the instrument from the power source.

Loosen the two captive screws which hold the cover onto the selector assembly; then pull to remove the cover.

3. To convert from 115-volts to 230-volts nominal line voltage, or vice versa, pull out the Voltage Selector switch bar (see Fig. 2-1); turn it around  $180^{\circ}$  and plug it back into the remaining holes. Change the line-cord plug to match the power-source receptacle or use a 115-to 230-volt adapter.

Fig. 2-1. Line Voltage Selector assembly on rear panel (shown with cover removed).

#### NOTE

Color-coding of the cord conductors is as follows (in accordance with National Electrical Code):

| Line                  | Black |

|-----------------------|-------|

| Neutral               | White |

| Safety earth (ground) | Green |

4. To change regulating ranges, pull out the Range Selector switch bar (see Fig. 2-1); slide it to the desired position and plug it back in. Select a range which is centered about the average line voltage to which the instrument is to be connected (sec Table 2-1).

5. Re-install the cover and tighten the captive screws.

Before applying power to the instrument, check that the indicating tabs on the switch bars are protruding through the correct holes for the desired nominal line voltage and regulating range.

Regulating Ranges

| Range Selector                    | Regulating Range     |                      |

|-----------------------------------|----------------------|----------------------|

| Switch Position                   | 115-volts<br>nominal | 230-volts<br>nominal |

| LO (switch bar in left holes)     | 90 to 110 volts      | 180 to 220 volts     |

| M (switch bar in<br>middle holes) | 104 to 126 volts     | 208 to 252 volts     |

| H1 (switch bar in<br>right holes) | 112 to 136 volts     | 224 to 272 volts     |

This instrument may be damaged if operated with the Line Voltage Selector assembly set to incorrect positions for the line voltage applied.

The 7503 is designed to be used with a three-wire AC power system. If the three- to two-wire adapter is used to connect this instrument to a two-wire AC power system, be sure to connect the ground lead of the adapter to earth (ground). Failurc to complete the ground system may allow the chassis of this instrument to be elevated above ground potential and pose a shock hazard.

#### **Operating Temperature**

The 7503 can be operated where the ambient air temperature is between 0° C and  $+50^{\circ}$  C. This instrument can be stored in ambient temperatures between  $-55^{\circ}$  C and  $+75^{\circ}$  C. After storage at temperatures beyond the operating limits, allow the chassis temperature to come within the operating limits before power is applied.

The 7503 is cooled by convection air flow through the instrument. Components which require the most cooling are mounted externally on a heat radiator at the rear of this instrument. Adequate clearance must be provided on all sides to allow heat to be dissipated from the instrument. Do not block or restrict the air flow through the holes in the cabinet or the heat radiator on the rear. Maintain the clearance provided by the feet on the bottom and allow about two inches clearance on the top, sides, and rear (more if possible).

A thermal cutout in this instrument provides thermal protection and disconnects the power to the instrument if the internal temperature exceeds a safe operating level. Power is automatically restored when the temperature returns to a safe level. Operation in confined areas or in close proximity to heat-producing instruments may cause the thermal cutout to open more frequently.

#### **Operating Position**

A bail-type stand is mounted on the bottom of this instrument. This stand permits the 7503 to be tilted up about  $10^{\circ}$  for more convenient viewing (see Fig. 2-2).

Fig. 2-2. Instrument positioned on bail-type stand.

#### **PLUG-IN UNITS**

#### General

The 7503 is designed to accept up to three Tektronix 7-series plug-in units. This plug-in feature allows a variety of display combinations and also allows selection of bandwidth, sensitivity, display mode, etc. to meet the measurement requirements. In addition, it allows the oscilloscope system to be expanded to meet future measurement requirements. The overall capabilities of the resultant system are in large part determined by the characteristics of the plug-in selected. A list of the currently available plug-ins along with their major specifications, is given in Section 1. For more complete information, see the current Tektronix, Inc. catalog.

#### Installation

To install a plug-in unit into one of the plug-in compartments, align the slots in the top and bottom of the plug-in with the associated guide rails in the plug-in compartment. Push the plug-in unit firmly into the compartment until it locks into place. To remove a plug-in, pull the release latch on the plug-in unit to disengage it and pull the unit out of the compartment. Plug-in units can be removed or installed without turning off the instrument power. However, installation of the plug-ins with the power on may on without turning off the instrument power. However, installation of the plug-ins with the power on may on occasion cause the power-supply protection circuits of the 7503 to interrupt the power to the instrument. This is due to the sudden surge of current that is demanded as a plug-in is connected to the power-supply circuits. If the 7503 is not operating after the plug-ins are inserted, turn off the POWER switch momentarily and return it to ON.

It is not necessary that all of the plug-in compartments be filled to operate the instrument; only the plug-ins needed for the measurement to be made are necessary. However, at environmental extremes, interference may be radiated into this instrument through the open plug-in compartment; also, the instrument may radiate interference into other equipment. Blank plug-in panels are available from Tektronix, Inc. to cover the unused compartment; order Tektronix Part No. 016-0155-00.

When the 7503 is calibrated in accordance with the calibration procedure given in this instruction manual, the vertical and horizontal gain are normalized. This allows calibrated plug-in units to be changed from one plug-in compartment to another without recalibration. However, the basic calibration of the individual plug-in units should be checked when they are installed in this system to verify their measurement accuracy. See the operating instructions section of the plug-in unit instruction manual for verification procedure.

The plug-in feature of the 7503 allows a variety of display modes with many different plug-ins. Specific information for obtaining these displays is given later, in this section. However, the following information is provided here to aid in plug-in installation.

To produce a single-trace display, install a single-channel vertical unit (or dual-channel unit set for single-channel operation) in either of the vertical compartments. For dual-trace displays, either install a dual-channel vertical unit in one of the vertical compartments or install a singlechannel vertical unit in each vertical compartment. A combination of a single-channel and dual- channel vertical unit allows a three-trace display; likewise, a combination of two dual-channel vertical units allows a four-trace display.

For time-base displays, a 7B-series plug-in is placed in the Horizontal compartment.

X-Y displays can be obtained in two ways with the 7503 system. If a 7B-series time- base plug-in is available which

has an amplifier feature, the X signal can be routed through one of the vertical units via the internal-trigger pickoff circuitry to the horizontal system. Then, the vertical (Y) signal is connected to the remaining vertical unit. Also, a 7Aseries amplifier plug-in can be installed in the horizontal compartment for X-Y operation.

Special purpose plug-ins may have specific restrictions regarding the plug-in compartments in which they can be installed. This information will be given in the instruction manuals for these plug-ins.

#### CONTROLS AND CONNECTORS

#### General

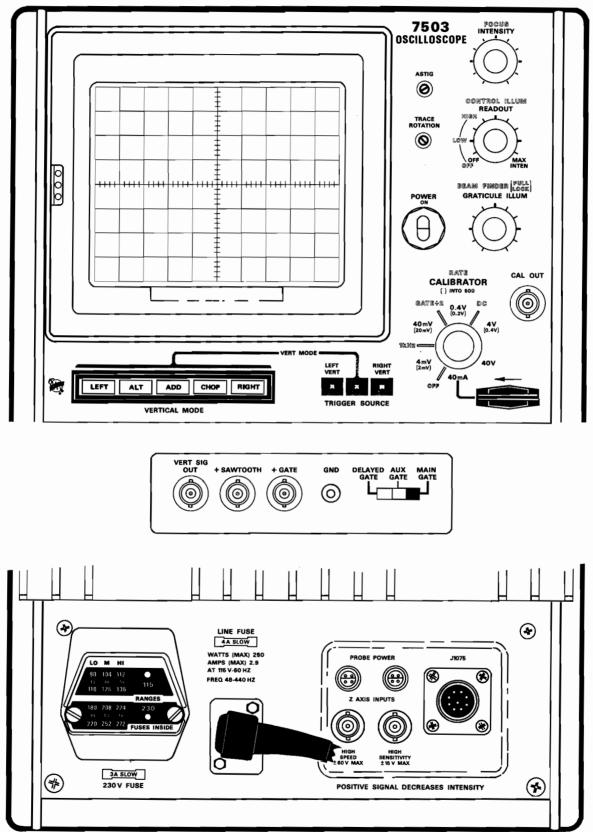

The major controls and connectors for operation of the 7503 are located on the front panel of the instrument. Several auxiliary functions are provided on the side and rear panels. Fig. 2-3 shows the front, side, and rear panels of the 7503. To make full use of the capabilities of this instrument, the operator should be familiar with the function and use of each of these controls and connectors. A brief description of each control and connector is given here. More detailed operating information is given under General Operating Information.

#### Cathode-Ray Tube (CRT)

ASTIG Screwdriver adjustment used in conjunction with the FOCUS control to obtain a well-defined display. Does not require readjustment in normal use. INTENSITY Controls brightness of the trace. Control is inoperative when the HORIZ compartment is vacant. Provides adjustment for optimum FOCUS display definition. **BEAM FINDER** Compresses display within graticule area independent of display (PULL LOCK) position or applied signals. Momentary actuation provided when button is pressed; display remains compressed when knob is pulled outward to lock it in the "find" position. READOUT Controls brightness of the readout portion of the CRT display. In the fully counterclockwise position, the

Readout System is inoperative.

#### **Operating Instructions-7503**

Fig. 2-3. Front-, side- and rear-panel controls and connectors.

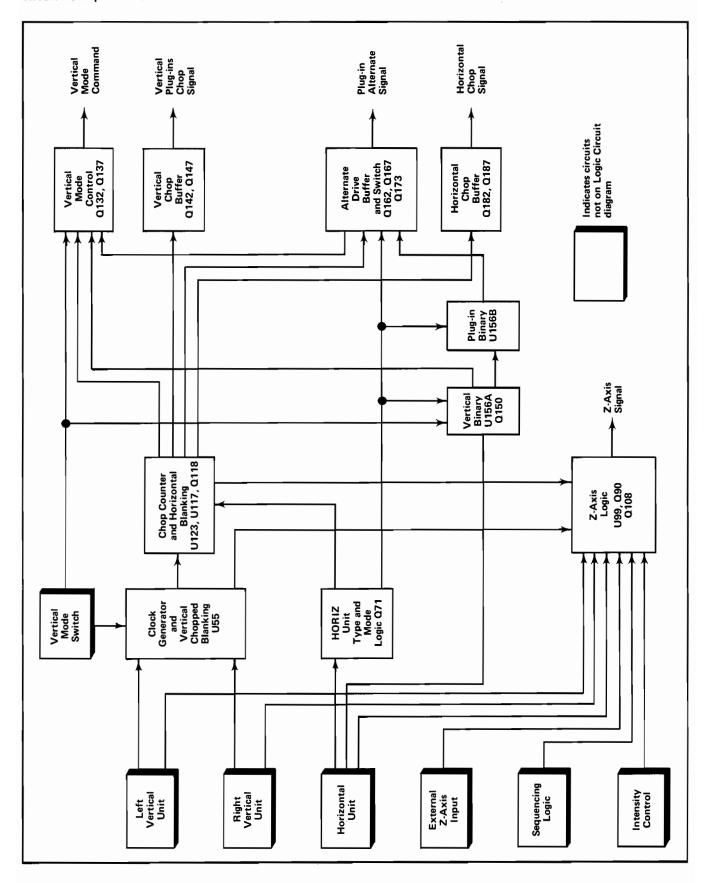

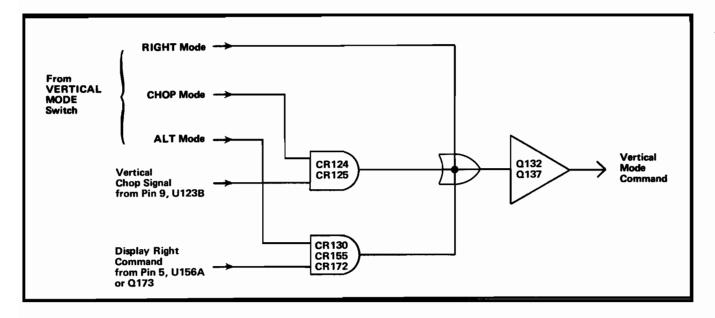

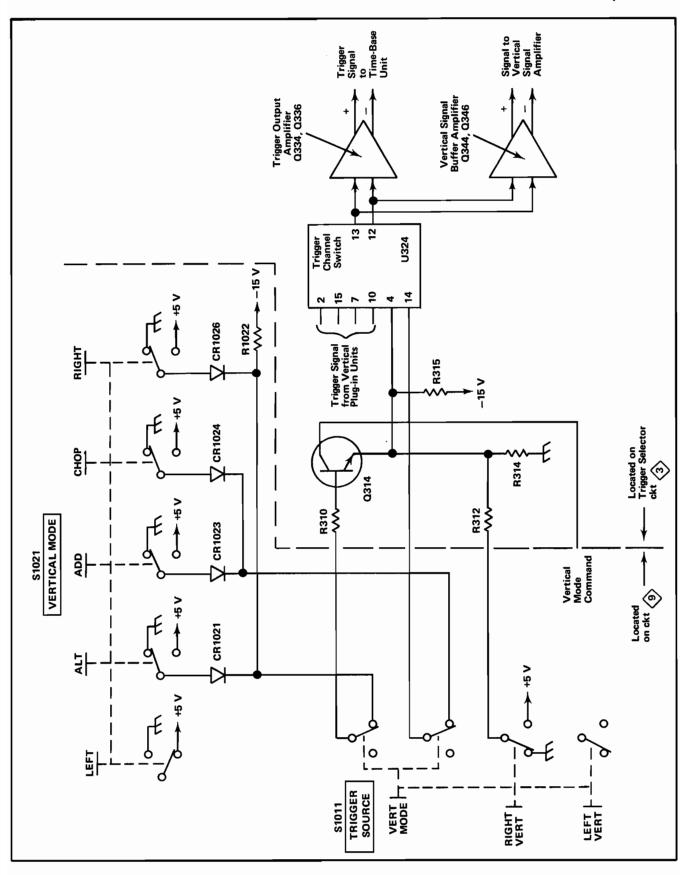

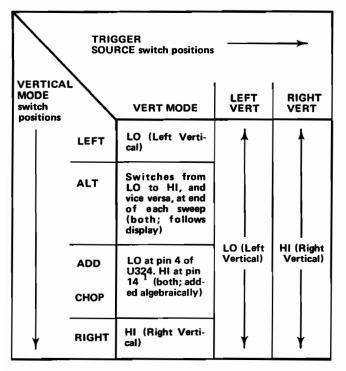

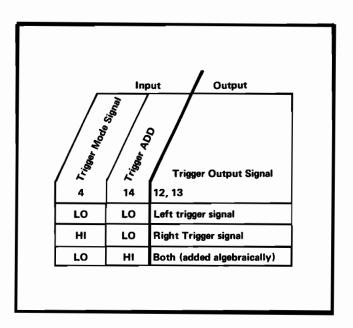

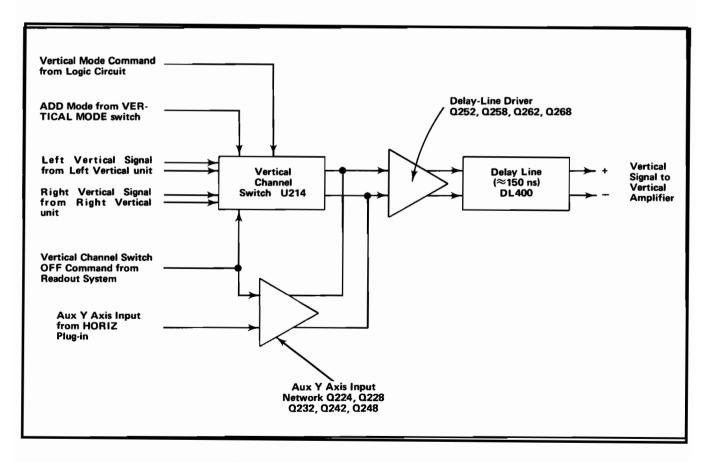

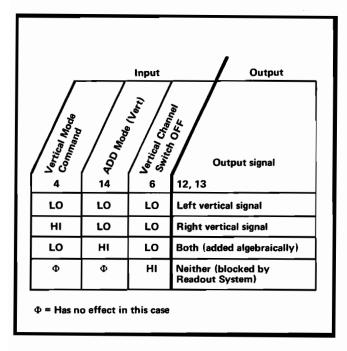

CONTROL ILLUM Calibrator Controls illumination level of pushbutton switches on the 7503 and the associated plug-ins. OFF: All pushbutton lights off. LOW: All pushbuttons illuminated at low intensity. HIGH: Pushbuttons illuminated at maximum intensity. TRACE ROTATION Screwdriver adjustment to align RATE trace with horizontal graticule lines. GRATICULE ILLUM Controls graticule illumination. **Mode Selectors** VERTICAL MODE Selects vertical mode of operation. LEFT: Signal from plug-in unit in LEFT VERT compartment is displayed. ALT: Signals from plug-in units in both LEFT VERT and RIGHT VERT compartments are displayed. Display switched between vertical plug-ins after each sweep. ADD: Signals from plug-in units in both LEFT VERT and RIGHT VERT compartments are algebraically added and the algebraic sum displayed on the CRT. CHOP: Signals from plug-in units in both LEFT VERT and RIGHT VERT compartments are displayed. Display switched between vertical plug-ins at a one-megahertz repetition rate. RIGHT: Signal from plug-in unit in **RIGHT VERT compartment is dis-**Outputs played. CAL OUT TRIGGER SOURCE Selects source of internal trigger signal for time-base unit in the Horizontal compartment. VERT MODE: Trigger signal auto-40 mA Current matically follows the vertical dis-Loop play except in CHOP; then the trigger signal is the same as for ADD. LEFT VERT: Trigger signal is obtained from plug-in unit in LEFT VERT SIG OUT VERT compartment. **RIGHT VERT:** Trigger signal is obtained from plug-in unit in RIGHT VERT compartment.

۲

CALIBRATOR

Selects amplitude of output at CAL OUT connector or 40 mA current through current loop. Outputs available from four millivolts to 40 volts, into high-impedance load, in decade steps, or from two millivolts to 0.4 volt into 50-ohm load (output into 50 ohms shown in brackets on panel).

Selects the mode and repetition rate of the output from the Calibrator.

OFF: Calibrator is disabled. No current through current loop and no voltage at CAL OUT connector.

1 kHz: Calibrator operates at one--kilohertz rate, 40-milliampere square-wave current through current loop or square-wave voltage (amplitude determined by CALI-BRATOR switch) at CAL OUT connector.

GATE ÷2: Calibrator operates at one-half the repetition rate of the gate signal from the time-base unit in the Horizontal compartment. 40-milliampere square-wave current through current loop or squarewave voltage (amplitude determined by CALIBRATOR switch) at CAL OUT connector.

DC: DC voltage available at CAL OUT connector (amplitude determined by CALIBRATOR switch), or 40 milliampere DC current through current loop.

Provides positive-going calibrator output when voltage operation is selected.

Probe loop providing calibrator current output when CALIBRATOR switch is set to 40 mA postiion.

#### Side Panel

Provides output signal from the vertical plug-ins. Source of the output signal at the VERT SIG OUT connector is selected by the TRIGGER SOURCE switch.

- + SAWTOOTH Positive-going sample of sawtooth signal from a time-base unit in the HORIZ compartment.

- + GATE Positive-going gate signal from a time-base unit in the HORIZ compartment. Switch allows selection of one of three gate signals: MAIN GATE, coincident with the sweep being displayed; AUX GATE, depends upon type of time-base unit; DELAYED GATE, coincident with the delay period (delaying sweep time-base units only).

- GND Binding post to establish common ground between the 7503 and any associated equipment.

#### **Rear Panel**

Line Voltage Selector (not labeled) Switching assembly to select the nominal operating voltage and the line voltage range. The assembly also includes the line fuses.

Voltage Selector: Selects nominal operating voltage range (115 or 230 volts).

Range Selector: Selects line voltage range (low, medium, high).

PROBE POWER Power source for active probe systems.

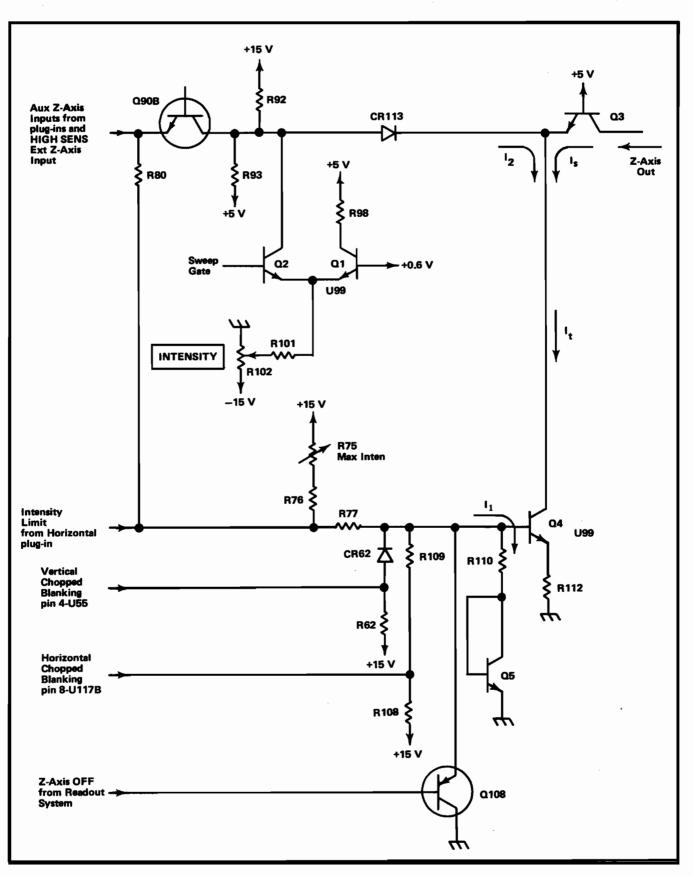

Z-AXIS INPUTS Input connectors for intensity modulation of the CRT display.

> HIGH SPEED: Input connector for high-amplitude Z-axis signals; usable over full frequency range of instrument.

> HIGH SENSITIVITY: Input connector for low-amplitude Z-axis signals; usable for signals with repetition rates of DC to 10 megahertz; input voltage derating necessary between two and 10 megahertz.

J1075 Nine-pin connector which provides remote single-sweep reset and ready indication for the time-base unit in the HORIZ compartment (with compatible time-base units only).

#### **FIRST-TIME OPERATION**

#### General

The following steps demonstrate the use of the controls and connectors of the 7503. It is recommended that this procedure be followed completely for familiarization with this instrument.

#### Set-up Information

1. Set the front-panel controls as follows:

| INTENSITY       | Counterclockwise |

|-----------------|------------------|

| FOCUS           | Midrange         |

| BEAM FINDER     | Released         |

| READOUT         | OFF              |

| CONTROL ILLUM   | HIGH             |

| GRATICULE ILLUM | Counterclockwise |

| POWER           | OFF              |

| CALIBRATOR      | 4 V              |

| RATE            | 1 kHz            |

| VERTICAL MODE   | LEFT             |

| TRIGGER SOURCE  | VERT MODE        |

|                 |                  |

2. Connect the 7503 to a power source that meets the voltage and frequency requirements of this instrument. If the available line voltage is outside the limits of the Line Voltage Selector switch (on rear panel), see Operating Voltage in this section.

3. Insert Tektronix 7A-series amplifier units into both the LEFT VERT and RIGHT VERT compartments. Insert a Tektronix 7B-series time-base unit into the HORIZ compartment.

4. Set the POWER switch to ON. Allow several minutes warmup so the instrument reaches a normal operating temperature before proceeding.

5. Set both vertical units for a vertical deflection factor of two volts/division and center the vertical position controls.

6. Set the time-base unit for a sweep rate of 0.5 millisecond/division in the auto, internal trigger mode.

7. Advance the INTENSITY control until the trace is at the desired viewing level (near midrange).

8. Connect the CAL OUT connector to the input connector of the left vertical unit with a BNC-to-BNC patch cord (supplied accessory).

۲

9. Adjust the FOCUS control for a sharp, well-defined display over the entire trace length. (If focused display cannot be obtained, see Astigmatism Adjustment in this section.)

10. Disconnect the input signal and position the trace with the left vertical unit position control so it coincides with the center horizontal line of the graticule.

11. If the trace is not parallel with the center horizontal line, see Trace Alignment Adjustment in this section.

12. Rotate the GRATICULE ILLUM control throughout its range and notice that the graticule lines are illuminated as the control is turned clockwise (most obvious with tinted filter installed). Set control so graticule lines are illuminated as desired.

#### Calibration

13. Connect the CAL OUT connector to the input connectors of both vertical units with the BNC-to-BNC jumper leads.

14. The display should be two divisions in amplitude with five complete cycles shown horizontally. An incorrect display indicates that the plug-ins need to be recalibrated. See the instruction manual of the applicable unit for complete information.

#### Vertical Mode

15. Notice that the position control of only the left vertical unit has any effect on the displayed trace. Position the start of the trace to the farthest left line of the graticule with the time-base unit position control, and move the trace to the upper half of the graticule with the left vertical unit position control.

16. Press the RIGHT button of the VERTICAL MODE switch.

17. Notice that the position control of only the right vertical unit has any effect on the displayed trace. Move the display to the bottom half of the graticule with the right vertical unit position control.

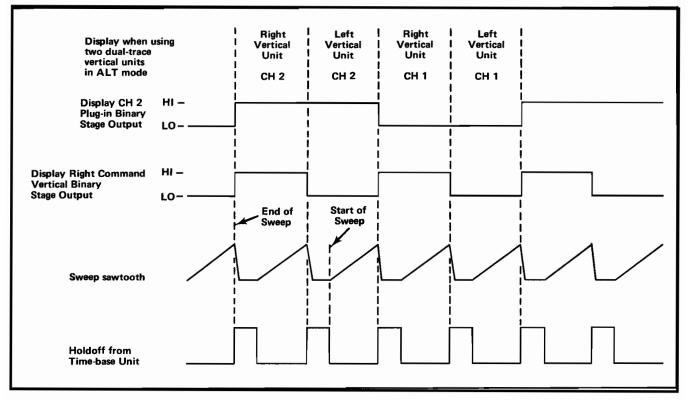

18. Press the ALT button of the VERTICAL MODE switch. Notice that two traces are displayed on the CRT. The top trace is produced by the left vertical unit, and the bottom trace is produced by the right vertical unit. Reduce the sweep rate of the time-base unit to 50 milliseconds/

division. Notice that the display alternates between the left and right vertical units after each sweep. Turn the time-base sweep rate switch throughout its range. Notice that the display alternates between vertical units at all sweep rates.

19. Press the CHOP button of the VERTICAL MODE switch. Turn the time-base unit sweep rate switch throughout its range. Notice that a dual-trace display is presented at all sweep rates, but unlike ALT, both vertical units are displayed on a time-sharing basis. Return the time-base unit sweep rate switch to 0.5 millisecond/division.

20. Press the ADD button of the VERTICAL MODE switch. The display should be four divisions in amplitude. Notice that the position control of either vertical unit moves the display. Return the VERTICAL MODE switch to the LEFT position.

#### Triggering

21. Center the display on the CRT with the left vertical unit position control. Disconnect the input signal from the right vertical unit input connector. Press all of the VER-TICAL MODE switch buttons in sequence. Notice that a stable display is obtained in all positions of the VERTICAL MODE switch (straight line in RIGHT position).

22. Press the LEFT VERT button of the TRIGGER SOURCE switch. Again, press all of the VERTICAL MODE buttons in sequence. Notice that the display is again stable in all positions, as in the previous step.

23. Press the RIGHT VERT button of the TRIGGER SOURCE switch. Press all the VERTICAL MODE switch buttons in Sequence and notice that a stable display cannot be obtained in any position. This is because there is no input signal connected to the right vertical unit.

#### **Control Illumination**

24. Notice that the selected switch buttons of the 7503 and the plug-in units are illuminated.

25. Change the CONTROL ILLUM switch to the LOW position. Notice that the selected buttons of the 7503 and the plug-ins are illuminated at a reduced intensity.

26. Change the CONTROL ILLUM switch to the OFF position. Notice that none of the buttons are illuminated.

#### Readout

27. Turn the READOUT control clockwise until a digital display is visible within the top or bottom division of

the CRT. Change the deflection factor of the vertical unit selected for display. Notice that the readout display changes as the deflection factor is changed. Change the sweep rate of the time-base unit. Notice that the readout display for the time-base unit changes also as the sweep rate is changed.

28. Set the time-base unit for magnified operation. Notice that the readout display changes to indicate the correct magnified sweep rate. If a readout-coded 10X probe is available for use with the vertical unit, connect it to the input connector of the vertical plug-in. Notice that the deflection factor indicated by the readout is increased by 10 times when the probe is added. Return the time-base unit to normal sweep operation and disconnect the probe.

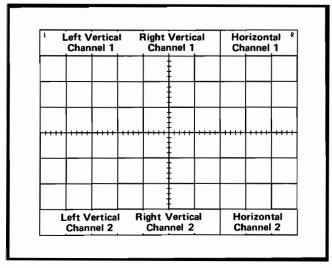

29. Press all of the VERTICAL MODE switch buttons in sequence. Notice that the readout from a particular plug-in occupies a specific location on the display area. If either of the vertical units is a dual-trace unit, notice that the readout for channel 2 appears within the lower division of the CRT.

#### **Beam Finder**

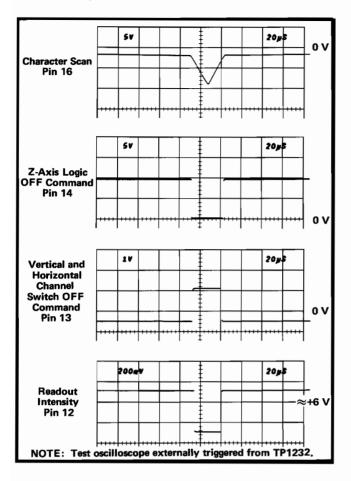

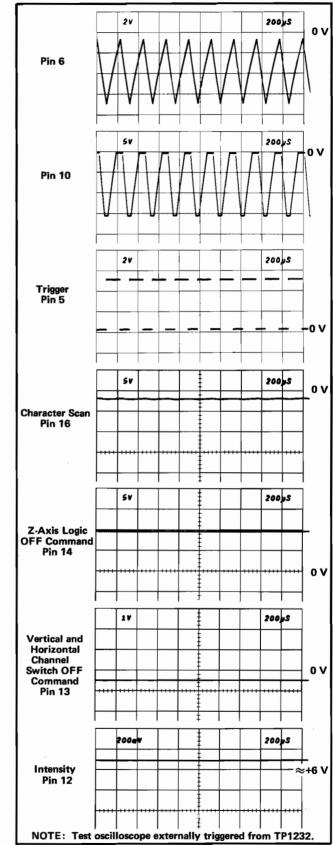

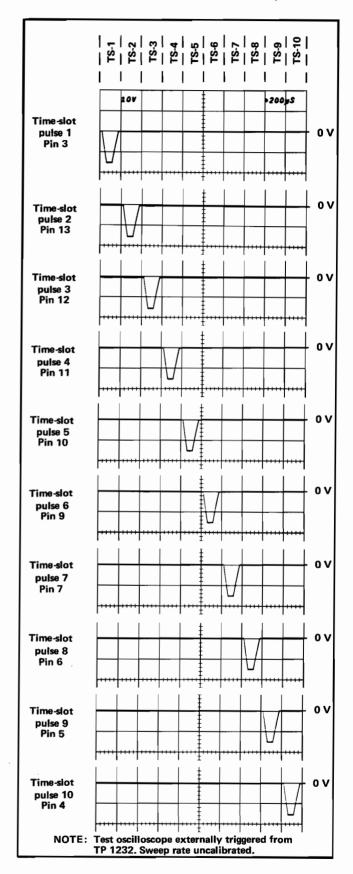

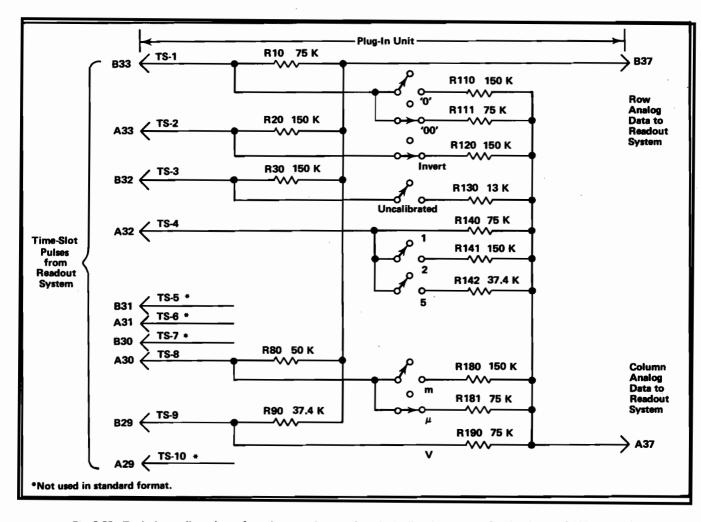

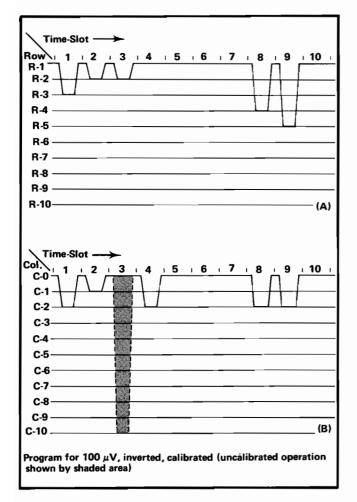

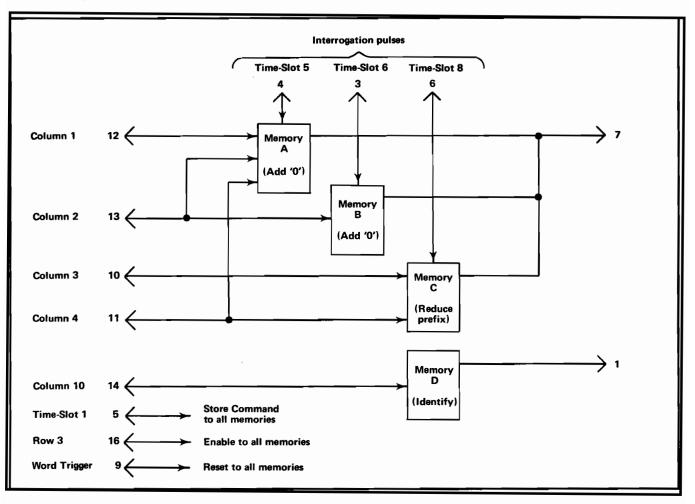

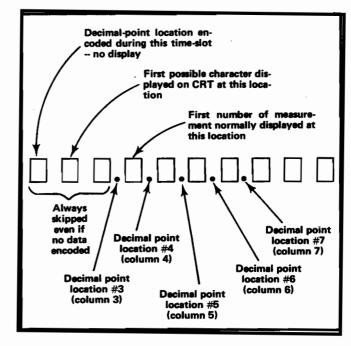

30. Set the vertical deflection factor of the vertical plug-in which is displayed to 0.1 volt/division. Notice that no square wave display is visible, since the deflection exceeds the scan area of the CRT.