# WARNING

.

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO. REFER TO OPERATORS SAFETY SUMMARY PRIOR TO PERFORMING ANY SERVICE.

# PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL.

# 7A42 LOGIC TRIGGERED VERTICAL AMPLIFIER

# **SERVICE (VOLUME 1)**

For Qualified Service Personnel Only

# INSTRUCTION MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

Serial Number \_\_

First Printing May 1983 Revised MAR 1988

070-4286-00 Product Group 42

. - .

Copyright  $\stackrel{<}{<}$  1983 Tektronix, Inc. All rights reserved. Contents of this publication may not be reproduced in any form without the written permission of Tektronix, Inc.

Products of Tektronix, Inc. and its subsidiaries are covered by U.S. and foreign patents and/or pending patents.

TEKTRONIX, TEK, SCOPE-MOBILE, and registered trademarks of Tektronix, Inc. TELEQUIPMENT is a registered trademark of Tektronix U.K. Limited.

Printed in U.S.A. Specification and price change privileges are reserved.

### INSTRUMENT SERIAL NUMBERS

Each instrument has a serial number on a panel insert, tag, or stamped on the chassis. The first number or letter designates the country of manufacture. The last five digits of the serial number are assigned sequentially and are unique to each instrument. Those manufactured in the United States have six unique digits. The country of manufacture is identified as follows:

| B000000 | Tektronix, Inc., Beaverton, Oregon, USA               |

|---------|-------------------------------------------------------|

| 100000  | Tektronix Guernsey, Ltd., Channel Islands             |

| 200000  | Tektronix United Kingdom, Ltd., London                |

| 300000  | Sony/Tektronix, Japan                                 |

| 700000  | Tektronix Holland, NV, Heerenveen,<br>The Netherlands |

# **TABLE OF CONTENTS**

| SECTION 1-G  | ENERAL INFORMATION Page                  | GENERAL  |

|--------------|------------------------------------------|----------|

| TECH         | INICAL MANUALS 1-1                       |          |

|              | PERATORS MANUAL1-1                       |          |

| S            | ERVICE MANUAL 1-1                        |          |

|              | ATION                                    |          |

|              | AL INSPECTION1-2                         |          |

| OPER         | RATING TEMPERATURE 1-2                   |          |

| INST         | ALLING THE 7A42 IN THE MAINFRAME 1-2     |          |

| MAIN         | FRAME COMPATIBILITY 1-2                  | SECTION  |

| PACH         | KAGING FOR SHIPMENT 1-3                  | BLOCK D  |

| SPECIFICATIO | N                                        | DES      |

| STANDARD AC  | CCESSORIES1-15                           | DETAILED |

| OPTIONAL AC  | CESSORIES (NOT INCLUDED)                 | FRO      |

| PROBES       |                                          |          |

| OPERATING IN | STRUCTIONS1-15                           |          |

| CONTROLS     | , CONNECTORS, AND INDICATORS 1-15        |          |

| DETAILED OPE | ERATING INFORMATION1-18                  |          |

| SELF-TE      | ST 1-18                                  | 3        |

| FRONT-       | PANEL INITIALIZATION1-18                 | ATT      |

| BATTER       | Y BACKUP 1-19                            |          |

|              | OR MESSAGES 1-19                         |          |

|              | CONNECTIONS 1-21                         |          |

| RECO         | DMMENDED PROBES1-23                      | CH       |

| PF           | ROBE COMPENSATION1-23                    |          |

| C            | OAXIAL CABLES1-23                        |          |

| CRT RE       | ADOUT                                    |          |

| POSITIO      | N                                        | DIS      |

|              |                                          |          |

| STATUS       | INDICATORS (CH1, CH2, CH3, CH4) 1-24     |          |

|              | LAY1-24                                  |          |

|              | TTL                                      | TRI      |

| GND          |                                          | ANI      |

|              | ΙΜΩ                                      |          |

|              | OP1-24                                   |          |

|              | R FUNCTION                               |          |

|              | IGGER FUNCTION AND B TRIGGER             |          |

|              | CTION1-25                                | EDO      |

|              | EN B NESTED TRIGGERING1-25               | AT       |

|              | EW1-25                                   |          |

|              | R FILTER                                 |          |

|              | DCK SYNC                                 | 1        |

|              | PE SELECT 1-25                           | 1        |

|              | CLOCK INPUT 1-26                         | 1000     |

| RESET II     | CUNTRUES, CUNNECTURES, AND INDIVERTORS . | TRI      |

|              |                                          |          |

|              | SELF-TEST                                |          |

|              | FRONT-PANEL INITIALIZATION               | 1,19     |

|              | BATTERY BACKUP                           | 1.10     |

|              | OPERATOR MESSAGES                        |          |

|              | SIGNAL CONNECTIONS                       |          |

|              | RECOMMENDED PROBES                       | 1-23     |

|              | PROBE COMPENSATION                       |          |

|              | COAXIAL CABLES                           |          |

|              | CRT READOUT                              |          |

|              | POSITION                                 |          |

|              | GAIN                                     |          |

|              | STATUS INDICATORS (CH1, CH2, CH3, CH4)   |          |

|              | DISPLAY.                                 |          |

| SIC.         | ECL/TTL.                                 |          |

|              | GND                                      |          |

|              | 50Ω/1ΜΩ                                  |          |

|              | ALT/CHOP                                 |          |

|              | TRIGGER FUNCTION                         |          |

| GENERAL INFORMATION (CONT) | Page |

|----------------------------|------|

| AND                        | 1-29 |

| OR                         | 1-29 |

| CLEAR                      | 1-30 |

| NOT                        | 1-30 |

| EDGE                       | 1-30 |

|                | DRY OF OPERATION                       |

|----------------|----------------------------------------|

|                |                                        |

|                | DN                                     |

| DETAILED CIRCU | T OPERATION                            |

| FRONT PAN      | IEL DISPLAY AND CONTROL                |

| KEYBOA         | RD DECODER2-8                          |

|                | L STATUS AND SWITCH LED                |

| DRIVER.        |                                        |

| THRESH         | OLD DISPLAY DRIVER                     |

|                | LED DRIVER                             |

| ATTENIIAT      | ORS AND CONTROL                        |

|                | RE RELAY DRIVERS                       |

|                | AD COMPARATORS                         |

|                | GER PICKOFF                            |

|                | WITCHING AND AMPLIFIERS                |

|                |                                        |

|                | L AMPLIFIERS                           |

|                | TION CONTROL                           |

|                | L SWITCHES2-11                         |

| DISPLAY CO     | ONTROL                                 |

|                | S DECODER AND LATCH                    |

|                | CONTROL                                |

|                |                                        |

|                | OMPARATORS, BOOLEAN LOGIC,             |

|                | IS                                     |

|                | OLD DACS2-12                           |

|                | ATORS                                  |

|                | N LOGIC                                |

| TRIGGER        | R FILTERS                              |

|                | CTORS2-13                              |

| A THEN B L     | OGIC AND TRIGGER I/O2-13               |

|                | B LOGIC2-13                            |

| TRIGGER        | OUT AMPLIFIER                          |

| RESET B        | UFFER                                  |

| EXT CLO        | CK                                     |

| TRIGGER        | 8 VIEW SELECT                          |

| TRIGGER C      | ONTROL                                 |

|                | יייייייייייייייייייייייייייייייייייייי |

| 1-18           | THRESHOLD DISPLAY DRIVER               |

| 1-18           | MATRIX LED DRIVER                      |

| 1-18           | ATTENUATORS AND CONTROL                |

| 1-19           | ARMATURE RELAY DRIVERS                 |

| 1-19           | OVERLOAD COMPARATORS                   |

| 1-21           | TRIGGER PICKOFF                        |

| 1-23           | CHANNEL SWITCHING AND AMPLIFIERS.      |

|                | CHANNEL AMPLIFIERS                     |

|                | POSITION CONTROL                       |

|                | CHANNEL SWITCHES                       |

| 1-24           | DISPLAY CONTROL                        |

|                | ADDRESS DECODER AND LATCH              |

| ) 1-24         | DISPLAY CONTROL                        |

|                | HORN                                   |

|                | TRIGGER COMPARATORS, BOOLEAN LOO       |

|                | AND FILTERS                            |

|                | THRESHOLD DACS                         |

| 1-24           | INNESHOLD DAGS                         |

COMPARATORS .....

BOOLEAN LOGIC .....

# **TABLE OF CONTENTS (CONT)**

| THEORY OF OPERATION (CONT)                             | Page   | ма  |

|--------------------------------------------------------|--------|-----|

| AUTO RESTART                                           |        | DI/ |

| WAITSTATE GENERATOR                                    | . 2-16 |     |

| REAL TIME CLOCK                                        |        |     |

| GENERAL INPUT LATCH                                    |        |     |

| PROBE OFFSET ACQUISITION                               | . 2-16 |     |

| PROBE CODING AND DIAGNOSTIC HOOKS                      |        |     |

| MUX                                                    |        |     |

| DIAGNOSTIC HOOKS                                       |        |     |

| READOUT                                                | . 2-19 |     |

| POWER SUPPLY AND DISTRIBUTION                          |        |     |

| POWER STAGE                                            |        |     |

| RECTIFIERS AND FILTERS                                 |        |     |

|                                                        |        |     |

| PULSE WIDTH MODULATION (PWM)                           | . 2-21 |     |

| CONTROLLER                                             | 2-21   |     |

| DRIVERS                                                |        |     |

| SNUBBER                                                |        |     |

| ATTENUATOR SUPPLIES                                    |        |     |

| ATTENDATOR SOFFEIES                                    |        |     |

| SECTION 3MAINTENANCE                                   |        |     |

| PREVENTIVE MAINTENANCE                                 | . 3-1  |     |

| PLUG-IN PANEL REMOVAL                                  |        |     |

| CLEANING                                               | 3-1    |     |

| EXTERIOR                                               | 3-1    |     |

| INTERIOR                                               | . 3-1  |     |

| LUBRICATION                                            |        |     |

| VISUAL INSPECTION                                      | . 3-4  |     |

| SEMICONDUCTOR CHECKS                                   |        |     |

| ELECTRICAL ADJUSTMENT                                  | . 3-4  |     |

| ADJUSTMENT AFTER REPAIR                                |        |     |

| TROUBLESHOOTING                                        |        |     |

| TROUBLESHOOTING AIDS                                   |        |     |

| DIAGRAMS                                               |        |     |

| CIRCUIT BOARD ILLUSTRATIONS                            |        |     |

| COMPONENT COLOR CODING                                 |        |     |

| WIRING COLOR CODE<br>SEMICONDUCTOR LEAD CONFIGURATIONS |        |     |

| STATIC-SENSITIVE DEVICE                                | . 3-5  |     |

| CLASSIFICATION                                         | 2.5    |     |

| MULTI-PIN CONNECTOR IDENTIFICATION                     |        |     |

| TROUBLESHOOTING EQUIPMENT                              |        |     |

| TROUBLESHOOTING TECHNIQUES                             |        |     |

| 1. CHECK CONTROL SETTINGS                              |        |     |

| 2. CHECK ASSOCIATED EQUIPMENT                          |        |     |

| 3. VISUAL CHECK                                        |        |     |

| 4. ISOLATE TROUBLE TO A CIRCUIT                        |        |     |

| 5. CHECK INSTRUMENT ADJUSTMENT                         | . 3-9  |     |

| 6. CHECK VOLTAGES                                      |        |     |

| 7. CHECK INDIVIDUAL COMPONENTS                         |        |     |

| TRANSISTORS                                            |        |     |

| INTEGRATED CIRCUITS                                    | . 3-9  |     |

| DIODES                                                 | 3-10   |     |

| RESISTORS                                              |        |     |

| CAPACITORS                                             | 3-10   |     |

| 8. REPAIR AND ADJUST THE CIRCUIT                       | 3-10   |     |

| MAINTENANCE (CONT)                     | Page   |

|----------------------------------------|--------|

| DIAGNOSTICS AND TROUBLESHOOTING        | 2 10   |

| SELF TEST                              |        |

|                                        |        |

| EXTENDED DIAGNOSTICS                   | . 3-12 |

| BACKGROUND INFORMATION ON              |        |

| SIGNATURE ANALYSIS                     | . 3-15 |

| EXTENDING CIRCUIT BOARDS FOR           |        |

| TROUBLESHOOTING                        |        |

| HOW TO EXTEND THE A6 TRIGGER BOARD.    | 3-15   |

| HOW TO EXTEND THE A7 DIGITAL BOARD     | 3-18   |

| WHAT TO DO IF THE 7A42 DOES NOT        |        |

| RESPOND TO FRONT-PANEL CONTROLS        | 3-18   |

| FORCED INSTRUCTION FREERUN             |        |

| EXTERNAL BUS EXERCISE (XBUSX)          |        |

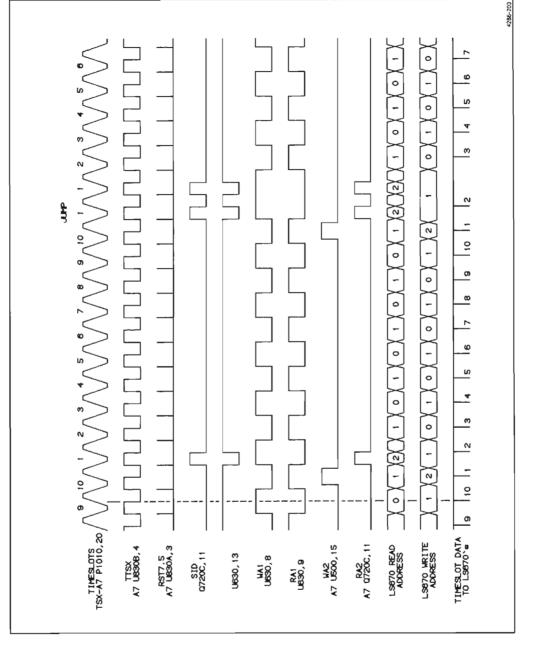

| INTERVAL 1 (SEE FIG. 3-9)              |        |

| INTERVAL 2                             |        |

| INTERVAL 3                             |        |

|                                        |        |

|                                        |        |

| EXTERNAL BUS OPERATION                 |        |

| FRONT-PANEL LED OPERATION              |        |

| FRONT PANEL KEYS AND DVM DISPLAY       |        |

| PROBE OFFSET DAC AND COMPARATOR        |        |

| AUTO RESTART CIRCUIT                   |        |

| DIAGNOSTIC TEST DESCRIPTIONS           | 3-23   |

| ROMS                                   | 3-25   |

| 1—ROM A8U145                           | 3-25   |

| 2ROM A8U245                            | 3-25   |

| 3—ROM A8U340                           |        |

| 4ROM A8U345                            |        |

| RAMS                                   |        |

| 5-RAM A8U615                           |        |

| 6—RAM A8U615                           |        |

| MPU BOARD MISCELLANEOUS                |        |

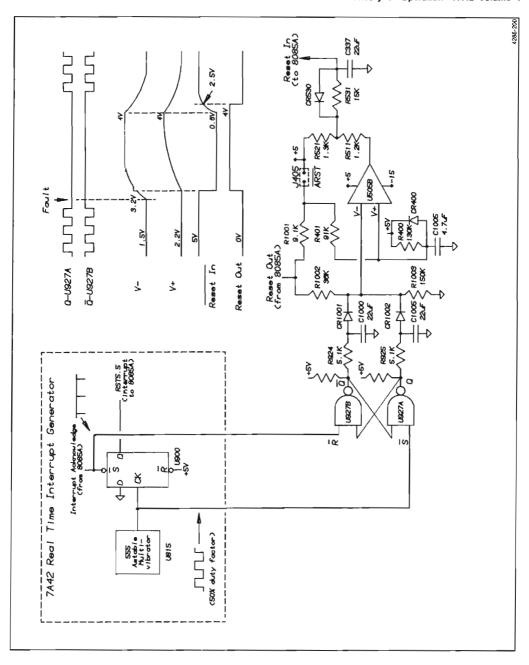

| 7-REAL TIME INTERRUPT CIRCUIT (RST5.5) | 3-20   |

|                                        | 0.00   |

| ABU815, ABU900B                        |        |

| 8-EXTERNAL BUS CLEAR                   |        |

| 9-WAIT STATE GENERATOR A8U835          | 3-26   |

| 10-PROBE OFFSET ADC A8U600.            |        |

| A8U505A                                |        |

| DIGITAL BOARD MISCELLANEOUS            | 3-27   |

| 11-DISPLAY CONTROL A7U700, A7U800,     |        |

| A7U820, A7U900                         | 3-27   |

| 12-READOUT; RST7.5 A8U830A, B, D, AND  |        |

| A8Q720A                                | 3-27   |

| 13-READOUT; SID A7Q720C                | 3-28   |

| A6 TRIGGER BOARD DIAGNOSTICS           | 3-28   |

| LEGEND                                 |        |

| EXAMPLE #1                             |        |

| EXAMPLE #2                             |        |

| INSTRUCTIONS                           |        |

| TROUBLESHOOTING TIPS FOR THE           | 5-51   |

| TRIGGER BOARD                          | 0.00   |

|                                        |        |

|                                        | J-JO   |

| A1. TRIGGER CONTROL (WRMD) LATCH,      |        |

| A6U1010                                | 3-36   |

| A2. TRIGGER CONTROL LEVEL SHIFTING     |        |

| TRANSISTORS, RESET BUFFER              | 3-36   |

# **TABLE OF CONTENTS (CONT)**

|                                      | Page |

|--------------------------------------|------|

| A3. TRIGGER CONTROL SHIFT            |      |

| REGISTERS                            |      |

| TRIGGER INTERCONNECT                 | 3-36 |

| B1. TRIGGER TEST BIT INTERCONNECT    | 3-36 |

| B2. TRIGGER FILTER INTERCONNECT      | 3-37 |

| B3. A THEN B GATE OUTPUT CABLE       | 3-37 |

| THRESHOLD DACS AND COMPARATORS       | 3-37 |

| C1. THRESHOLD DACS                   | 3-37 |

| C2. THRESHOLD COMPARATORS            |      |

| BOOLEAN LOGIC AND TRIGGER FILTERS    |      |

| D1. BOOLEAN LOGIC                    |      |

| D2. TRIGGER FILTERS                  |      |

| D3. TRIGGER FILTER CURRENT SOURCES   |      |

| A THEN B LOGIC                       |      |

| E1. A THEN B LOGIC                   |      |

|                                      |      |

| EDGE DETECTORS                       |      |

| F1. SYNC CONTROL LINES               |      |

| F2. EDGE-DETECTOR CIRCUITS           |      |

| F3. MULTIPLEXERS                     |      |

| EXTERNAL CLOCK                       |      |

| G1. CLOCK CONTROL LINES              |      |

| G2. EXTERNAL CLOCK LOGIC             |      |

| TRIGGER BOARD TEST DESCRIPTIONS      | 3-41 |

| TRIGGER CONTROL                      | 3-41 |

| 14—TRIGGER CONTROL REGISTER          | 3-41 |

| 15—TRIGGER PICKOFF A/D-1             | 3-41 |

| 16-TRIGGER PICKOFF A/D-1             | 3-41 |

| 17-TRIGGER PICKOFF A/D-1             | 3-41 |

| 18-TRIGGER PICKOFF A/D-1             |      |

| 19-TRIGGER PICKOFF A/D-2             |      |

| 20-TRIGGER PICKOFF A/D-2             |      |

| 21-TRIGGER PICKOFF A/D-2             |      |

| 22-TRIGGER PICKOFF A/D-2             |      |

| 23-BOOLEAN LOGIC-FUNCTION A          |      |

| 24-BOOLEAN LOGIC-FUNCTION B          |      |

| 25-BOOLEAN LOGIC-FORCTION B          |      |

|                                      |      |

| 26A THEN B LOGIC                     |      |

| 27-A THEN B LOGIC                    |      |

| 28-A THEN B LOGIC                    |      |

| 29-A THEN B LOGIC                    |      |

| 30—A THEN B LOGIC                    |      |

| 31-A THEN B LOGIC                    |      |

| 32-A THEN B LOGIC                    |      |

| 33-A THEN B LOGIC                    | 3-42 |

| 34-65—EDGE DETECTORS                 | 3-42 |

| 66—BUFFERED EXTERNAL CLOCK           | 3-42 |

| 67-BUFFERED EXTERNAL CLOCK           | 3-42 |

| 68-BUFFERED EXTERNAL CLOCK           | 3-42 |

| 69BUFFERED EXTERNAL CLOCK            | 3-43 |

| 70-EXTERNAL CLOCK                    |      |

| 71-EXTERNAL CLOCK                    |      |

| 72-EXTERNAL CLOCK                    |      |

| TROUBLESHOOTING CIRCUITS NOT COVERED |      |

| BY DIAGNOSTICS.                      | 3-44 |

| MAINFRAME SUPPLY CURRENT LIMITED     |      |

| 7A42 +5 Vo2 Vo5 Vo FAILURES          |      |

| 1842 TO VU, "2 VU, "O VU FAILURES    | 0-44 |

|                                    | -    |

|------------------------------------|------|

| MAINTENANCE (CONT)                 | Page |

| AMPLIFIER BOARD                    |      |

| TRIGGER BOARD                      |      |

| TRIGGER OUT TO MAINFRAME           | 3-45 |

| TRIGGER VIEW OUTPUT                | 3-45 |

| FRONT PANEL TRIGGER OUT            | 3-45 |

| ATTENUATORS                        |      |

| DIGITAL BOARD                      |      |

| ARMATURE RELAY DRIVE CIRCUITRY     |      |

| READOUT                            |      |

| CALIBRATION AND TROUBLESHOOTING    | 3-41 |

|                                    |      |

| AIDS                               |      |

| ROM PART NUMBER (LEVEL& KEY)       | 3-47 |

| FRONT-PANEL INTERACTIVE (LEVEL®    |      |

| KEY)                               |      |

| SPEAKER CONTROL (PROBE OFFSET KEY) |      |

| THRESHOLD DAC RAMP (A KEY)         | 3-48 |

| ATTENUATOR OFFSET CALIBRATOR       |      |

| (B KEY)                            | 3-48 |

| DISPLAY READOUT CHARACTERS         |      |

| (A THEN B KEY)                     | 3-48 |

| TRIGGER THRESHOLD CALIBRATION      | 0 40 |

| (NOT KEY)                          | 2 40 |

| CORRECTIVE MAINTENANCE             |      |

|                                    |      |

| OBTAINING REPLACEMENT PARTS        |      |

| SPECIAL PARTS                      |      |

| ORDERING PARTS                     |      |

| SOLDERING TECHNIQUES               | 3-49 |

| REMOVING AND REPLACING PARTS       | 3-50 |

| SEMICONDUCTORS                     | 3-50 |

| CHASSIS PARTS                      | 3-51 |

| HOW TO REMOVE THE FRONT-PANEL      |      |

| ASSEMBLY                           | 3-51 |

| HOW TO REPLACE THE FRONT PANEL     |      |

| HOW TO REPLACE FRONT-PANEL         |      |

| COMPONENTS                         | 3-52 |

| LEDS                               |      |

| POTENTIOMETERS                     |      |

|                                    |      |

| SWITCHES                           |      |

| HOW TO REMOVE AND REPLACE THE FRO  | NI-  |

| PANEL OVERLAY AND/OR THE A10 DVM   |      |

| BOARD                              |      |

| HOW TO REMOVE AND REPLACE THE REA  |      |

| PANEL                              |      |

| CIRCUIT BOARDS                     |      |

| HOW TO REMOVE THE A1 SWITCH BOARD  | _    |

| A2 LED BOARD ASSEMBLY              | 3-54 |

| HOW TO INSTALL THE A1 SWITCH BOARD | -    |

| A2 LED BOARD ASSEMBLY              | 3-54 |

| HOW TO REMOVE THE A4 ATTENUATOR    |      |

| CONTROL BOARD                      | 3-55 |

| HOW TO REPLACE THE A4 ATTENUATOR   | 5 00 |

| CONTROL BOARD                      | 3-55 |

| HOW TO REMOVE THE AS AMPLIFIER     | 0-00 |

|                                    | 3.65 |

| BOARD                              | 3-22 |

| HOW TO REPLACE THE A5 AMPLIFIER    |      |

| BOARD                              | 3-56 |

# **TABLE OF CONTENTS (CONT)**

| MAINTENANCE (CONT)                  | Page   |

|-------------------------------------|--------|

| HOW TO REMOVE AND REPLACE THE A6    |        |

| TRIGGER BOARD ASSEMBLY              | 3-56   |

| HOW TO REMOVE AND REPLACE THE A7    |        |

| DIGITAL BOARD                       | 3-57   |

| HOW TO REMOVE AND REPLACE THE A8    |        |

| MPU BOARD                           | 3-57   |

| HOW TO REMOVE THE A9 POWER SUPPLY   |        |

| BOARD                               | 3-57   |

| HOW TO REMOVE AND REPLACE           |        |

| ATTENUATOR MODULES                  | 3-58   |

| HOW TO REMOVE AND REPLACE           |        |

| ARMATURE RELAYS                     |        |

| HOW TO REPLACE THE DELAY LINES      |        |

| HOW TO REPLACE VERTICAL CHANNEL     |        |

| SWITCH MICROCIRCUITS                |        |

| PLUG-IN LATCH                       |        |

| INTERCONNECTING PINS                |        |

| COAXIAL-TYPE END-LEAD CONNECTORS    |        |

| CIRCUIT-BOARD PINS                  |        |

| CIRCUIT-BOARD PIN SOCKETS           |        |

| MULTI-PIN CONNECTORS                |        |

| ADJUSTMENT AFTER REPAIR             |        |

|                                     |        |

|                                     |        |

| SECTION 4—CHECKS AND ADJUSTMENT     |        |

| USING THESE PROCEDURES              | 4-1    |

| PERFORMANCE CHECK AND ADJUSTMENT    |        |

| SUMMARY                             |        |

| TEST EQUIPMENT                      |        |

| TEST EQUIPMENT ALTERNATIVES         |        |

| PART I-FUNCTIONAL CHECK PROCEDURE   |        |

| 7A42 FUNCTIONAL CHECK               | 4-9    |

| 1. SELF TEST                        |        |

| 2. INITIALIZING THE 7A42            | 4-9    |

| 3. DISPLAY AND TRIGGER FUNCTIONS    | 4-9    |

| 4. A THEN B NESTED TRIGGERING       | . 4-11 |

| 5. EXT CLOCK OPERATION              | . 4-11 |

| PART II-PERFORMANCE CHECK PROCEDURE | . 4-12 |

| INDEX TO PART II-PERFORMANCE CHECK  |        |

| PROCEDURE                           | . 4-12 |

| PERFORMANCE CHECK INITIAL SETUP     |        |

| PROCEDURE                           | . 4-13 |

| A CHANNEL AMPLIFIERS                | 4-14   |

B. TRIGGER VIEW TRACE .

..... 3-59 .... 3-59

.... 3-60

.... 3-60

.... 3-60 ...3-61

.... 3-61

.... 3-61

.... 3-62

...3-62

. . . . 4-1

#### INDEX TO PART III-ADJUSTMENT ADJUSTMENT INITIAL SETUP PROCEDURE ....... 4-67

Page

D. TRIGGER THRESHOLD AND PROBE

### SECTION 5-INSTRUMENT OPTIONS

CHECKS AND ADJUSTMENT (CONT)

### SECTION 6-REPLACEABLE ELECTRICAL PARTS

#### SECTION 7-DIAGRAMS AND CIRCUIT BOARD ILLUSTRATIONS

|                                          | DIAGRAM |

|------------------------------------------|---------|

| FRONT PANEL DISPLAY & CONTROL            |         |

| ATTENUATORS & CONTROL                    |         |

| CHANNEL SWITCHING & AMPLIFIERS           |         |

| DISPLAY CONTROL                          | 4       |

| TRIGGER COMPARATORS, BOOLEAN LOGIC & FIL | LTERS5  |

| EDGE DETECTORS                           |         |

| A THEN B LOGIC & TRIGGER I/O             |         |

| TRIGGER CONTROL                          |         |

| CPU                                      |         |

| READOUT                                  |         |

| POWER SUPPLIES & DISTRIBUTION            |         |

| INTERCONNECT                             |         |

| CONNECTORS TO MAINFRAME                  |         |

| CABLING                                  |         |

|                                          |         |

### SECTION 8-REPLACEABLE MECHANICAL PARTS

CHANGE INFORMATION

4-21

# **RELATED DOCUMENTATION**

| ARMATURE RELAYS                                                                           |

|-------------------------------------------------------------------------------------------|

| HOW TO REPLACE THE DELAY LINES<br>HOW TO REPLACE VERTICAL CHANNEL<br>SWITCH MICROCIRCUITS |

|                                                                                           |

| COAXIAL-TYPE END-LEAD CONNECTORS.                                                         |

| CIRCUIT-BOARD PINS                                                                        |

| CIRCUIT-BOARD PIN SOCKETS                                                                 |

| MULTI-PIN CONNECTORS                                                                      |

| ADJUSTMENT AFTER REPAIR                                                                   |

|                                                                                           |

|                                                                                           |

| SECTION 4—CHECKS AND ADJUSTMENT                                                           |

| USING THESE PROCEDURES                                                                    |

| PERFORMANCE CHECK AND ADJUSTMENT                                                          |

|                                                                                           |

# LIST OF ILLUSTRATIONS

Figure

| No.  |                                                                        | Page  |

|------|------------------------------------------------------------------------|-------|

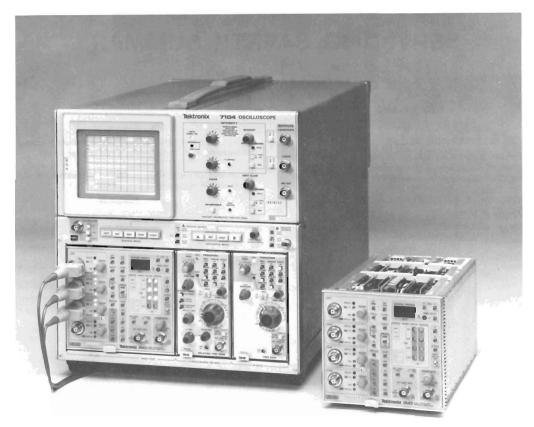

| 110. | 7A42 Features                                                          |       |

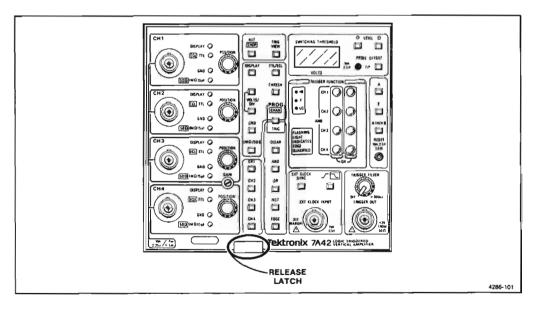

| 1-1  | 7A42 release latch                                                     |       |

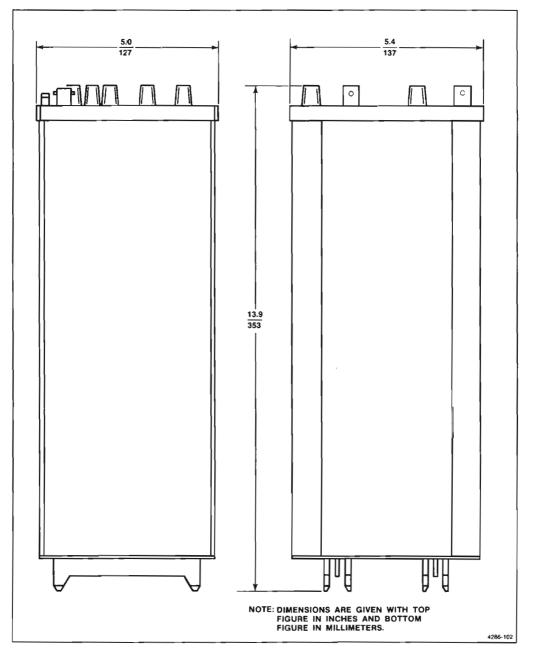

| 1-2  | 7A42 dimensional drawing                                               |       |

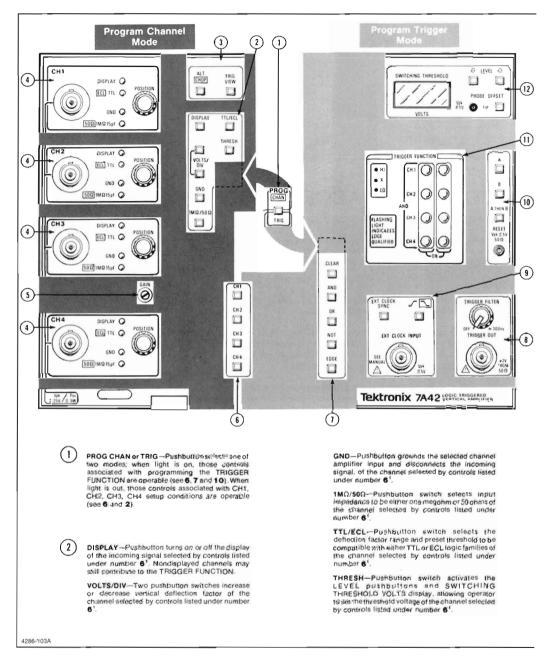

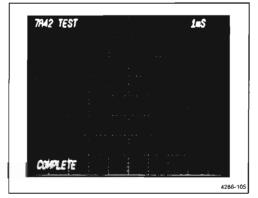

| 1-3  | 7A42 controls, connectors, and indicators                              |       |

| 1-4  | Self-test in progress                                                  |       |

| 1-5  | Self-test finished                                                     |       |

| 1-6  | Typical self-test failure display                                      |       |

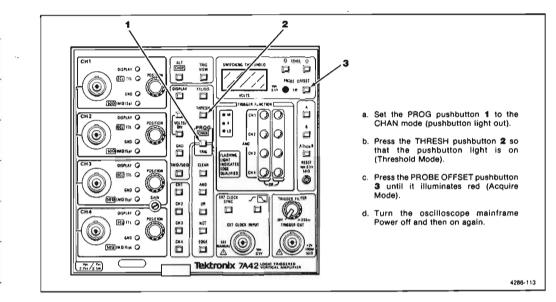

| 1-7  | Initialization of the 7A42 front-panel                                 |       |

|      | controls                                                               | 1-21  |

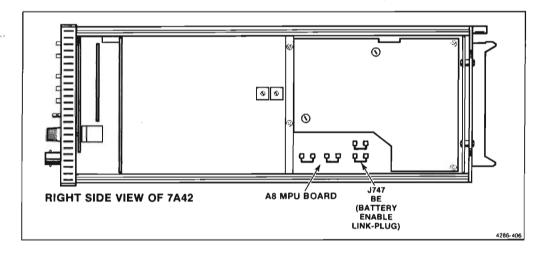

| 1-8  | Location of J747 Battery Enable link plug                              |       |

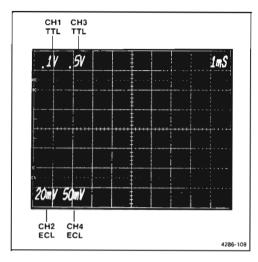

| 1-9  | Channel readout display                                                |       |

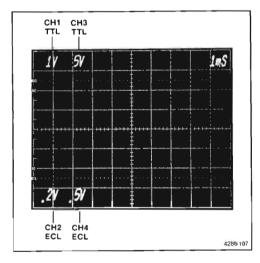

| 1-10 | Channel readout display with 10X probe attached                        |       |

|      | to inputs of CH1, CH2, CH3, and CH4                                    | 1-24  |

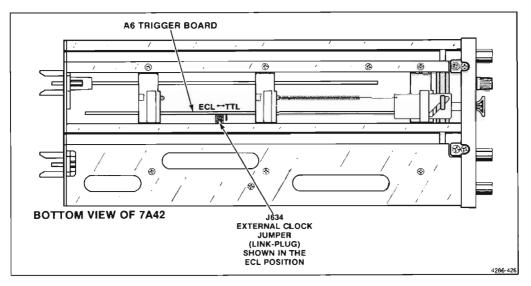

| 1-11 | Location of J634, External Clock Jumper,                               |       |

|      | on A6 Trigger Board                                                    | 1-26  |

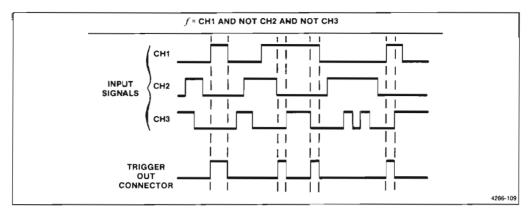

| 1-12 | Timing diagram showing the relationship of the                         |       |

|      | TRIGGER OUT waveform to the input signal                               | 1-27  |

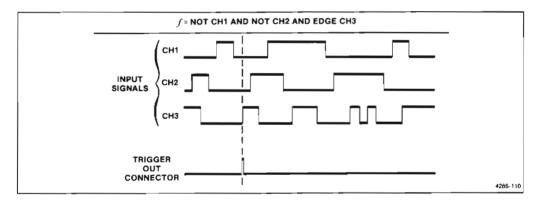

| 1-13 | Timing diagram depicting the TRIGGER FUNCTIO                           | N     |

|      | reacting to the input signals                                          | 1-27  |

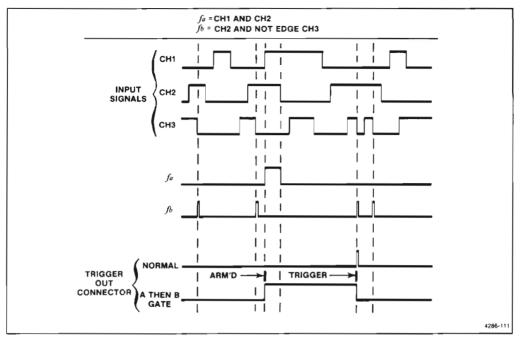

| 1-14 | Example of A THEN B, level and EDGE sensitive                          |       |

|      | TRIGGER FUNCTION, showing the Normal and                               |       |

|      | A THEN B Gate waveform alternatives                                    | 1-28  |

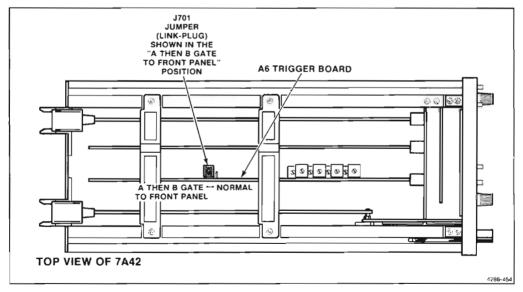

| 1-15 | Location of J701, on A6 Trigger Board                                  |       |

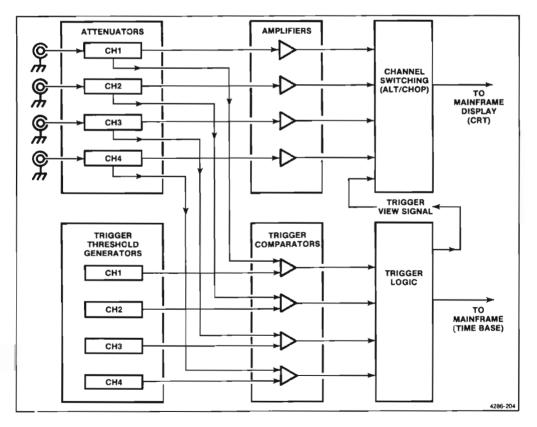

| 2-1  | Simplified Block Diagram                                               | 2-1   |

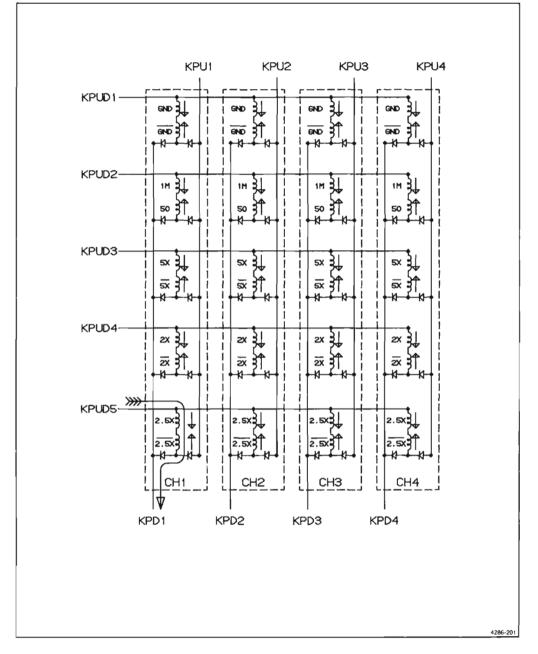

| 2-2  | Armature Relay Matrix (Actuating the                                   |       |

|      | CH1 2.5X attenuator)                                                   |       |

| 2-3  | Partial A8; Auto Restart Circuit                                       |       |

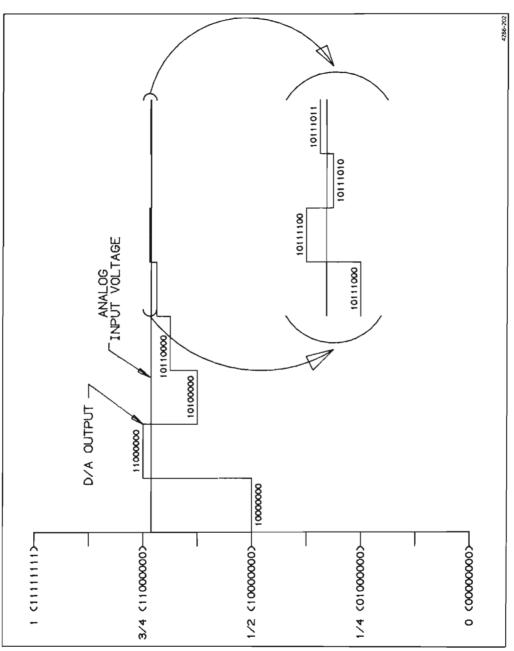

| 2-4  | Successive Approximation Example                                       |       |

| 2-5  | 7A42 Readout Timing                                                    |       |

| 3-1  | Color code for resistors and capacitors                                |       |

| 3-2  | Semiconductor lead configuration                                       | 3-7   |

| 3-3  | Orientation of multi-pin connectors                                    | 3-8   |

| 3-4  | Functions of front-panel keys with 7A42 in                             |       |

|      | extended diagnostic test mode                                          | 3-13  |

| 3-5  | Right and left views of extended A6                                    | 0.40  |

| 3-6  | Trigger Board and its connections<br>Extended view of A7 Digital Board |       |

| 3-0  | and its connections                                                    | 2.17  |

| 3-7  | Location of jumpers on A8 MPU Board                                    |       |

| 3-8  | Location of jumpers on the A7 Digital                                  |       |

| 5-0  | Board                                                                  | 3.10  |

| 3-9  | Timing of XBUSX operation                                              |       |

| 3-10 | A typical "walking-zeros" waveform                                     |       |

| 3-11 | (A) Partial A8 CPU diagram: probe-offset DAC                           |       |

|      | and (B) waveforms when operating                                       | 3-23  |

| ger  | and (B) waveforms when operating                                       | 11.01 |

|      | pins that must be unsoldered to                                        | 1-14  |

|      | an attenuator module                                                   | 1-14  |

|      | ent of delay lines                                                     |       |

|      | ssembly                                                                | 1-15  |

|      | -end lead connector assembly                                           | 2-1   |

|      | ed view of circuit-board pin and                                       | 2-2   |

|      | n of the J747 Battery Enable link                                      | _     |

|      |                                                                        | 2-3   |

|      | view waveform amplitude with ECL                                       | 2-4   |

|      | gnal                                                                   | 2-5   |

|      | view and channel transition time                                       | 3-1   |

|      | ence                                                                   | 3-2   |

|      | sine-wave signal triggered at the                                      | 3-3   |

|      | t level                                                                | 3-4   |

|      | waveform display for measuring the                                     |       |

| No.     |                                                            | Page    |

|---------|------------------------------------------------------------|---------|

| 3-14    | Waveforms in wait-state generator                          |         |

| 3-15    | (A) Probe offset A/D converter and                         |         |

|         | (B) its waveforms                                          | 3-28    |

| 3-16    | (A) Readout circuitry and (B) waveforms                    |         |

|         | at 50 µs/div., (C) 500 µs/div                              | 3-29    |

| 3-17    | How to connect a signature analyzer or the                 |         |

|         | 7A42 Signature Analyzer TTL-to-ECL Converte                |         |

|         | to the A8 MPU Board                                        |         |

| 3-18    | Timing of waveforms in A Then B Logic test                 |         |

| 3-19    | Voltages at 10 pins on attenuator module                   | 3-46    |

| 3-20    | (A) Row and column currents and (B) readout                |         |

|         | during Display Readout Characters test                     |         |

| 3-21    | Recommended desoldering sequence                           |         |

| 3-22    | How to remove the latch-release knob                       | 3-51    |

| 3-23    | Interconnections between front panel and                   |         |

|         | A6 Trigger Board                                           | 3-52    |

| 3-24    | Pins of single-color and two-color LEDs                    |         |

| 3-25    | Trigger Board ground screws                                | 3-57    |

| 3-26    | The 10 pins that must be unsoldered to                     | 127/82/ |

| 0000000 | remove an attenuator module                                |         |

| 3-27    | Placement of delay lines                                   |         |

| 3-28    | Latch assembly                                             |         |

| 3-29    | Coaxial-end lead connector assembly                        | 3-62    |

| 3-30    | Exploded view of circuit-board pin and                     |         |

|         | ferrule                                                    | 3-62    |

| 4-1     | Location of the J747 Battery Enable link                   |         |

|         | plug                                                       |         |

| 4-2     | Trigger view waveform amplitude with ECL                   |         |

|         | input signal                                               |         |

| 4-3     | Trigger view and channel transition time                   |         |

|         | coincidence                                                |         |

| 4-4     | 100 kHz sine-wave signal triggered at the                  | 4.00    |

|         | zero-volt level                                            |         |

| 4-5     | Typical waveform display for measuring the                 | 4.00    |

| 4-5     | hysteresis level<br>Location of J634 External Clock Jumper |         |

| 4-0     | (link-plug) on the A6 Trigger Board                        | 4.99    |

| 4-7     | External clock view and channel transition                 |         |

| 41      | time coincidence                                           | 4-33    |

| 4-8     | Typical external clock transition display                  |         |

| 40      | in the ECL mode                                            | 4-35    |

| 4-9     | Typical external clock transition display                  |         |

| 45      | in the TTL mode                                            | 4-36    |

| 4-10    | Threshold voltage range of the external                    |         |

|         | clock input, in the ECL mode                               | 4-38    |

|         |                                                            |         |

|         | the input signals                                          | 3-26    |

|         | FUNCTION, showing the Normal and                           | 3-27    |

|         | Gate waveform alternatives                                 | 3-27    |

|         | f J701, on A6 Trigger Board 1-28                           | 3-28    |

|         | Block Diagram                                              | 3-30    |

|         | Relay Matrix (Actuating the                                | 3-30    |

|         | attenuator)                                                | 4-1     |

|         | Auto Restart Circuit                                       |         |

|         | Approximation Example                                      | 4-2     |

|         | out Timing                                                 | 4-2     |

|         | for resistors and capacitors                               | 4-3     |

|         | ictor lead configuration                                   | 40      |

|         | of multi-pin connectors                                    | 4-4     |

|         | of front-panel keys with 7A42 in                           |         |

|         | liagnostic test mode                                       | 4-5     |

|         |                                                            |         |

# LIST OF ILLUSTRATIONS (CONT)

| Figure<br>No. | Page                                              |

|---------------|---------------------------------------------------|

| 4-13          | Typical waveform display of the 50 kHz            |

|               | reference signal and the resultant trigger output |

|               | signal                                            |

| 4-14          | Location of J701 (Link-Plug) on the A6            |

|               | Trigger Board 4-56                                |

| 4-15          | Trigger view transitions referenced to the        |

|               | CH1 waveform voltage levels                       |

| 4-16          | Relationship between the CH1, CH2, and            |

|               | Trigger View waveforms when checking the reset    |

|               | input pulse width                                 |

| 4-17          | Relationship between the CH1, CH2, and CH3        |

|               | waveforms when checking the Reset Input Pulse     |

|               | Width                                             |

| 4-18          | Location of the J747 BE (Battery Enable)          |

|               | link plug                                         |

# The illustrations in section 7 are located near their associated diagrams on the foldout page.

- 7-1 Semiconductor lead configurations.

- 7-2 7A42 board locator illustration.

- 7-3 A1-Switch circuit board assembly.

- 7-4 A2-LED circuit board assembly.

- 7-5 A4-Attenuator Control circuit board assembly.

- 7-6 A5-Amplifier circuit board assembly.

- 7-7 A7-Digital circuit board assembly.

- 7-8 A6-Trigger circuit board assembly.

- 7-9 A8-MPU circuit board assembly.

- 7-10 A9-Power Supply circuit board assembly.

- 7-11 A3-Interconnect circuit board assembly.

# LIST OF TABLES

#### Table

| No.  | Page                                            |

|------|-------------------------------------------------|

| 1-1  | Shipping Carton Test Strength                   |

| 1-2  | Electrical Characteristics                      |

| 1-3  | Environmental Characteristics                   |

| 1-4  | Physical Characteristics                        |

| 1-5  | 7A42 Self-Test Failure Messages                 |

| 1-6  | 7A42 Front-Panel Control Settings When          |

|      | Initialized1-22                                 |

| 1-7  | 7A42 Operator Message Summary1-22               |

| 1-8  | Channel Volts/Division Ranges                   |

| 2-1  | Signal Name Dictionary                          |

| 3-1  | Part Number Reference For Support Items         |

| 3-2  | Color Codes of Coaxial Cables                   |

| 3-3  | Relative Susceptibility To Damage From          |

|      | Static Discharge                                |

| 3-4  | What To Check After Replacing Components on     |

|      | The A6 Trigger Board                            |

| 3-5  | CRT And SWITCHING THRESHOLD VOLTS               |

|      | Displays                                        |

| 3-6  | Extended Test Failure Messages                  |

| 3-7  | Alphabetical List of Link-Plug Jumpers on       |

|      | Digital and MPU Boards                          |

| 3-8  | Purposes of Link-Plug Jumpers on Digital        |

|      | and MPU Boards                                  |

| 3-9  | Front-Panel Interactive Keys, Codes,            |

|      | and LEDs                                        |

| 3-10 | and LEDs                                        |

|      | Tests                                           |

| 3-11 | Failure Codes, Sets, And Resets For             |

|      | Edge Detectors                                  |

| 3-12 | Front-Panel Interactive Keys, Codes, and        |

|      | LEDs                                            |

| 4-1  | Performance Check and Adjustment Summary 4-2    |

| 4-2  | Test Equipment                                  |

| 4-3  | 7A42 Front-Panel Power-Up Control Settings 4-10 |

| 4-4  | Calibrated Range At Input Connectors            |

| 4-5  | High- and Low-Frequency Compensation            |

| 1000 | Adjustments                                     |

|      |                                                 |

# **OPERATORS SAFETY SUMMARY**

The general safety information in this part of the summary is for both operating and servicing personnel. Specific warnings and cautions will be found throughout the manual where they apply, but may not appear in this summary.

## TERMS

### IN THIS MANUAL

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

### AS MARKED ON EQUIPMENT

CAUTION indicates a personal injury hazard not immediately accessible as one reads the marking, or a hazard to property including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

## SYMBOLS

### IN THIS MANUAL

Static-Sensitive Devices

This symbol indicates where applicable cautionary or other information is to be found.

### AS MARKING ON EQUIPMENT

🖌 DANGER-High voltage

Protective ground (earth) terminal.

⚠▲

ATTENTION-refer to manual.

## WARNINGS

### **POWER SOURCE**

This product is intended to operate in a mainframe connected to a power source that will not apply more than 250 volts rms between the supply conductors or between either supply conductor and ground. A protective ground connection by way of the grounding conductor in the power cord is essential for safe operation.

### GROUNDING THE PRODUCT

This product is grounded through the grounding conductor of the mainframe power cord. To avoid electric shock, plug the mainframe power cord into a properly wired receptacle before connecting to the product input or output terminals. A protective-ground connection by way of the grounding conductor in the mainframe power cord is essential for safe operation.

### DANGER ARISING FROM LOSS OF GROUND

Upon loss of the protective-ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulating), can render an electric shock.

### DO NOT OPERATE IN EXPLOSIVE ATMOSPHERES

To avoid explosion, do not operate this product in an atmosphere of explosive gasses.

### DO NOT REMOVE COVERS OR PANELS

To avoid personal injury, do not remove the product covers or panels. Do not operate the product without the covers and panels properly installed.

### DO NOT OPERATE WITHOUT COVERS

To avoid personal injury, do not operate this product without covers or panels installed. Do not apply power to the plug-in via a plug-in extender.

# SERVICING SAFETY SUMMARY

## FOR QUALIFIED SERVICE PERSONNEL ONLY

Refer also to the preceding Operators Safety Summary

### DO NOT SERVICE ALONE

Do not perform internal service or adjustment of this product unless another person capable of rendering first aid and resuscitation is present.

# USE CARE WHEN SERVICING WITH POWER ON

Dangerous voltages exist at several points in this

product. To avoid personal injury, do not touch exposed connections and components while power is on.

Disconnect power before removing protective panels, soldering, or replacing components.

4286-1

### 7A42 FEATURES

The 7A42 Logic Triggered Vertical Amplifier is a four channel, wide bandwidth, plug-in unit, compatible with Tektronix 7000-series Oscilloscopes. It was specifically designed to display and make measurements on digital logic signals in the TTL, ECL and CMOS logic families. While the display output from the 7A42 is analog, the trigger output is digital and is comprised of a user selectable Boolean function of the *lour* input channels. A fifth TRIGGER VIEW trace depicts either the trigger function butput or the external clock input.

# **GENERAL INFORMATION**

This section contains a basic content description of both the Operators and Service manuals, information on instrument installation, power requirements, packaging for shipment, Standard Accessories, Optional Accessories, Specifications and a dimensional drawing of the 7A42. The specification portion consists of three tables: Electrical, Environmental, and Physical Characteristics.

### **TECHNICAL MANUALS**

An operators and two service manuals are supplied with your 7A42 as standard accessories. The following information outlines the content of these manuals.

#### **Operators Manual**

The Operators Manual is divided into the following four sections:

Section 1—GENERAL INFORMATION contains content descriptions of the Operators and Service manuals, instrument description, mainframe and plug-in compatibility, packaging instructions and instrument specifications.

Section 2—OPERATING INSTRUCTIONS contains a block diagram description, a front-panel drawing and brief description of controls, connectors and indicators. Get-Acquainted Exercises provide a basic operating procedure for the first-time user followed by a systematic demonstration of all front-panel controls. A detailed description of all front-panel controls is also given in this section.

Section 3—APPLICATIONS gives examples of how to use the 7A42 to make some difficult measurements.

Section 4-INSTRUMENT OPTIONS contains a description of available options.

### Service Manual

The following service instructions are for use by qualified personnel only. To avoid personal injury, do not perform any service other than that contained in the operating instructions unless you are qualified to do so. Refer to Operators Safety Summary and Service Safety Summary prior to performing any service.

The service manual is divided into 2 volumes. Volume 1 contains the following:

Section 1—GENERAL INFORMATION contains content descriptions of the Operators and Service manuals, mainframe and plug-in compatibility, packaging instructions, instrument specifications, and operating instructions.

Section 2---THEORY OF OPERATION contains basic and general circuit analysis that is useful for servicing the instrument.

Section 3—MAINTENANCE describes preventive maintenance procedures, conventional troubleshooting and diagnostic troubleshooting procedures with detailed instructions for replacing assemblies, subassemblies, and individual components.

Section 4—CHECKS AND ADJUSTMENT contains procedures to check the operational performance and electrical characteristics of the instrument. Procedures also include methods for adjustment of the instrument to meet specifications.

Section 5-INSTRUMENT OPTIONS contains a description of available options.

Section 6-REPLACEABLE ELECTRICAL PARTS contains information necessary to order replaceable parts and assemblies related to the electrical functions of the instrument.

Section 7—DIAGRAMS AND CIRCUIT BOARD ILLUSTRATIONS includes detailed circuit schematics, locations of assembled boards within the instrument, voltage and waveform information and circuit board component locators.

Section 8—REPLACEABLE MECHANICAL PARTS includes information necessary to order replaceable mechanical parts and shows exploded drawings which identify assemblies.

Volume 2 of the service manual contains signature analysis tables to be used with the diagnostic information provided in the Maintenance section of the Volume 1 service manual.

## INSTALLATION

### INITIAL INSPECTION

This instrument was inspected both mechanically and electrically before shipment. It should be free of mars or scratches and should meet or exceed all electrical specifications. To confirm this, inspect the instrument for physical damage incurred in transit and check the basic instrument functions by performing the Performance Check Procedure in the Checks and Adjustment section of this manual. If there is damage or deficiency, contact your local Tektronix Field Office or representative.

### **OPERATING TEMPERATURE**

The 7A42 can be operated where the ambient air temperature is from 0° to  $+50^{\circ}$  C and can be stored in ambient temperatures from  $-55^{\circ}$  to  $+75^{\circ}$  C. After storage at temperatures outside the operating limits, allow the chassis temperature to reach operating limits before applying power.

### INSTALLING THE 7A42 IN THE MAINFRAME

The 7A42 is designed to operate in the two center or the two left plug-in compartments of a Tektronix 7000-series oscilloscope mainframe.

#### NOTE

Switch off the mainframe power before installing or removing the 7A42.

To install the 7A42 in the mainframe, align the grooves in the top and bottom of the instrument with the guides at the top and bottom of the plug-in compartment. Then push the 7A42 in until its front panel is flush with the front panel of the mainframe.

To remove the 7A42 from its host mainframe, pull the release latch (see Fig. 1-1) to disengage the unit from the mainframe, then pull the 7A42 straight out from the plug-in compartment leaving the mainframe on the bench.

### MAINFRAME COMPATIBILITY

The 7A42 is compatible with all Tektronix 7000 series mainframes. In four-wide plug-in compartment mainframes, it can be installed in either the two left or two center plug-in compartments. When used in the two left compartments, select the Left Vertical Mode to display the analog signals. The associated time base plug-in Trigger Source should be Left Vertical with the time-base trigger controls set to Auto or Norm, Dc, Internal, Slope to +, with the Level control centered. The A Then B Gate Output can be picked off from the RIGHT VERTICAL TRIGGER SOURCE by a 7D11 or 7D15 from either horizontal compartment. In three-wide plug-in compartment mainframes, the 7A42 must be used in the two left compartments in a similar way.

When the 7A42 is installed in the center two plug-in compartments of a four compartment mainframe; set the

Figure 1-1. 7A42 release latch.

mainframe Vertical Mode and Trigger Source to Right Vertical. The mainframe A Then B Gate Output can not be used in this configuration, however, the A Then B Gate is still available at the front-panel TRIGGER OUT bnc connector.

Since all analog channels are sent out the 7A42's left interface connector, it cannot use the full capabilities of a dual beam oscilloscope such as the 7844, R7844, and the 7612D. However, it has full compatibility with these mainframes in a single beam configuration.

Since the 7A42 uses the mainframe crt readout to display the channel volts per division and error warning messages, the 7A42 is not recommended for use in mainframes without readout.

If the 7A42 is used with two time-base units in a four compartment mainframe where Chop has been selected as the Horizontal Mode, and if exactly four traces are to be displayed by the 7A42, two of the traces may synchronize to one time base while the other two traces synchronize to the other time base. To prevent this from happening, one trace should be removed, or a fifth trace should be added to the mainframe crt display (even if it is positioned off screen so it cannot be seen). With one, two, three, or five traces, the channel display will not synchronize to the horizontal chop frequency.

The 7A42 is compatible with the 7854 Oscilloscope mainframe when the 7854 is operated in real-time. However, when the 7854 is operated in digital storage, and waveform and readout acquisition is desired, the 7A42-7854 mode should be selected by moving jumper P540 to the 7854 mode. To locate P540 refer to Figure 3-7 in the Maintenance section of this manual. Once the 7A42-7854 mode has been selected, proper readout and waveform acquisition can be guaranteed with the following 7A42 display conditions:

- 1. Any single channel displayed alone (CH1, CH2, CH3, CH4, or TRIG VIEW).

- Channels 1 and 2 only displayed together, ALT display mode selected.

- Channels 3 and 4 only displayed together, ALT display mode selected.

Refer to the Applications section in the Operators manual for further information.

### PACKAGING FOR SHIPMENT

If this instrument is to be shipped by commercial transportation, we recommend that the instrument be packaged in the original manner. The carton and packaging material in which your instrument was shipped should be saved and used for this purpose.

### NOTE

# Package and ship Plug-Ins and Mainframes separately.

If this instrument is to be shipped to a Tektronix Service Center for service or repair, attach a tag to the instrument showing the following: Owner of the instrument (with address), the name of a person at your firm who can be contacted, complete instrument type and serial number, and a description of the service required.

If the original package is unfit for use or not available, package the instrument as follows:

- Obtain a corrugated cardboard shipping carton having inside dimensions at least six inches greater than the instrument dimensions; refer to Table 1-1 for carton test strength requirements.

- 2. Enclose the instrument with polyethylene sheeting or equivalent to protect the finish of the instrument.

- Cushion the instrument on all sides by tightly packaging dunnage or urethane foam between the carton and the instrument, allowing three inches of packaging on each side.

- 4. Seal the carton with shipping tape or with an industrial stapler.

- Mark the address of the Tektronix Service Center and your return address on the carton in one or more prominent locations.

| Gross Weight<br>(lb) | Carton Test Strength<br>(Ib) |

|----------------------|------------------------------|

| 0                    | 200                          |

| 10-30                | 275                          |

| 30-120               | 375                          |

| 120-140              | 500                          |

TABLE 1-1 Shipping Carton Test Strength

# SPECIFICATION

The electrical characteristics listed in Table 1-2 apply when the following conditions are met: (1) Adjustment of the instrument must have taken place at an ambient temperature between  $+20^{\circ}$  and  $+30^{\circ}$  C, (2) the instrument is allowed a 20-minute warm-up period, (3) specifications are valid at an ambient temperature of 0° to  $+50^{\circ}$  C, unless otherwise stated, (4) the instrument must be in an environment that meets the limits described in Table 1-3, (5) the instrument must be operated in a calibrated 7000-series mainframe.

Any applicable conditions not listed above may be stated as part of the characteristic. Environmental characteristics are listed in Table 1-3 and Physical characteristics are listed in Table 1-4.

| Characteristic                                 | Performance<br>Requirement                                                                                           | Supplemental<br>Information                                                                                                                                                        |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | DISPLAY                                                                                                              |                                                                                                                                                                                    |

| Deflection Factor                              |                                                                                                                      |                                                                                                                                                                                    |

| Calibrated Range at Input<br>BNC Connector     |                                                                                                                      |                                                                                                                                                                                    |

| TTL (CMOS) Family                              | 0.1, 0.2, 0.5 V/div.                                                                                                 |                                                                                                                                                                                    |

| ECL Family                                     | 20, 50, 100 mV/div.                                                                                                  |                                                                                                                                                                                    |

| Calibrated Range through a<br>10X Probe        |                                                                                                                      |                                                                                                                                                                                    |

| TTL (CMOS) Family                              |                                                                                                                      | 1, 2, 5 V/div.                                                                                                                                                                     |

| ECL Family                                     |                                                                                                                      | 0.2, 0.5, 1 V/div.                                                                                                                                                                 |

| Channel to Channel Gain Match                  | Within 2% in ECL Logic Family,<br>20 mV/div, 1 Megohm input<br>impedance.                                            |                                                                                                                                                                                    |

| Gain Ratio Accuracy<br>within the same Channel | Within 2% of indicated deflection<br>factor relative to ECL Logic<br>Family. 20 mV/div, 1 Megohm<br>input impedance. |                                                                                                                                                                                    |

| GAIN Range                                     |                                                                                                                      | Permits adjustment of deflection<br>factor for calibrated operation<br>with any calibrated 7000-series<br>mainframe. Adjustable at least<br>+4% to -4% from calibrated<br>setting. |

| Frequency Response                             | 1                                                                                                                    |                                                                                                                                                                                    |

| Bandwidth                                      | 350 MHz in 7104, 0°-35°C mainframe ambient temperature.                                                              |                                                                                                                                                                                    |

|                                                | Refer to Tektronix Product<br>Catalog 7000-Series Oscilloscope<br>System Specification for system<br>bandwidths.     |                                                                                                                                                                                    |

| Characteristic                                             | Performance<br>Requirement                          | Supplemental<br>Information                                                                                                                                                                                       |

|------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            | DISPLAY (CONT)                                      |                                                                                                                                                                                                                   |

| nput Signal Dynamic Range                                  |                                                     |                                                                                                                                                                                                                   |

| Maximum Signal Voltage at tip of 10X Probe                 |                                                     |                                                                                                                                                                                                                   |

| TTL (CMOS) Family                                          |                                                     | ±30 V.                                                                                                                                                                                                            |

| ECL Family                                                 |                                                     | ±6 V.                                                                                                                                                                                                             |

| Dutput Dynamic Range                                       |                                                     | Limited to the CRT display<br>area. Mainframe Vertical Trace<br>Separation should not be used<br>to bring an off-screen signal<br>onto screen.                                                                    |

| Maximum Input Voltage                                      |                                                     |                                                                                                                                                                                                                   |

| 1 Megohm                                                   |                                                     | 25 V (dc + peak ac)<br>36 MHz or less, derated linearly<br>to 3 V (peak ac) at 300 Mhz.                                                                                                                           |

| 50 Ohm                                                     |                                                     | 5 V RMS during any 1 ms time<br>interval. Active internal protection<br>opens all inputs if overvoltage<br>is applied to any channel.                                                                             |

| 0-Ohm Input Protection<br>Reaction Time                    |                                                     |                                                                                                                                                                                                                   |

| Maximum time to open input<br>with applied overvoltage of: |                                                     |                                                                                                                                                                                                                   |

| 10 V DC                                                    | 10 seconds.                                         |                                                                                                                                                                                                                   |

| 15 V DC                                                    | 1 second.                                           |                                                                                                                                                                                                                   |

| 20 V DC                                                    | 0.5 second.                                         |                                                                                                                                                                                                                   |

| nput Characteristics                                       |                                                     |                                                                                                                                                                                                                   |

| Input Coupling                                             |                                                     |                                                                                                                                                                                                                   |

| DC                                                         |                                                     | Incoming signal is dc-coupled to the amplifler.                                                                                                                                                                   |

| GND                                                        |                                                     | A grounded input is actually<br>open at the input BNC, (i.e.,<br>1 Megohm or 50 Ohm termination<br>is disconnected). Internally,<br>the amplifier input is grounded<br>to provide a zero-volt input<br>reference. |

| High Impedance                                             | 1 Megohm ±1%, in parallel with approximately 15 pF. |                                                                                                                                                                                                                   |

| Low Impedance                                              | 50 ohms ±1 ohm at dc.                               |                                                                                                                                                                                                                   |

| VSWR                                                       |                                                     | ≤1.15:1, dc to 300 MHz.                                                                                                                                                                                           |

#### Characteristic Performance Supplemental Requirement Information **DISPLAY (CONT)** VOLTS/DIV Shift 0.2 divisions or less shift when VOLTS/DIV is changed in either TTL or ECL Families or between Families. At least +7 divisions to -7 **POSITION Range** divisions but less than +9 divisions to -9 divisions from graticule center with gain calibrated. Displayed Noise Grounded input at maximum sensitivity, 7A42 triggered on another channel, tested at 1 ms/div and 10 ns/div, not more than 0.02 divisions RMS, as measured in a 7854. DC Drift Drift with Time Not more than 0.2 divisions in any 10 minutes after twenty minute warm-up (ambient temperature and line voltage constant). Not more than 0.2 divisions **Drift with Temperature** for 10° C ambient change (line voltage constant). Differential Delay Between Any 200 ps maximum. Two Channels, set to Same Logic Family and VOLTS/DIV Typically 25 ns from channel Plug-in Delay Time input to A11 and B11 of mainframe interface connector, Channel to Channel Crosstalk Typically less than 0.05 divisions with logic signal inputs applied through a 10X probe. Chop Frequency See mainframe manual for specifications. TRIG VIEW or External Clock View Amplitude 0.35 divs ±0.1 div. Position Baseline to be set 3 divisions (±0.5 divisions) below graticule center. Internally adjustable approximately ±4 divisions from graticule center. See Section 4 for adjustment procedure. Risetime 2 ns or less.

| Characteristic                                          | Performance<br>Requirement | Supplemental<br>Information                              |

|---------------------------------------------------------|----------------------------|----------------------------------------------------------|

|                                                         | DISPLAY (CONT)             |                                                          |

| RIG VIEW or External<br>lock View (cont)                |                            |                                                          |

| Time Coincidence with<br>Channel Display                |                            |                                                          |

| TRIG VIEW                                               | Within 3 ns.               |                                                          |

| External Clock View                                     | Within 5 ns.               |                                                          |

| eadout                                                  |                            | Displayed on crt, see detailed<br>operating information. |

|                                                         | TRIGGER                    |                                                          |

| WITCHING THRESHOLD                                      |                            |                                                          |

| Voltage Range                                           |                            |                                                          |

| At Input BNC                                            |                            |                                                          |

| TTL (CMOS) Fami y                                       | +1.28 V to -1.27 V.        |                                                          |

| ECL Family                                              | +256 mV to -254 mV.        |                                                          |

| At tip of 10X probe with<br>readout compensation        |                            |                                                          |

| TTL (CMOS) Family                                       |                            | +12.8 V to -12.7 V.                                      |