## 91A24, 91AE24, AND P6460

## OPERATOR'S MANUAL ADDENDUM

TO THE DAS 9100 SERIES OPERATOR'S MANUAL (PART NUMBER 070-03264-00, -01, AND UP)

This Tektronix Manual Addendum supports the following products:

91A24 Data Acquisition Module 91AE24 Data Acquisition Module P6460 Data Acquisition Probe

This addendum is designed to be inserted into *DAS 9100 Series Operator's Manuals* that have part numbers 070-3264-00, -01, and up. You can find your manual part number in the bottom left corner of the manual title page. (Note: Some manuals may already have this addendum inserted in the back of their binders. Check your manual to see if there is a duplicate.)

This addendum contains operator's information specific to the 91A24 and 91AE24 Data Acquisition Modules and the P6460 Data Acquisition Probe. It adds information to the DAS 9100 Series Operator's Manual; it does not replace information.

Refer to the DAS 9100 Series Operator's Manual for information on other products, including mainframes, instrument modules, probes, and options.

**How To Use This Addendum.** This addendum is organized similarly to the *DAS* 9100 Series Operator's Manual. Information within the addendum corresponds to sections within the operator's manual. You can place the addendum at the back of the operator's manual binder, or you can insert the pages into their corresponding operator's manual sections.

This addendum affects only some of the operator's manual sections; it does not affect all of them.

PLEASE CHECK FOR CHANGE INFORMATION AT THE REAR OF THIS MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

| Serial | Number |  |

|--------|--------|--|

|--------|--------|--|

070-4540-00 Product Group 57

## TABLE OF CONTENTS

|                                                         | Page     |

|---------------------------------------------------------|----------|

| LIST OF ILLUSTRATIONS                                   | ٧        |

| OPERATOR'S SAFETY SUMMARY                               | v        |

| GENERAL INFORMATION                                     |          |

|                                                         |          |

| Description                                             |          |

| Standard and Optional Accessories                       |          |

| Specifications                                          | 3        |

| OPERATING INSTRUCTIONS                                  | 7        |

| Module Installation                                     | 7        |

| Configuration and Update Requirements                   | 7        |

| Word Recognizer and Clock Interconnect Pins             | 8        |

| Sync-Output Cable                                       | 9        |

| Connecting Acquisition Probes                           | 10       |

| P6460 Characteristics                                   | 10       |

| Operator's Checkout                                     | 12       |

|                                                         |          |

| CHANNEL SPECIFICATION MENU                              | 13       |

| Power-Up Channel Grouping                               | 13       |

| Grouping Demultiplexed Channels                         | 13       |

| Threshold Selection                                     | 13       |

|                                                         |          |

| TRIGGER SPECIFICATION MENU                              | 15       |

| 91A24 TRIGGER SPECIFICATION Sub-Menu                    | 15       |

| MODE, SPECIFICATION, and Data Entry Fields              | 15       |

| Mnemonics Functions                                     | 16       |

| Data Qualification Functions                            | 17       |

| Trigger Functions                                       | 18       |

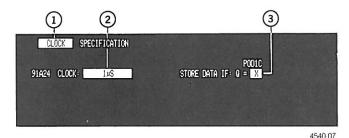

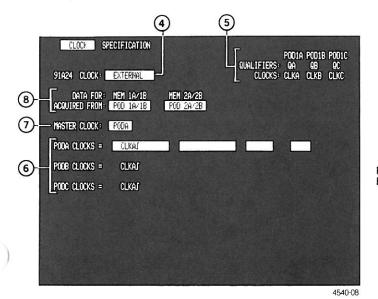

| 91A24 CLOCK SPECIFICATION Sub-Menu                      | 22       |

| Internal Clocking                                       | 22       |

| External Clocking                                       | 23       |

|                                                         |          |

| 91A24 ARMS Mode                                         |          |

| Sub-Menu Organization                                   | 27       |

| Conditions for Time-Alignment                           |          |

| ARMS Acquisition Display                                | 27       |

| STATE TABLE MENU (Additions with Firmware Version 1.11) | 29       |

| Page Scrolling                                          |          |

| Counter/Timer Display                                   | 29       |

| Acquisition Memory Display                              | 29<br>29 |

| ARMS Acquisition Display                                | 29<br>29 |

| Reference Memory Display                                | 29       |

| ,                                                       | 23       |

| TIMING DIAGRAM MENU                                     | 31       |

| Acquisition Display                                     | 31       |

| ARMS Acquisition Display                                | 31       |

## TABLE OF CONTENTS (cont.)

|                                                                    | Page |

|--------------------------------------------------------------------|------|

| DEFINE MNEMONICS MENU (Additions With Firmware Version 1.11)       | . 33 |

| Word Recognizer Mnemonics                                          | . 33 |

| Group Headings for the 91A24 Trigger Specification Sub-menu        |      |

| Displaying Micro Names                                             |      |

| New System Call                                                    | . 35 |

| APPLICATION EXAMPLES                                               | . 37 |

| System Setup                                                       |      |

| Connections to the 8085                                            |      |

| Clocking                                                           |      |

| Setting Up Demultiplexing                                          |      |

| Setting Up Clock Expressions                                       | . 38 |

| Defining the Master Clock                                          |      |

| Setting Up a DMA Qualifier                                         |      |

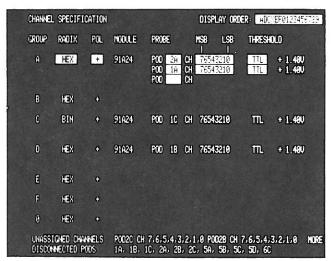

| Channel Grouping                                                   |      |

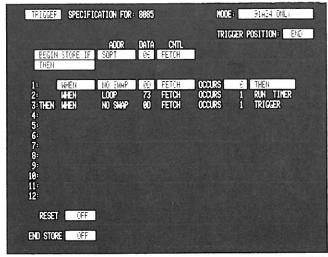

| Triggering and Data Qualification                                  |      |

| Timing Worst-Case Execution                                        |      |

| Counting Occurrences of a Repetitive Event                         | . 42 |

| ERROR AND PROMPTER MESSAGES (Additions With Firmware Version 1.11) | . 45 |

| Index                                                              | . 47 |

## LIST OF ILLUSTRATIONS

| Figure<br>Number | 1                                                                                                                                       | Page |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

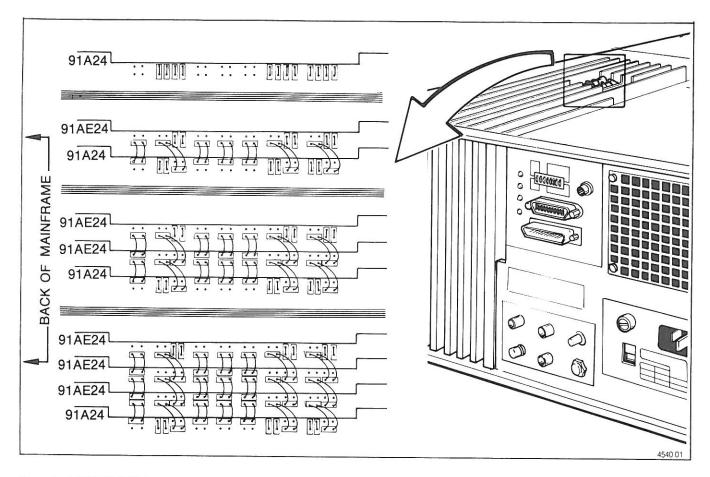

| 1                | 91A24/91AE24 interconnect pins                                                                                                          | 9    |

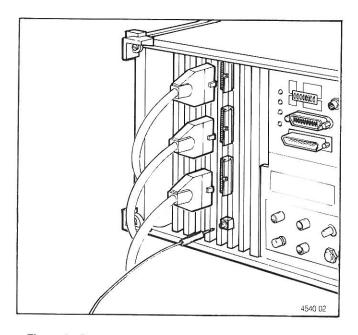

| 2                | Connecting P6460 probes and sync-output cable                                                                                           | 9    |

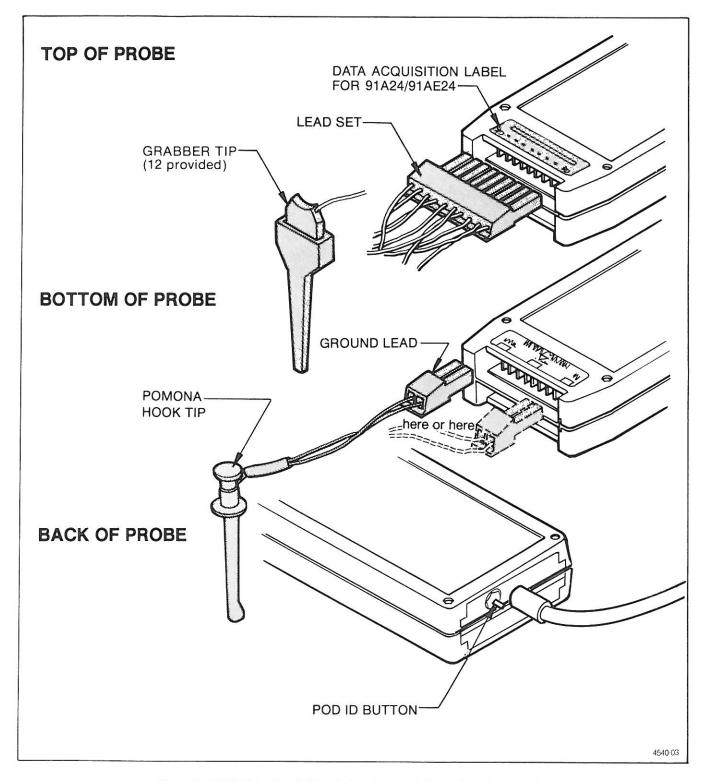

| 3                | P6460 Data Acquisition Probe characteristics and lead connections                                                                       |      |

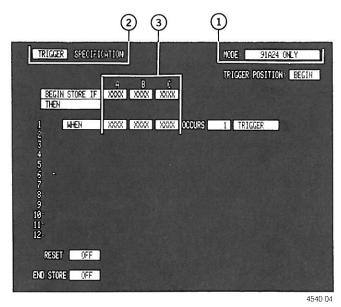

| 4                | Default 91A24 Trigger Specification sub-menu                                                                                            | 16   |

| 5                | 91A24 Trigger Specification sub-menu and its data qualification functions                                                               |      |

| 6                | 91A24 Trigger Specification sub-menu and its trigger functions                                                                          |      |

| 7                | Default Clock Specification sub-menu                                                                                                    |      |

| 8                | Clock Specification sub-menu configured for external clocking                                                                           |      |

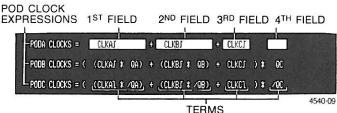

| 9                | Pod clock expressions and their fields                                                                                                  |      |

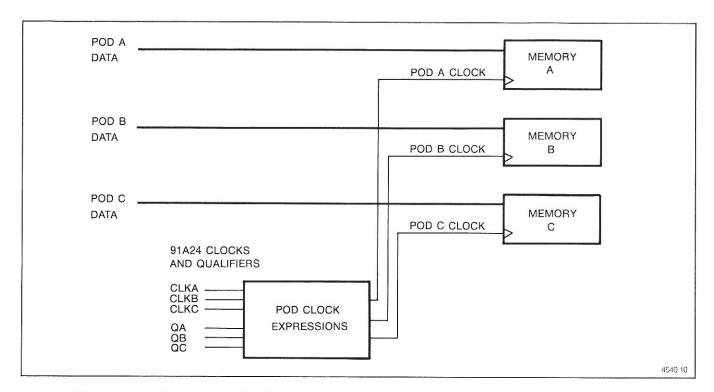

| 10               | External clocking and acquisition                                                                                                       | 24   |

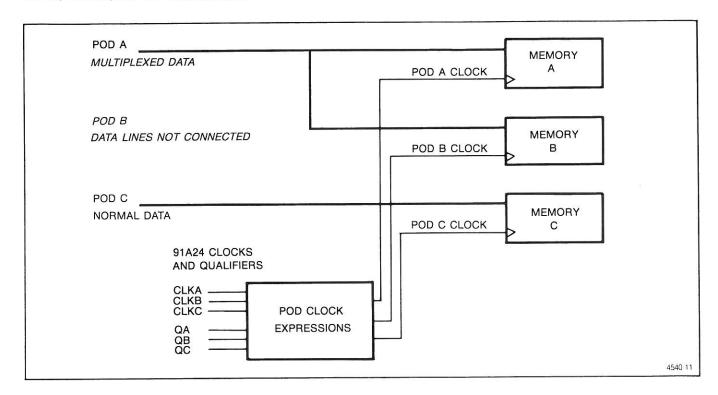

| 11               | Demultiplexed acquisition                                                                                                               |      |

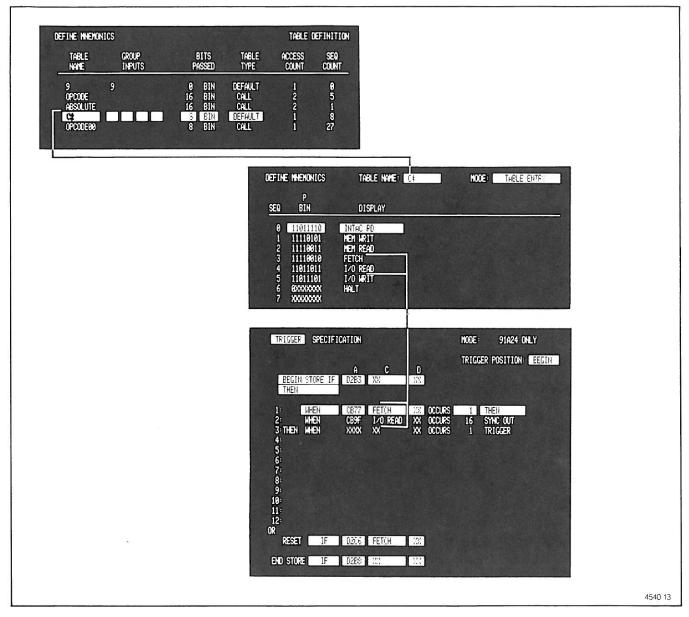

| 12<br>13         | Using mnemonics for word recognition in the 91A24 Trigger Specification sub-menu How creating a [group]* table provides word recognizer | 33   |

|                  | mnemonics for the 91A24 Trigger Specification sub-menu                                                                                  | 34   |

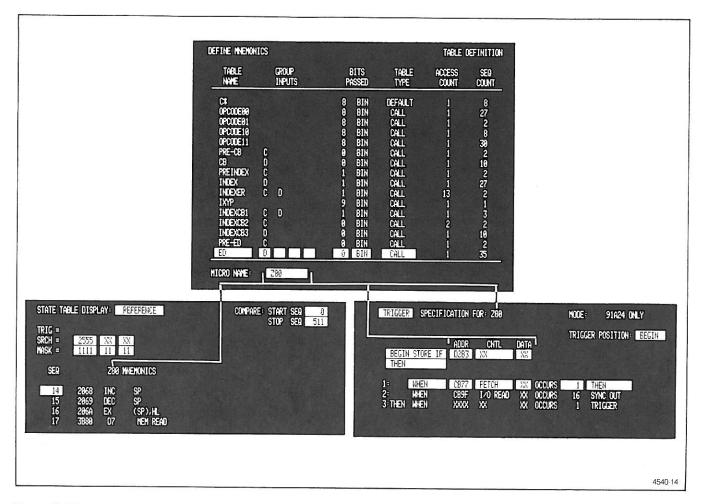

| 14               | Changes in the State Table menu and 91A24 Trigger Specification sub-menu                                                                | -    |

|                  | caused by the MICRO NAME field                                                                                                          | 35   |

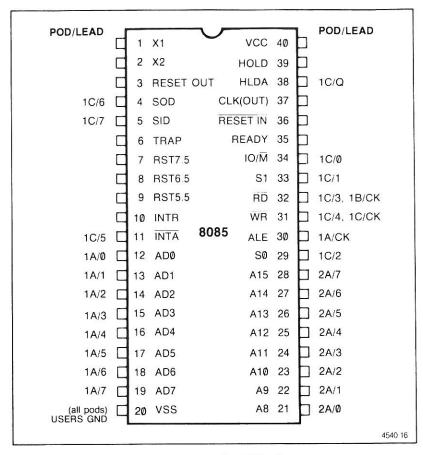

| 15               | Connections to the 8085 microprocessor                                                                                                  |      |

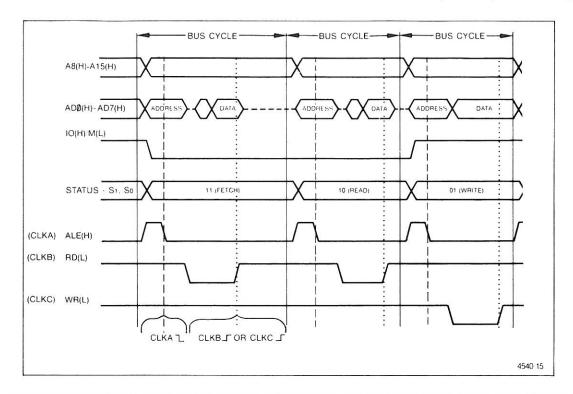

| 16               | 8085 bus timing and 91A24 clocking                                                                                                      |      |

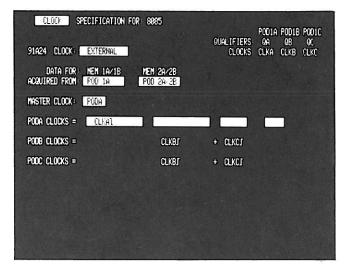

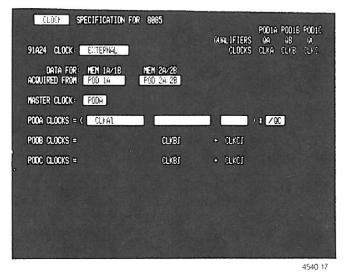

| 17               | Clock Specifiation sub-menu setup for 8085                                                                                              |      |

| 18               | Using /QC to eliminate acquisition of DMA cycles                                                                                        |      |

| 19               | 8085 Channel Specification setup                                                                                                        |      |

| 20               | A proposed sorting algorithm                                                                                                            | 41   |

| 21               | 91A24 Trigger Specification setup for timing worst-case execution                                                                       | 42   |

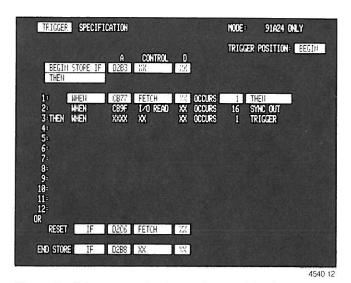

| 22               | An interrupt service routine which outputs characters to an I/O port                                                                    |      |

| 23               | 91A24 Trigger Specification sub-menu set up to count output of characters to an I/O port                                                |      |

## **OPERATOR'S SAFETY SUMMARY**

The general safety information in this part of the summary is for both operators and service personnel. Specific warnings and cautions will be found throughout the manual where they apply, but may not appear in this summary.

#### Terms In This Manual

CAUTION statements identify conditions or practices that could result in damage to the equipment or other property.

WARNING statements identify conditions or practices that could result in personal injury or loss of life.

#### Terms As Marked on Equipment

CAUTION indicates a personal injury hazard not immediately accessible as one reads the marking, or a hazard to property including the equipment itself.

DANGER indicates a personal injury hazard immediately accessible as one reads the marking.

### Symbols As Marked on Equipment

DANGER - High voltage.

Protective ground (earth) terminal.

ATTENTION — refer to manual.

#### **Grounding the Product**

This product is grounded through the mainframe in which it is operating. To avoid electrical shock, plug the power cord of the mainframe into a properly wired receptacle before connecting to the product. A protective-ground connection by way of the grounding conductor in the power cord is essential for safe operation.

#### **Danger Arising From Loss of Ground**

Upon loss of the protective-ground connection, all accessible conductive parts (including knobs and controls that may appear to be insulated) can render an electric shock.

#### Do Not Operate in Explosive Atmospheres

To avoid explosion, do not operate this product in an explosive atmosphere unless it has been specifically certified for such operation.

## **GENERAL INFORMATION**

### DESCRIPTION

The 91A24 and 91AE24 Data Acquisition Modules are plugin circuit board assemblies that are compatible with any DAS 9100 Series mainframe. They feature comprehensive clocking, data qualification, and triggering abilities. Acquisition rates of up to 10 MHz are possible, using either internal or external clocking. Each module acquires 24 data channels, using three data acquisition probes.

**Clocking.** The 91A24 can acquire data under the control of either asynchronous internal clocking or synchronous external clocking. For external clocking, three different clock expressions may be formed, each using as many as three clock and three qualifier signals. Data can be demultiplexed without double probing.

**Data Qualification and Triggering.** The 91A24 offers extensive word recognition for data qualification and triggering.

For qualifying blocks of data, you can use as many as two ORed word recognizers to begin data storage, and two more to end data storage. Alternatively, you can qualify data on a cycle-by-cycle basis using up to two ORed word recognizers.

For triggering, there is a 16-level sequential word recognizer, a word recognizer for resetting the sequential word recogniz-

er, and a word recognizer which can trigger independently of the sequential word recognizer.

**Module Configuration.** Only one 91A24 module may be installed in a DAS mainframe. In addition, up to three 91AE24 modules can be installed, allowing acquisition of up to 96 channels. 91AE24s are expander modules and can only be used with a 91A24 module installed in the mainframe.

**Modes of Operation.** The 91A24 and 91AE24 modules may be operated alone in 91A24 ONLY mode, or they may be used with high-speed data acquisition modules in 91A24 ARMS mode.

In ARMS mode, the 91A24/91AE24 and high-speed modules act as linked logic analyzers. Both types of modules acquire data simultaneously; when the 91A24 trigger conditions are satisfied, the high-speed module is armed to look for its trigger event.

**Data Display.** Data acquired by 91A24/91AE24 modules, including ARMS acquisition, can be displayed in both state table and timing diagram format.

## STANDARD AND OPTIONAL ACCESSORIES

#### 91A24 DATA ACQUISITION MODULE

The following lists include the standard and optional accessories for the 91A24 Data Acquisition Module.

#### Standard Accessories

| 1 | 175-8165-00 | External Sync Output Cable,         |

|---|-------------|-------------------------------------|

|   |             | 2 m (78 in.)                        |

| 1 | 070-4672-00 | 91A24 Instructions                  |

| 1 | 070-4540-00 | 91A24, 91AE24, and P6460 Operator's |

|   |             | Manual Addendum (to the DAS 9100    |

|   |             | Series Operator's Manual)           |

|   |             |                                     |

|   |             |                                     |

#### **Optional Accessories**

| UPIK40      | 40-pin Universal Probe Interface Kit    |

|-------------|-----------------------------------------|

| 070-4541-00 | 91A24 and 91AE24 Service Manual         |

|             | Addendum (to the DAS 9100 Series        |

|             | Service Manual)                         |

| 175-8166-00 | Interconnect Cable Assembly,            |

|             | 28 cm (11 in.), for service procedures; |

|             | 7 required                              |

| DAS 9100 Se | eries Mnemonics Tapes;                  |

|             | see your Tektronix Sales Engineer for   |

|             | ordering information                    |

#### 91AE24 DATA ACQUISITION MODULE

The following lists include the standard and optional accessories for the 91AE24 (Expander) Module.

#### Standard Accessories

| 7 | 175-8167-00 | Interconnect Cable Assemblies, |

|---|-------------|--------------------------------|

|   |             | 7.6 cm (3 in.)                 |

| 1 | 070-4671-00 | 91AE24 Instructions            |

### **Optional Accessories**

| UPIK40      | 40-pin Universal Probe Interface Kit    |

|-------------|-----------------------------------------|

| 070-4541-00 | 91A24 and 91AE24 Service Manual         |

|             | Addendum (to the DAS 9100 Series        |

|             | Service Manual)                         |

| 175-8166-00 | Interconnect Cable Assembly,            |

|             | 28 cm (11 in.), for service procedures; |

|             | 7 required                              |

| DAS 9100 Se | eries Mnemonics Tapes;                  |

|             | see your Tektronix Sales Engineer for   |

|             |                                         |

ordering information

#### P6460 DATA ACQUISITION PROBE

The following lists include the standard and optional accessories for the P6460 Data Acquisition Probe.

#### Standard Accessories

| 1 | 070-4345-00 | P6460 Instructions (includes service information)                                     |

|---|-------------|---------------------------------------------------------------------------------------|

| 1 | 012-0747-00 | Lead Set, 25 cm (10 in.)                                                              |

| 1 | 020-0720-00 | Package of 12 Probe Tips (each tip is a 206-0222-00)                                  |

| 2 | 012-0989-00 | Ground (or VL) Sense Leads,<br>12.7 cm (5 in.) with Pomona Hook Tips<br>(344-0267-00) |

| 2 | 344-0046-00 | Alligator Clips (substitute for hook tips above)                                      |

#### **Optional Accessories**

| 012-0987-00<br>012-0800-00<br>020-1041-00<br>012-1000-00<br>012-0989-01 | Flying Lead Set, 12.7 cm (5 in.) Flying Lead Set, 25 cm (9.8 in.) 40-pin Univ. Probe Interface Kit Diagnostic Lead Set, 25 cm (10 in.) Package of 10 Ground (or VL) Sense Lead Tips with Pomona Hook Tips (344-0267-00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 103-0209-01                                                             | GPIB Connector/Adapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 003-0709-00                                                             | Control of the state of the sta |

| 015-0330-00                                                             | Adapter, Test Clip, 16-DIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 015-0339-02                                                             | Adapter, Test Clip, 40-DIP,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 015-0339-00                                                             | 10 cm (3.9 in.) cable (requires 380-<br>0560-05 Adapter)<br>Adapter, Test Clip, 40-DIP,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                         | 30 cm (11.8 in.) cable (requires 380-0560-05 Adapter)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 380-0560-05                                                             | Adapter, required for use with 40-DIP Adapters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 119-1474-00                                                             | Probe Holder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

## **SPECIFICATIONS**

Table 1

91A24 AND 91AE24 ELECTRICAL SPECIFICATIONS: DATA ACQUISITION AND STORAGE

| Characteristics                                    | Performance Requirements          | Supplemental Information                                                                                             |

|----------------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Maximum Sampling Rate                              | 10 MHz (non-multiplexed)          | Internal or External Clocking (multiplexed 20 MHz)                                                                   |

| Acquisition Memory<br>Memory Depth                 |                                   | 1023 Words                                                                                                           |

| Memory Width                                       |                                   | 24 Channels (one 91A24, 3 probes); expandable to 96 channels (one 91A24, three 91AE24s, 12 probes).                  |

| Data Setup (period data valid prior to clock edge) | 25 ns min.<br>(using P6460 probe) | Same requirement for multiplexed data.                                                                               |

| Data Hold (period data valid beyond clock edge)    | 0 ns max.<br>(using P6460 probe)  | Same requirement for multiplexed data.                                                                               |

| Trigger Position                                   |                                   | Selectable for BEGIN, CENTER, END, DELAY. In DELAY mode, trigger sequence = 1015 - DELAY value.                      |

| External Trigger Enable                            |                                   | TTL LS input to mainframe BNC connector. Rising edge enables sequential word recognizer trigger on next clock cycle. |

| Setup Time<br>Hold Time                            | 25 ns min.<br>0 ns max.           |                                                                                                                      |

| 91A24 ARMS Modes                                   |                                   | High-speed module is armed to look for trigger within ten 91A24 clock cycles after 91A24 trigger event.              |

| Requirement for Time Alignment                     |                                   | No data qualifiers are used (91A24 clock qualifiers are permitted).                                                  |

|                                                    |                                   | High-speed module operation must overlap 91A24 operation by at least 5 master clocks.                                |

|                                                    |                                   | High-speed clock rate must be at least twice that of 91A24 master clocks.                                            |

|                                                    |                                   | Trigger words for both the high-speed and 91A24 modules must be in memory.                                           |

Table 2

91A24 AND 91AE24 ELECTRICAL SPECIFICATIONS: CLOCKING

| Characteristic               | Performance Requirements                     | Supplemental Information                                                                                                                      |

|------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Clock               |                                              | Interval is selectable from 100 ns to 5 ms in a 1-2-5 sequence. May be qualified using 91A24's pod C qualifier.                               |

| External Clocks & Qualifiers |                                              | 3 clocks, 3 qualifiers                                                                                                                        |

| Source                       |                                              | Via acquisition probes connected to 91A24                                                                                                     |

| Selection                    |                                              | Boolean combinations used to form 3 POD CLOCK expressions.                                                                                    |

| Raw Clock Rate               | 20 MHz max.                                  | Time between <i>qualified</i> master clocks may be no less than 100 ns. Other POD CLOCKs must occur ≥ 20 ns before next cycle's master clock. |

| Clock Pulse Width            | 25 ns min., high and low (using P6460 probe) |                                                                                                                                               |

| Qualifier Setup Time         | 25 ns min.<br>(using P6460 probe)            |                                                                                                                                               |

| Qualifier Hold Time          | 0 ns max.<br>(using P6460 probe)             |                                                                                                                                               |

Table 3

91A24 AND 91AE24 ELECTRICAL SPECIFICATIONS: WORD RECOGNIZER FUNCTIONS

| Characteristic             | Performance Requirements | Supplemental Information                                                                           |

|----------------------------|--------------------------|----------------------------------------------------------------------------------------------------|

| Word Recognizer Width      |                          | Same as channel width                                                                              |

| BEGIN STORE IF             |                          | Up to 2 ORed word recognizers                                                                      |

| END STORE IF               |                          | Up to 2 ORed word recognizers                                                                      |

| STORE ONLY IF              |                          | Up to 2 ORed word recognizers                                                                      |

| RESET Word Recognizer      |                          | Resets sequential word recognizer to Level 1, and resets timer.                                    |

| Independent Trigger        |                          | Parallel word recognizer ORed to sequential word recognizer. Not affected by trigger input signal. |

| Sequential Word Recognizer |                          | Up to 16 levels of word recognition                                                                |

| OCCURS Counter             |                          | Number of event occurrences (1-4096) may be specified at each level.                               |

| Intermediate Level Actions |                          | THEN, RUN TIMER, STOP TIMER, SYNC OUT selections                                                   |

| Final Level Actions        |                          | TRIGGER, INCR CNTR (12 decimal digits), SYNC & TRG, NEVER TRG selections                           |

Table 3 (cont.)

91A24 AND 91AE24 ELECTRICAL SPECIFICATIONS: WORD RECOGNIZER FUNCTIONS

| Characteristic         | Performance Requirements                                                                      | Supplemental Information                                                                                                     |  |  |

|------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Timer Accuracy         | Indicated value $\pm$ 2%, $\pm$ 100 ns each time started                                      | Times to over 27 hours.                                                                                                      |  |  |

| Sync Output Signal     | TTL output level, terminated into 1 $\text{M}\Omega$                                          | Remains high until completion of a subsequent word recognizer level with no syncoutput specified.                            |  |  |

| Sync Output Delay      | 3 master clocks + 45 ns ± 10 ns<br>between event occurrence and rising<br>edge of sync-output | Measured from master clock's active edge to connector output.                                                                |  |  |

| Word Recognizer Output |                                                                                               | TTL-level signal output by mainframe BNC connector. 4 Master clock cycles after trigger event, signal goes and remains high. |  |  |

Table 4

91A24 AND 91AE24 ELECTRICAL SPECIFICATIONS: PROBE INTERFACE AND SUPPORT

| Characteristic                                              | Performance Requirements        | Supplemental Information                                   |

|-------------------------------------------------------------|---------------------------------|------------------------------------------------------------|

| Probe-to-Module Signals                                     |                                 | 8 data (91A24 & 91AE24), 1 clock, 1 qualifier (91A24 only) |

| Module-to-Probe Signals                                     |                                 |                                                            |

| Threshold Reference Voltage                                 |                                 |                                                            |

| Fixed (TTL)                                                 |                                 | +1.40 V                                                    |

| Variable (VAR)                                              |                                 | -6.40 V to $+6.35$ V in 50 mV steps. Default is $-1.30$ V. |

| TTL and VAR Threshold Accuracy (to input of attached probe) | Indicated value ± 0.5%, ± 65 mV |                                                            |

## 91A24 AND 91AE24 ENVIRONMENTAL SPECIFICATIONS

The environmental specifications for the operation of this instrument meet or exceed those specified for the operation

of the DAS9109 Mainframe and the DAS9129 Mainframe. For details, refer to the DAS 9100 Series Operator's Manual.

Table 5

P6460 ELECTRICAL SPECIFICATIONS

| Characteristic                                                                                           | Description                                                                  |  |  |  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| User's Ground Sense                                                                                      | $<\!$ 100 $\Omega$ to user's ground                                          |  |  |  |

| Input Impedance                                                                                          | 1 M $\Omega$ $\pm$ 1%, 5 pF nominal; lead set adds approx 5 pF               |  |  |  |

| Max. Non-Destructive Input Voltage Range                                                                 | ±40 V (DC + peak AC)                                                         |  |  |  |

| Max. Voltage Between Any Two Inputs                                                                      | ±60 V (DC + peak AC)                                                         |  |  |  |

| Operating Input Voltage Range                                                                            | From $-40$ V to input threshold's voltage $+$ 10 V $(+30$ V for RS-232 only) |  |  |  |

| Threshold Offset and Accuracy                                                                            | $\pm0.25\%$ of threshold $\pm50$ mV                                          |  |  |  |

| Minimum Input Swing                                                                                      | 0.5 V p-p centered on the threshold                                          |  |  |  |

| Minimum Pulse Width (with input 250 mV over the threshold from $+0.5~\mathrm{V}$ and $-0.5~\mathrm{V}$ ) | 4 ns at threshold                                                            |  |  |  |

Table 6

P6460 ENVIRONMENTAL SPECIFICATIONS

| Characteristic                         | Description                                          |  |  |

|----------------------------------------|------------------------------------------------------|--|--|

| Temperature<br>Operating<br>Storage    | -15°C to +55°C<br>-62°C to +75°C                     |  |  |

| Humidity                               | 95% to 97% relative humidity                         |  |  |

| Altitude<br>Operating<br>Non-operating | 4.5 km (15,000 ft.)<br>15 km (50,000 ft.)            |  |  |

| Electrical Discharge                   | 5 kV maximum from 200 pF with 2 kΩ series resistance |  |  |

Table 7

P6460 PHYSICAL SPECIFICATIONS

| Characteristic     | Description                                                                 |  |  |  |

|--------------------|-----------------------------------------------------------------------------|--|--|--|

| Weight             | 340 g (12 oz.)                                                              |  |  |  |

| Overall Dimensions | r.                                                                          |  |  |  |

| Pod                | 11.4 cm (4.5 in.) long,<br>5.6 cm (2.2 in.) wide,<br>2.2 cm (0.85 in.) deep |  |  |  |

| Cable              | 2 m (78.8 in.) ±10%                                                         |  |  |  |

## OPERATING INSTRUCTIONS

This section describes installation requirements for the 91A24 and 91AE24 modules and their probes. It also provides operator's checkout procedures for the modules and probes.

Repackaging Information. All DAS 9100 Series products are shipped in specially designed transportation packaging. Keep this packaging for use whenever you ship DAS products. If the original packaging is no longer fit for use, contact your nearest Tektronix Field Office and obtain new DAS packaging.

If you need to ship any part of your 91A24/91AE24 system to a Tektronix Service Center, please send all parts of your 91A24 system: the 91A24 module, any 91AE24 modules, and their probes.

When you ship a product to a Tektronix Service Center, be sure to attach an identifying tag to the product (inside the packaging). On this tag include your name, the name of your company, the name and serial number of the enclosed product, and a description of the service requested.

### MODULE INSTALLATION

It is assumed that you are already familiar with the procedures for removing the mainframe top panel and cover, and with the procedures for installing modules into the mainframe bus slots. If you are not familiar with these procedures, refer to the *Operating Instructions* section of the *DAS 9100 Series Operator's Manual*.

Do not remove or install a 91A24 or 91AE24 module until you have read the following warnings, cautions, and configuration requirements.

#### WARNING

When installing or removing instrument modules, the operator may gain access to the mainframe's module compartment only. Unless you are a qualified service technician, do not open any other compartments within the mainframe because they contain hazardous voltages.

## CAUTION

When modules are being installed, the mainframe should be turned off and unplugged from its power source. Damage to the module's circuitry may occur if the module is installed while the mainframe is receiving power.

## CONFIGURATION AND UPDATE REQUIREMENTS

#### **Configuration Requirements**

The power and configuration requirements for the 91A24 and 91AE24 modules are as follows:

- To operate 91AE24 modules, a 91A24 module must be installed in the mainframe.

- 2. The 91A24 module can only share a +5 V power supply with a 91AE24, 91A08, or 91P32 module.

If the 91A24 is installed in a bus slot sharing a power supply with any type of module other than a 91AE24, 91A08, or 91P32, the power supply may not function correctly due to current overload.

When positioning modules around the 91A24, be sure to allow for the power supply restriction. Table 1 shows bus slot positions recommended for 91A24 and 91AE24 modules.

You can see which power supplies are present in the mainframe by checking the chrome pins visible through the power supply area cover. DO NOT remove the power supply area cover.

Without violating the power supply requirement, the 91A24 and 91AE24 must be positioned in adjacent bus slots. All 91AE24 modules must be positioned to the same side (either all to the right or all to the left) of the 91A24 module. Table 1 shows bus slot positions recommended for 91A24 and 91AE24 modules.

Table 1

RECOMMENDED BUS-SLOT PLACEMENT

| Bus Slot | Module                                  |  |  |  |  |

|----------|-----------------------------------------|--|--|--|--|

| 0        | Controller                              |  |  |  |  |

| 1        | 91A24 Data Acquisition Module           |  |  |  |  |

| 2        | 91AE24 Data Acquisition Module          |  |  |  |  |

| 3        | 91AE24 Data Acquisition Module          |  |  |  |  |

| 4        | 91AE24 Data Acquisition Module          |  |  |  |  |

| 5        | Any module other than a 91A24 or 91AE24 |  |  |  |  |

| 6        | Any module other than a 91A24 or 91AE24 |  |  |  |  |

| 7        | Trigger/Timebase                        |  |  |  |  |

| 7        | Trigger/Timebase                        |  |  |  |  |

#### 91A24, 91AE24, and P6460 Addendum

Positioning modules as recommended ensures that Tektronix mnemonics tape files will restore. Also, if you use more than one DAS, consistent positioning of modules ensures that your setup files are transferable.

#### Firmware Update Requirements

To operate with 91A24/91AE24 modules your DAS must be equipped with firmware version 1.11 or higher. If your DAS has a lower firmware version, it will display the error message NEEDS FIRMWARE VERSION >=1.11 at powerup. You can determine your mainframe's firmware version by looking in the upper right corner of the power-up display.

Firmware version 1.11 requires that 91A04 modules be equipped with version 2 (or higher) firmware. You can determine if your 91A04 has the correct firmware by checking the 91A04 listing on the DAS powerup display: V2 (or higher) should appear at the right of this line.

To obtain Version 1.11 update kits for your mainframe and/or 91A04, contact your Tektronix representative.

#### **Hardware Update Requirements**

For use with 91A24/91AE24 modules, certain hardware updates are required. These updates can be performed by your Tektronix Service Center, or you can order the appropriate DAS hardware update kit. The following updates are necessary:

- DAS mainframes with serial numbers lower than B030100 require a controller board modification.

- 91A08 modules with serial numbers lower than B020100 require modification to operate in 91A24 ARMS 91A08 mode.

- PMA 100 Personality Module Adapters with serial numbers lower than B020100 require a new backpanel label.

Should any of your equipment require an update, contact your Tektronix representative.

## WORD RECOGNIZER AND CLOCK INTERCONNECT PINS

When one or more 91AE24 expander modules are installed in the mainframe, interconnect pins on the top edge of the modules are used to communicate word recognizer and clock signals.

Each 91AE24 module comes equipped with seven 3-inch interconnect cable assemblies. These cables connect the 91A24 and 91AE24 modules' word recognizer and clock interconnect pins. In addition, some of the 91A24's square-pin jumpers move to interconnect pins on the 91AE24 furthest from the 91A24. Interconnect cables and square-pin jumpers must be correctly installed for the modules to operate properly.

Figure 1 illustrates how the interconnect cables and squarepin jumpers should be installed.

Figure 1. 91A24/91AE24 interconnect pins. This illustration shows correct configurations of interconnect cables and square-pin jumpers. Four possible cases are shown: a 91A24 without 91AE24s, and configurations when one, two, and three 91AE24s are installed.

#### SYNC-OUTPUT CABLE

The 91A24 module comes equipped with a 2-meter coaxial cable. This cable is used to carry a TTL-level sync-output signal. The sync-output signal can be synchronized with recognition of events defined in the Trigger Specification submenu's sequential word recognizer.

The sync-output cable is connected to the 91A24 through back-panel openings on the mainframe. The cable plug-in jack is located on the back edge of the 91A24 module, immediately below the pod C connector. Connection of the sync-output cable is shown in Figure 2.

Figure 2. Connecting P6460 probes and sync-output cable.

#### CONNECTING ACQUISITION PROBES

Data acquistion probes are connected to the 91A24 and 91AE24 through back-panel openings on the mainframe. The probes attach to the modules' pod A, pod B, and pod C connectors.

To connect probes to modules (see Figure 2):

- Grasp the probe by its cable holder.

- Align the cable holder with the module's pod connector.

Be sure the raised tab on the cable holder is facing towards bus slot 0, and is aligned with the opening on the module's pod connector.

- Gently push the cable holder onto the connector. Do not force the connection.

To disconnect the probe, grasp the cable holder and pull gently.

You may damage the probe cable if you disconnect the probe by pulling on the cable rather than the cable holder.

#### P6460 CHARACTERISTICS

The P6460 is a 100 MHz data acquisition probe. Each P6460 provides the 91A24 module with eight data input channels, one qualifier channel, and one clock channel. When connected to a 91AE24 module, only the data channels are active. For P6460 specifications and signal characteristics, refer to *Specifications* in this manual.

Figure 3 illustrates the various elements and features of the P6460 probe. Refer to this figure when reading the following paragraphs.

Probe label for 91A24/91AE24. Each P6460 comes packaged with two gummed signal input labels. Find the label that has Q (qualifier) marked on the left and CK (clock) marked on the right. Place the label on the probe housing location shown in Figure 3.

**Probe Leads and Tips.** Each P6460 probe is supplied with a 10-inch lead set and a package of 12 probe tips (grabbertype). Figure 3 shows connection of the leads and tips.

Connect the lead set to the probe, making sure that the set's white lead is on the side of the probe housing labled CK (clock). Push the lead set's connector into the probe housing. To disconnect the lead set, pull on its connector; do not pull on the leads.

Ground Lead Connections. Also provided with each P6460 are two 5-inch ground sense leads with Pomona Hook tips, and two alligator-clip lead tips. As shown in Figure 3, only one ground lead is required for use with the 91A24 and 91AE24 modules. Plug the lead into either of the probe housing's connectors labeled USERS GND.

Use the alligator-clip tips if necessary to ensure a secure ground connection. (Both types of lead tips make threaded connections to the ground lead.)

The middle GND connector, labeled  $\triangle$ , should only be used when the diagnostic lead set is connected to the probe.

**Maximum Non-destructive Input Voltage.** The maximum input voltage which may be used with the P6460 probe is  $\pm 40 \text{ V}$  peak.

CAUTION

Probe circuitry may be damaged if the P6460 is connected to a voltage source greater than  $\pm 40 \text{ V}$  peak.

Figure 3. P6460 Data Acquisition Probe characteristics and lead connections.

## **OPERATOR'S CHECKOUT**

When the DAS mainframe is powered up, all installed 91A24 or 91AE24 modules will appear on the power-up configuration display. PASS or FAIL notations appear next to each

module to show the results of that module's power-up testing. Table 2 lists and defines the power-up error conditions for 91A24 and 91AE24 modules.

Table 2 POWER-UP ERROR CONDITIONS

| Error Condition                | Definition                                                                                                                                                                                                                                                                                                               |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 91A24 Acquisition Module FAIL  | The 91A24 module has failed the power-up test. The module will not operate properly. Refer the 91A24 module to qualified service personnel.                                                                                                                                                                              |

|                                | This failure does not affect the operation of any installed pattern generator modules or other data acquisition modules, except for 91AE24s. 91AE24 modules will not operate without a working 91A24 module.                                                                                                             |

| 91AE24 Acquisition Module FAIL | The 91AE24 module has failed the power-up test. The module will not operate properly.                                                                                                                                                                                                                                    |

|                                | This failure will occur if the clock and word recognizer interconnect pins are improperly connected by interconnect cables and square-pin jumpers. Power down the mainframe, check the interconnect pins, then power up the mainframe. If the failure continues, refer the 91AE24 module to qualified service personnel. |

|                                | This failure may affect operation of the 91A24 module and/or other 91AE24 modules.                                                                                                                                                                                                                                       |

## CHANNEL SPECIFICATION MENU

For specific information on how to operate the Channel Specification menu, refer to *Channel Specification Menu* in the *DAS 9100 Series Operator's Manual.* The following paragraphs describe only special characteristics of the menu as they apply to the 91A24 module.

#### POWER-UP CHANNEL GROUPING

At power-up, the DAS organizes all 91A24 and 91AE24 pod A data in group A, pod B data in group B, and pod C data in group C. You may regroup channels as desired.

#### **GROUPING DEMULTIPLEXED CHANNELS**

When you have set up demultiplexing in the 91A24 Clock Specification sub-menu, multiplexed data is acquired by pod A. The data is demultiplexed and stored in both pod A and pod B memories (pod B data lines are not connected). In the Channel Specification menu's PROBE column, the data stored in pod B memory is listed as pod B data.

#### THRESHOLD SELECTION

The default THRESHOLD field value for 91A24/91AE24 pods is TTL +1.40 V. When you select VAR, you can specify a threshold in the range of -6.40 V to +6.35 V.

When you set one pod's threshold, the DAS automatically sets all other pods connected to that module with the same threshold value.

## TRIGGER SPECIFICATION MENU

The 91A24 and 91AE24 modules may be used in either of two acquisition modes, selected in the Trigger Specification menu. They are:

- 91A24 ONLY Mode this mode uses one 91A24 and up to three 91AE24 modules for data acquisition.

- 91A24 ARMS Mode ARMS mode allows data acquisition using 91A24/91AE24 modules together with a high-speed data acquisition module. The two types of modules are set up with different clock rates to provide a time-aligned display. When the 91A24 recognizes its trigger event, it arms the high-speed module to look for a second trigger event.

In both 91A24 ONLY and 91A24 ARMS modes, there are two sub-menus for setting up the 91A24: the Trigger Specification and Clock Specification sub-menus. For ARMS mode you set up the high-speed module's trigger and clocking in its ONLY mode, then select the appropriate 91A24 ARMS mode before starting acquisition.

The remainder of this section describes the 91A24 Trigger Specification sub-menu, the 91A24 Clock Specification sub-menu, and specific information for using 91A24 ARMS mode.

## 91A24 TRIGGER SPECIFICATION SUB-MENU

When you press the TRIGGER SPEC key after power-up, the DAS displays the 91A24's Trigger Specification submenu. 91A24 ONLY is the default acquisition mode. In this mode the DAS acquires data using one 91A24 module and up to three 91AE24 modules.

Description of the 91A24 Trigger Specification sub-menu is divided into four topics:

- MODE, SPECIFICATION, and Data Entry Fields describes general-purpose fields in the sub-menu.

- Mnemonics Functions describes the use of recognition mnemonics in data entry fields.

- Data Qualification Functions describes fields and functions which let you specify the kind of data to be stored.

Trigger Functions — describes fields and functions which let you trigger on particular data, and actions which the 91A24 can perform before the trigger occurs.

## MODE, SPECIFICATION, AND DATA ENTRY FIELDS

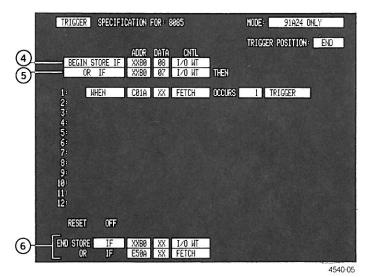

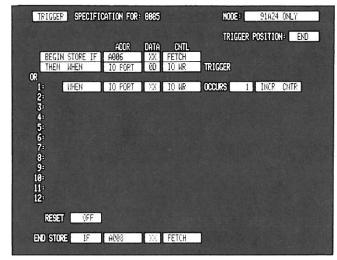

The following paragraphs explain the Trigger Specification sub-menu MODE, SPECIFICATION, and word recognizer fields. Refer to the numbered callouts in Figure 4 when reading the field descriptions.

Specific trigger, storage, and mnemonics functions are described later in this section.

Figure 4. Default 91A24 Trigger Specification sub-menu.

#### 1 MODE Field

(see Figure 4)

The MODE field is used to select among the Trigger Specification menu's available trigger modes. Which modes are available depends on which acquisition modules are installed in the mainframe. The field only appears in reverse video if more than one type of acquisition module is installed in the mainframe. The default mode is 91A24 ONLY.

#### To change trigger modes:

Press SELECT.

#### (2) SPECIFICATION Field

(see Figure 4)

This field lets you select between the Trigger Specification and Clock Specification sub-menus.

#### To move from one sub-menu to the other:

Press SELECT.

For details of clock specification, refer to 91A24 Clock Specification Sub-menu.

#### NOTE

If there is a MICRO NAME specified in the Define Mnemonics menu, the field's SPECIFICATION label changes to read SPECIFICATION FOR: [micro name]. Refer to the Define Mnemonics section of this manual for details.

## 3 Data Entry Fields

(see Figure 4)

The word recognizer data entry fields are organized in channel group columns. Channel group names are indicated above each group column.

#### NOTE

You can specify special group column headings in the Define Mnemonics menu. For details, refer to the Define Mnemonics Menu section of this manual.

#### To enter numeric data values:

Use the data entry keys.

Don't care (X) values are entered using the DON'T CARE key.

You can also use mnemonics in data entry fields. For details refer to the following *Mnemonics Functions* discussion and to the *Define Mnemonics Menu* section of this manual.

A channel group's data entry field will not be displayed if it's width exceeds 30 characters. The width of a group's field depends on the number of channels in the group and the group's display radix. You can alter channel grouping and display radix in the Channel Specification menu.

When the DAS cannot display all of the group columns on the display, it displays one or both of the messages <- MORE and MORE ->. The sub-menu allows you to scroll channel group columns sideways onto the display.

#### To scroll group columns:

Simultaneously press the SHIFT and  $\triangleright$  or  $\triangleleft$  SCROLL keys.

The DAS scrolls group columns onto the display one at a time, and indicates the direction in which other columns are hidden.

#### MNEMONICS FUNCTIONS

Working with the Define Mnemonics menu, the 91A24 Trigger Specification sub-menu provides a special function which permits you to use mnemonics in data entry fields. This feature is enabled by setting up special tables in the Define Mnemonics menu.

In these tables, called [group]\* tables, you list numeric values and their associated mnemonics. Each [group]\* table corresponds to a particular channel group, and can provide mnemonics for that group's data entry fields in the 91A24 Trigger Specification sub-menu.

For details on setting up 91A24-compatible [group]\* tables, refer to the *Define Mnemonics Menu* section of this manual.

Once you have set up [group]\* tables, their mnemonics and associated data values are easily obtained in data entry fields.

#### To obtain table mnemonics in a data entry field:

Press SELECT.

The first mnemonic listed in the corresponding [group]\* table will appear in the data entry field.

#### To choose from mnemonics listed in the table:

Press INCR to obtain the table's next mnemonic. Press DECR to obtain the previous mnemonic.

#### To return to numeric entry in a data entry field:

Press SELECT to obtain the numeric value associated with the mnemonic currently in the field, or press DON'T CARE to return the field to all don't cares (Xs).

#### DATA QUALIFICATION FUNCTIONS

The 91A24 offers special functions for qualifying data storage: BEGIN STORE IF, END STORE IF, and STORE ONLY IF. The following paragraphs describe how to use the Trigger Specification sub-menu to set up data qualification. They discuss each relevant field in the sub-menu and explain its optional values.

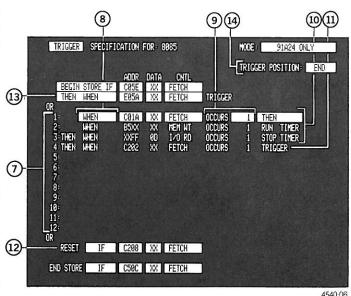

Figure 5 illustrates a typical 91A24 Trigger Specification submenu and its fields. Refer to the numbered callouts in Figure 5 when reading the following field descriptions.

Figure 5. 91A24 Trigger Specification sub-menu and its data qualification functions. This example shows parallel BEGIN STORE and END STORE qualifiers.

## (see Figure 5)

Press SELECT to choose between the following functions:

BEGIN STORE IF – the field's default function. When the event specified in the adjacent word recognizer fields is recognized, the DAS stores the BEGIN STORE and subsequent words until it recognizes an END STORE event. You can use the BEGIN STORE and END STORE functions to qualify specific blocks of data for storage.

#### NOTE

Data values entered in the sequential word recognizer, RESET word recognizer, and triggering parallel word recognizer are compared only to data that is qualified for storage. Therefore, values specified in these word recognizers must be a subset of qualified data.

**STORE ONLY IF** – directs the DAS to store a single cycle of data only if it meets the criteria you've specified in the adjacent word recognizer fields.

This function can be useful when you are interested in storing only a particular type of cycle, such as I/O reads.

### 5 Parallel Word Recognizer

(see Figure 5)

This field allows you to add a parallel ORed word recognizer for BEGIN STORE IF or STORE ONLY IF functions. It can also be used as a global ORed trigger word.

#### Press SELECT to obtain the following functions:

**THEN** – no operation is performed. The default value for this field. The DAS does not display data entry fields.

#### THEN WHEN...TRIGGER

**THEN WHEN NOT...TRIGGER** – both selections set up an ORed word recognizer for triggering. For details, refer to *Trigger Functions* in this section.

OR IF – provides a second word recognizer for the BEGIN STORE IF or STORE ONLY IF function (whichever is selected in the field directly above). The two word recognizers work in parallel and are logically ORed.

Using parallel word recognizers, you can specify two different recognition values for the same data qualification function.

### 6 END STORE Qualifier

(see Figure 5)

The END STORE function ends data storage until the DAS recognizes a BEGIN STORE data word. Up to two END STORE word recognizers are available.

Using BEGIN STORE and END STORE qualifiers, you can qualify specific blocks of data for storage and triggering. This allows you to avoid storing irrelevant data between occurrences of the target blocks.

#### NOTE

Data words which cause an END STORE to occur are not stored in the DAS acquisition memory.

In default, no data entry fields are displayed, and OFF is displayed in reverse video. When you select a value other than OFF, data entry fields appear to the right of the END STORE field.

#### NOTE

If you select the sub-menu's STORE ONLY IF function, the DAS turns the END STORE field OFF. Any END STORE values previously entered will be retained by the DAS, but are inactive.

Press SELECT to obtain the following END STORE options:

**END STORE OFF** – data storage is never disabled. This is the field's default value. No data entry fields are (12) displayed.

**END STORE IF** – ends data storage if the value in the adjacent data entry fields is recognized.

BEGIN STORE has precedence over END STORE. For example, if you specify END STORE on all don't cares (Xs), the DAS stores only those words that match the BEGIN STORE value.

**END STORE IF NOT** – ends data storage if the data value is NOT recognized.

#### END STORE IF

**OR** IF – provides two parallel ORed word recognizers for the END STORE function. The DAS ends storage if it recognizes either of the data values.

#### TRIGGER FUNCTIONS

For triggering, the 91A24 offers a 16-level sequential word recognizer, a word recognizer which resets the sequential word recognizer, and a parallel word recognizer which can trigger independently of the sequential word recognizer.

#### NOTE

Data values entered in the sequential word recognizer, RESET word recognizer, and triggering parallel word recognizer are compared only to data that is qualified for storage. Therefore, values specified in these word recognizers must be a subset of qualified data.

The following paragraphs describe how to use the Trigger Specification sub-menu to set up trigger parameters. They discuss each relevant field in the sub-menu and explain its optional values.

Figure 6 illustrates a typical 91A24 Trigger Specification submenu and its fields. Refer to the numbered callouts in Figure 6 when reading the following trigger function descriptions.

Figure 6. 91A24 Trigger Specification sub-menu and its trigger functions.

## Sequential Word Recognizer

(see Figure 6)

The sequential word recognizer lets you build up to 16 levels of word recognition. You can use the sequential word recognizer for triggering and a variety of other actions.

The sub-menu also provides a RESET word recognizer which can return the sequential word recognizer to its first level. Note that if a sequential word recognizer value and the RESET value are recognized during the same clock cycle, no reset occurs.