# MODEL 650 MAINTENANCE MANUAL

© 1987 Wavetek

THIS DOCUMENT CONTAINS INFORMATION PROPRIETARY TO WAVETEK AND IS PROVIDED SOLELY FOR INSTRUMENT OPERATION AND MAINTENANCE. THE INFORMATION IN THIS DOCUMENT MAY NOT BE DUPLICATED IN ANY MANNER WITHOUT THE PRIOR APPROVAL IN WRITING FROM WAVETEK.

Manual Revision 9/88 Manual Part Number: 1300-00-0420

# Scans By *Artek Media*

Artek Media 1042 Plummer Cir. SW Rochester, MN 55902

# www.artekmedia.com

"High resolution scans of obsolete technical manuals"

If your looking for a quality scanned technical manual in PDF format please visit our WEB site at <a href="www.artekmedia.com">www.artekmedia.com</a> or drop us an email at <a href="manuals@artekmedia.com">manuals@artekmedia.com</a> and we will be happy to email you a current list of the manuals we have available.

If you don't see the manual you need on the list drop us a line anyway we may still be able to point you to other sources. If you have an existing manual you would like scanned please write for details, This can often be done very reasonably in consideration for adding your manual to our library.

Typically the scans in our manuals are done as follows;

- 1) Typed text pages are typically scanned in black and white at 300 dpi.

- 2) Photo pages are typically scanned in gray scale mode at 600 dpi

- 3) Schematic diagram pages are typically scanned in black and white at 600 dpi unless the original manual had colored high lighting (as is the case for some 70's vintage Tektronix manuals).

If you purchased this manual from us (typically through our Ebay name of ArtekMedia) thank you very much. If you received this from a well-meaning "friend" for free we would appreciate your treating this much like you would "share ware". By that we mean a donation of at least \$5-10 per manual is appreciated in recognition of the time (a manual can take as much as 40 hours to reproduce, book, link etc.), energy and quality of effort that went into preserving this manual. Donations via PayPal go to: <a href="manuals@artekmedia.com">manuals@artekmedia.com</a> or can be mailed to us the address above.

Thanks

Dave & Lynn Henderson

paul & Symmeth

Artek Media

# WARRANTY

Wavetek warrants that all products manufactured by Wavetek conform to published Wavetek specifications and are free from defects in materials and workmanship for a period of one (1) year from the date of delivery when used under normal operating conditions and within the service conditions for which they were furnished.

The obligation of Wavetek arising from a Warranty claim shall be limited to repairing, or at its option, replacing without charge, any product which in Wavetek's sole opinion proves to be defective within the scope of the Warranty. In the event Wavetek is not able to modify, repair or replace non-conforming defective parts or components to a condition as warrantied within a reasonable time after receipt thereof, Buyers shall be credited for their value at the original purchase price.

Wavetek must be notified in writing of the defect or nonconformity within the Warranty period and the affected product returned to Wavetek's factory or to an authorized service center within (30) days after discovery of such defect or nonconformity.

For product warranties requiring return to Wavetek, products must be returned to a service facility designated by Wavetek. Buyer shall prepay shipping charges, taxes, duties and insurance for products returned to Wavetek for warranty service. Except for products returned to Buyer from another country, Wavetek shall pay for return of products to Buyer.

Wavetek shall have no responsibility hereunder for any defect or damage caused by improper storage, improper installation, unauthorized modification, misuse, neglect, inadequate maintenance, accident or for any product which has been repaired or altered by anyone other than Wavetek or its authorized representative and not in accordance with instructions furnished by Wavetek.

#### **Exclusion of Other Warranties**

The Warranty described above is Buyer's sole and exclusive remedy and no other warranty, whether written or oral, is expressed or implied. Wavetek specifically disclaims the implied warranties of merchantability and fitness for a particular purpose. No statement, representation, agreement, or understanding, oral or written made by an agent, distributor, representative, or employee of Wavetek, which is not contained in the foregoing Warranty will be binding upon Wavetek, unless made in writing and executed by an authorized Wavetek employee. Under no circumstances shall Wavetek be liable for any direct, indirect, special, incidental, or consequential damages, expenses, losses or delays (including loss of profits) based on contract, tort, or any other legal theory.

# SAFETY FIRST

# Protect yourself. Follow these precautions:

- Don't touch the outputs of the instrument or any exposed test wiring carrying the output signals. This-instrument can generate hazardous voltages and currents.

- Don't bypass the power cord's ground lead with two-wire extension cords or plug adaptors.

- Don't disconnect the green and yellow safety-earth-ground wire that connects the ground lug of the power receptacle to the chassis ground terminal (marked with (♣) or △).

- Don't hold your eyes extremely close to an rf output for a long time. The normally nonhazardous low-power rf energy generated by the instrument could possibly cause eye injury.

- Don't plug in the power cord until directed to by the installation instructions.

- Don't repair the instrument unless you qualify and know how to work with hazardous voltages.

- Pay attention to the WARNING statements. They point out situations that can cause injury or death.

- Pay attention to the CAUTION statements. They point out situations that can cause equipment damage.

#### **WARNING**

DO NOT RECHARGE, SHORT CIRCUIT, DISASSEMBLE, OR APPLY HEAT TO THE LITHIUM BATTERY INSIDE THE 650. VIOLATING THIS RULE COULD RELEASE POTENTIALLY HARMFUL LITHIUM. OBSERVE POLARITY WHEN YOU REPLACE THE BATTERY.

#### CAUTION

The 650 can deliver up to  $12\frac{1}{2}$  watts of output power. Always keep the output signal levels within the power range of your load.

# 4

# -WARNING-

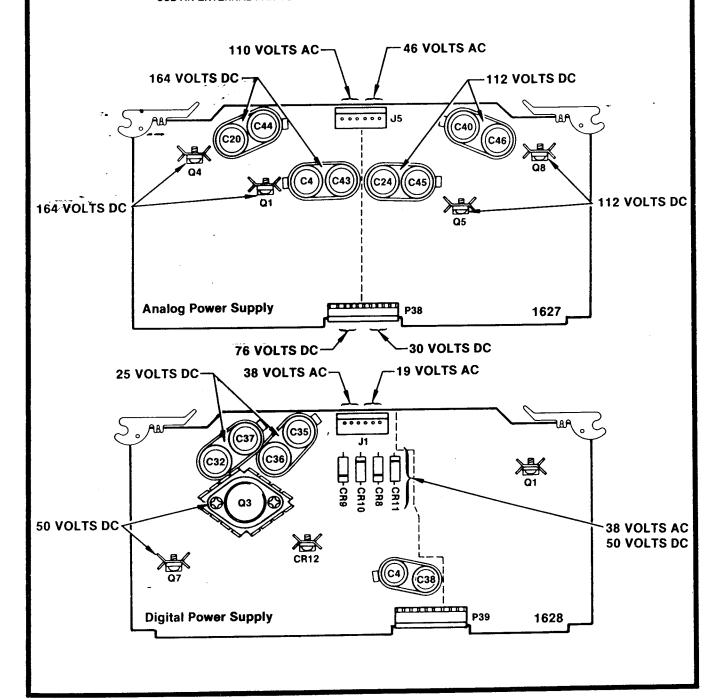

# DANGEROUS POWER SUPPLIES LETHAL VOLTAGES — HIGH CURRENTS — HOT HEATSINKS

DO NOT ATTEMPT TO REPAIR THE POWER SUPPLIES UNLESS YOU KNOW HOW TO WORK SAFELY WITH HIGH VOLTAGE, HIGH CURRENT, AND HIGH POWER.

WEAR SAFETY GLASSES AT ALL TIMES — DEFECTIVE CAPACITORS CAN EXPLODE.

CAPACITORS REQUIRE 40 SECONDS TO DISCHARGE.

USE AN EXTERNAL FAN TO COOL ANY SUPPLY OPERATED OUTSIDE THE 650 CHASSIS.

# CONTENTS

| CH 1 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                               |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 1.1 Specifications                                                                                                                                                                                                                                                                                                                                                         |

| СН 2 | THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                        |

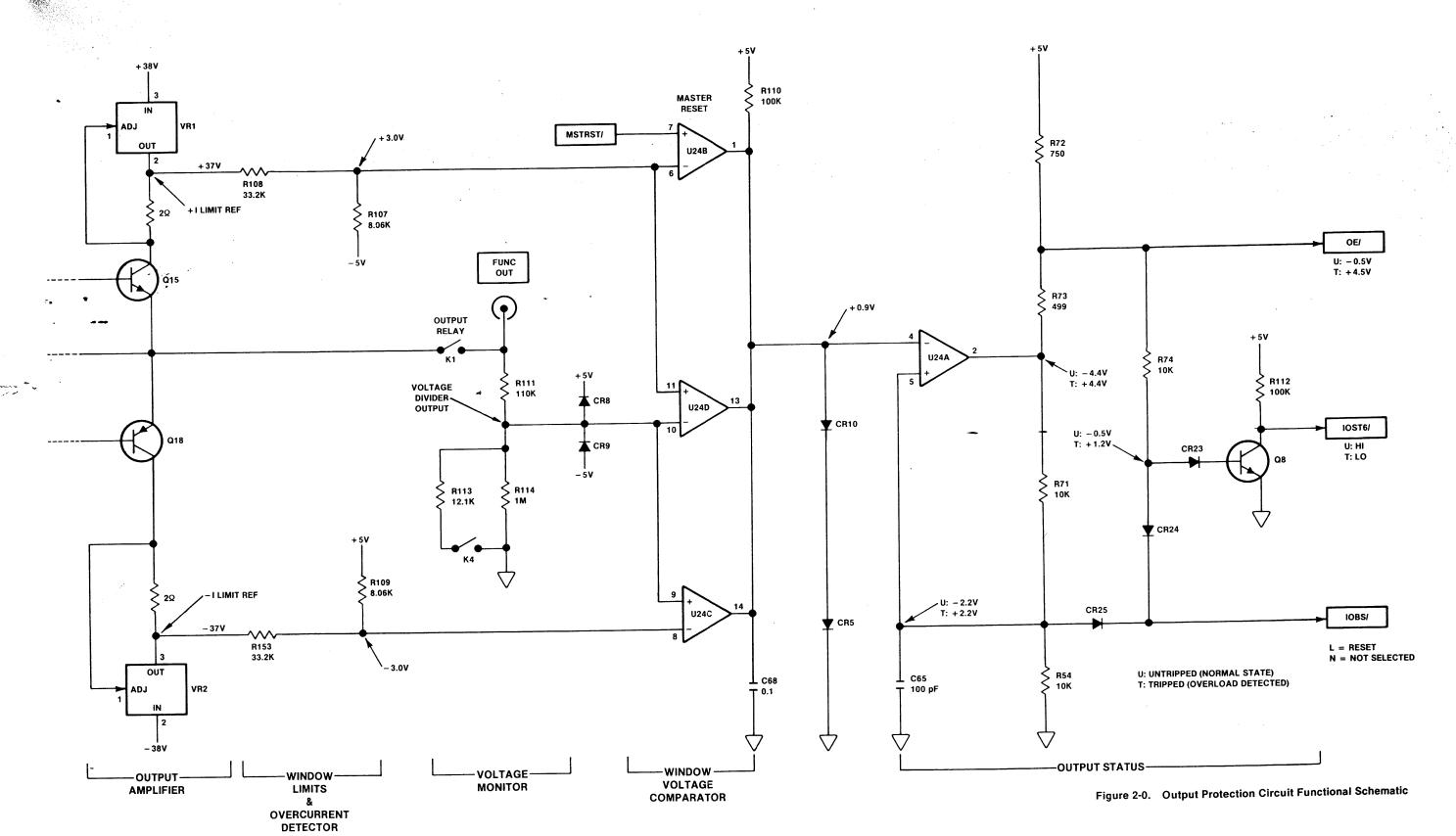

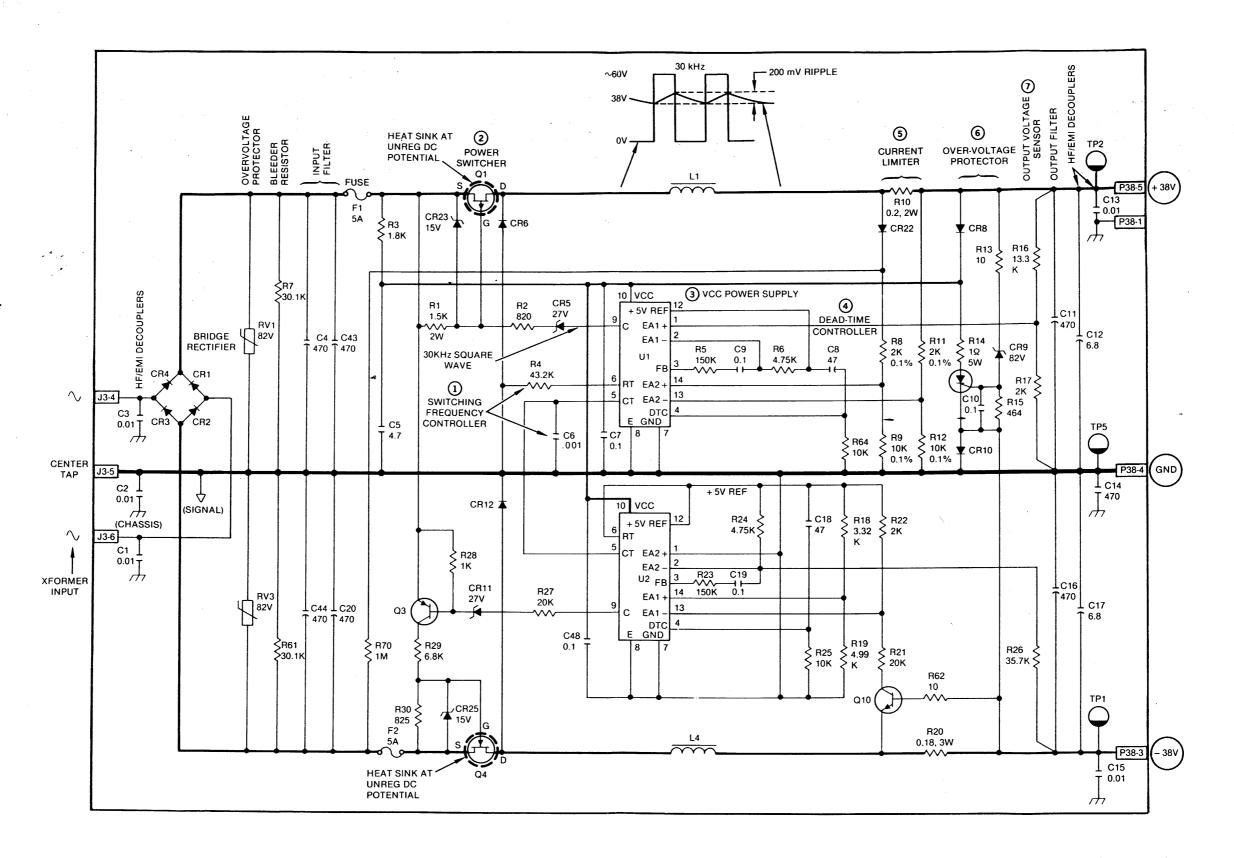

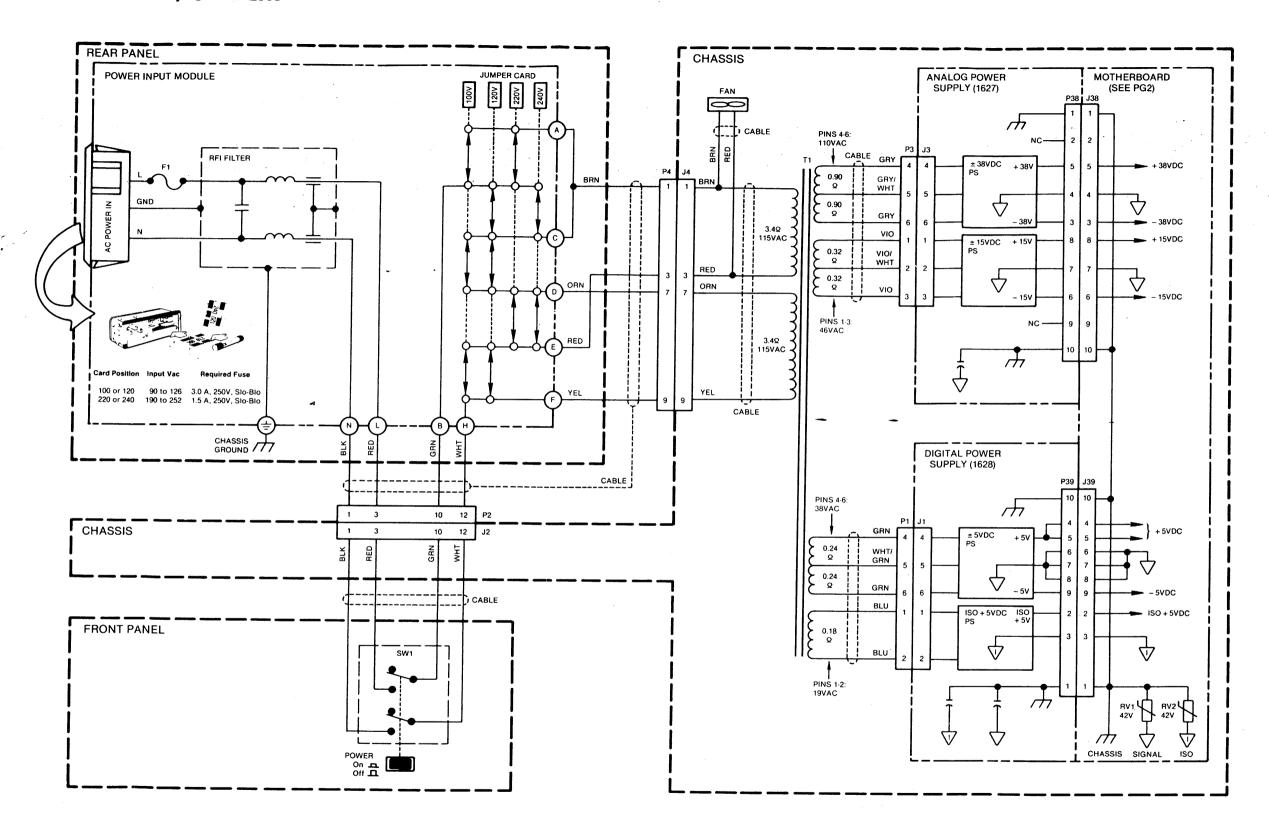

|      | 2.1 System Overview        2-2         2.2 Input Board Set (1473, 1474)        2-7         2.3 Main Microprocessor/Sample and Hold Board (1531)        2-7         2.4 Phase Engine Board (1625)            2.5 Phase Accumulator Board (1383)            2.6 RAM Board (1458)             2.7 DAC/Output Board (1467)              2.8 Reference/Calibration Board (1615) |

| CH 3 | PERFORMANCE VERIFICATION PROCEDURES                                                                                                                                                                                                                                                                                                                                        |

|      | 3.1 Quick Functional Check                                                                                                                                                                                                                                                                                                                                                 |

| CH 4 | PARTS AND SCHEMATICS                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.1 Drawings                                                                                                                                                                                                                                                                                                                                                               |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 SPECIFICATIONS

Instrument specifications are located in section 1 of the Model 650 Operator's Manual.

# 1.2 TOOLS AND TEST EQUIPMENT

You must have the following equipment to test, troubleshoot, calibrate and repair the 650.

<u>Basic Equipment</u>. You must have the following equipment for the procedures in the following sections:

#### Phase Measurement

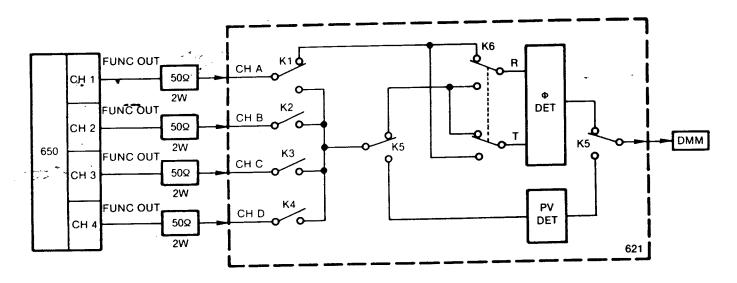

Wavetek Model 601 Switching System Master Chassis Wavetek Model 603 Switching System Front Panel Wavetek Model 621 Switching System Phase Detector Module

#### Signal Sources

Wavetek Model 271 12MHz Pulse/Function Generator Wavetek Model 178 Programmable Waveform Synthesizer Wavetek Model 650 2MHz Variable Phase Synthesizer

#### CHAPTER 2

#### THEORY OF OPERATION

#### Section

- 2.1 System Overview

- 2.2 Input Board Set

- 2.3 MicroProcessor/S&H Board

- 2.4 Phase Engine Board

- 2.5 Phase Accumulator Board

- 2.6 RAM Board

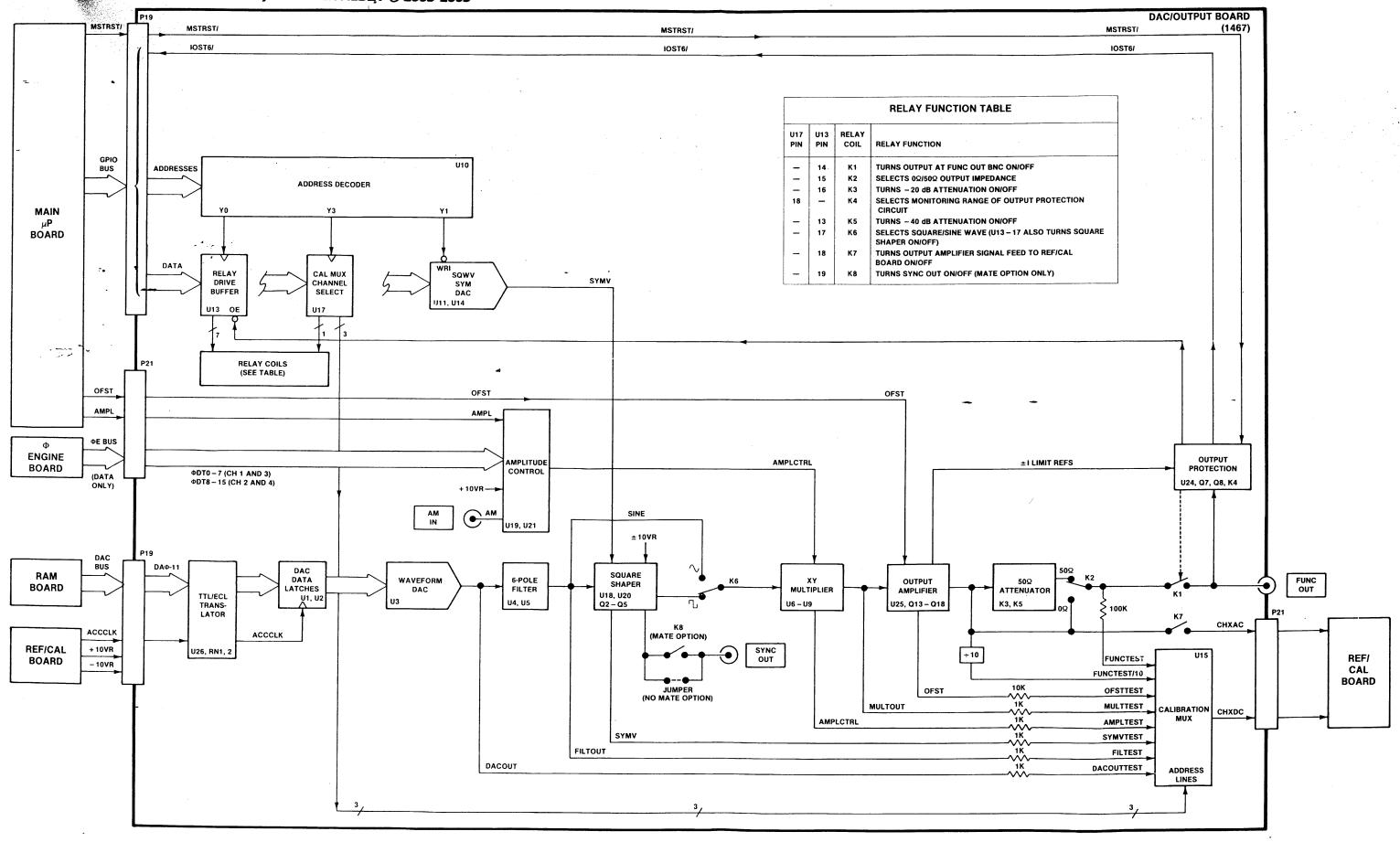

- 2.7 DAC/Output Board

- 2.8 Ref/Cal Board

2.9 Power Supplies

#### Function

Tells what the 650 does, how phase accumulation works, and what hardware performs each major function.

Lists the board functions, provides a block diagram to the circuit level, and describes individual circuits.

Explains circuit operation of the switching power supplies.

See section 4 for wiring diagrams and schematics.

#### 2.1 SYSTEM OVERVIEW

#### Section

#### Why You Should Read the Section

- 2.1.1 What Does the 650 Do?

- You need to know what the 650 can do before you can understand how it works. Therefore, this section first describes phase synthesis, then lists all the other capabilities that support it.

- 2.1.2 How Does Phase Accumulation Work?

- You need to understand phase accumulation before you study the circuits that perform it. Therefore, this section first describes this important concept, then shows how the 650 uses it to sweep frequency and phase.

- 2.1.3 What Does Each Board Do?

- You need to know what each board does so you can relate the 650's functions to the circuits that perform them. Therefore, this section provides a system block diagram that shows all the boards and lists the functions each one performs.

#### 2.1.1 What Can the 650 Do?

This section describes phase synthesis and lists all the 650 capabilities that support it. Knowing what the 650 can do will help you understand how it works.

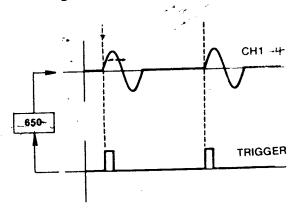

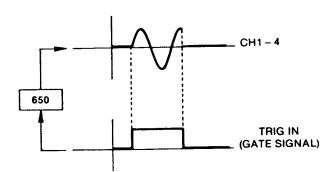

Phase Synthesis. The Model 650 Variable Phase Synthesizer generates multiple waveforms at controlled phase angles. Each channel's output signal maintains an absolutely fixed and precisely controllable phase relationship with the output signals of the other channels. Phase accuracy holds for fixed frequency, swept frequency, and swept phase operation. Digital generation of the signals guarantees fixed accuracy across the entire range of frequency and phase.

<u>Support Capabilities</u>. The additional capabilities listed below support the 650's primary role as a phase synthesizer and enable it to serve both phase and non-phase applications.

| Category                          |                                                                                                                                                                              | Capabili                                                                                                  | ties       |                                                                  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------|

| Non-Sweep Modes                   | Continuous<br>Triggered<br>Burst                                                                                                                                             | Sync Gated<br>Async Gated<br>Phase Lock                                                                   |            | Waveform Hold<br>AM                                              |

| Sweep Choices                     | Frequency Sweep Phase Sweep Both Sweep Sequential Sweep                                                                                                                      | Hold Sweep<br>Linear Sweep<br>Log Sweep                                                                   |            | Sine Sweep<br>Random Sweep<br>AM/FM/PM                           |

| Frequency/Phase/ Both Sweep Modes | Continuous Sweep with An Continuous Sweep with An Triggered Sweep with Aut Triggered Sweep with Aut Triggered Sweep/Hold wit Reset/Hold                                      | to Reverse Reverse/Hold Reset Sequential with Triggered Steps Reverse Sequential with Continuous Stepping |            |                                                                  |

| Channel Control                   | Sine, Triangle, Square,<br>Ramp, DC Waveforms<br>Output Impedance<br>Waveform Amplitude                                                                                      | Waveform Offs<br>Square Wave D<br>Phase Control<br>Frequency Mult                                         | outy Cycle | Amplitude Modulation Sync Output Delta Frequency Ramp Duty Cycle |

| Triggering                        | Internal<br>External                                                                                                                                                         | Front Panel<br>GPIB                                                                                       |            |                                                                  |

| Modulation                        | Frequency Modulation Phase Modulation                                                                                                                                        | Amplitude Mod<br>Combined (FM/                                                                            |            |                                                                  |

| Shift Keying                      | Synchronous Frequency Shift Keying (S-FSK) Asynchronous Frequency Shift Keying (A-FSK) Asynchronous Multiple Frequency Shift Keying Asynchronous Multiple Phase Shift Keying |                                                                                                           |            |                                                                  |

| Sweep Progress                    | Screen Sweep Monitor                                                                                                                                                         | Sweep Horizon                                                                                             | ital Out   | Sweep Marker                                                     |

| Unit Control                      | Front Panel                                                                                                                                                                  | GPIB                                                                                                      |            | MATE (optional)                                                  |

| Memory                            | 25 Stored Instrument Set                                                                                                                                                     | ups                                                                                                       | Lost-Pov   | ver Instrument Setup                                             |

| Maintenance                       | Self-Calibration                                                                                                                                                             |                                                                                                           | Self-T     | est                                                              |

THEORY OF OPERATION SYSTEM OVERVIEW

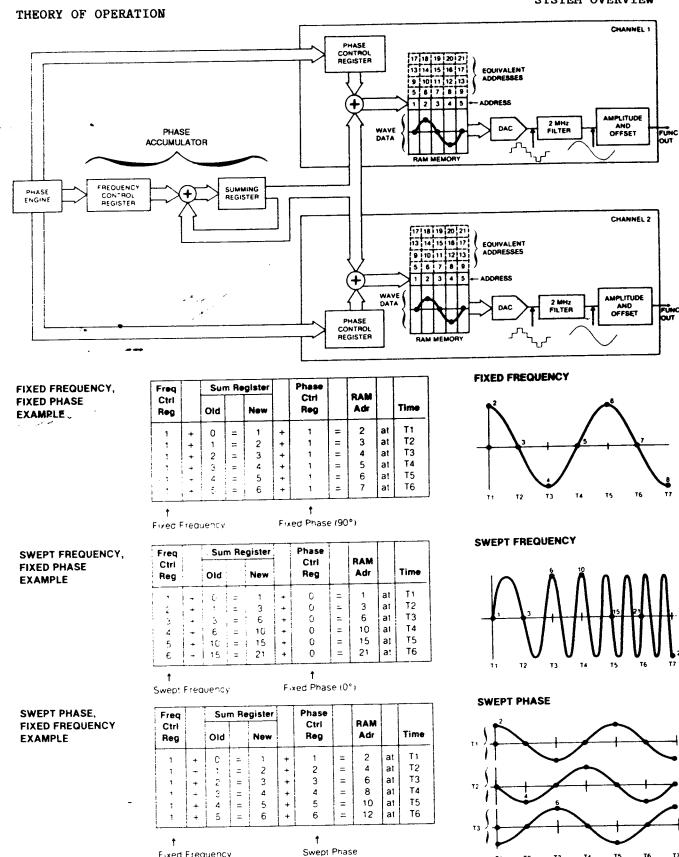

#### 2.1.2 How Does Phase Accumulation Work?

This section describes phase accumulation, then shows how the 650 uses it to sweep frequency and phase. Read this section to learn the basics of this important concept so you can better understand the circuits that perform it.

Basic Concept. Figure 2-1 shows a simplified block diagram of the phase synthesis circuits. To generate a fixed-frequency waveform, the phase engine loads a phase value (such as 0.9°) into the frequency control register of the phase accumulator. The adder then accumulates phase by repeatedly adding this phase value to the total in the summing register. The accumulating phase total sequentially addresses the storage locations of the waveform RAM. As you can see, the phase accumulator actually serves as a RAM address generator.

Because the RAM stores the waveform as a series of digital amplitudes, the RAM output, when applied to the digital-to-analog converter, produces a stairstep waveform. Filtering removes the stairsteps and produces a smooth output.

The address-generation rate of the phase accumulator remains constant at 10MHz. This gives a fixed amount of time between additions for the phase engine to load new values, if any, in the frequency and phase control registers. Because the address generation rate remains fixed, the phase accumulator determines the frequency of the output waveform by jumping over intermediate RAM addresses. The size of the phase value in the frequency control register determines the size of the jumps.

RAM Memory. For simplicity, figure 2-1 shows a sine wave stored as five points. In reality, the 650 stores the waveform as 8192 points. This resolution allows great latitude in skipping steps before the output signal suffers. Output resolution decreases only for extremely wide and fast sweeps.

Waveform Changes. To change a channel's output waveform, the 650 simply loads a new waveshape in the RAM. Each channel can produce a different waveform without affecting phase coherence between channels.

Equivalent Addresses. The "equivalent addresses" shown with the RAM make the example easy to follow. In actual operation, the phase engine loads the registers with adjusted values that produce real RAM addresses instead of the equivalent addresses shown.

**DAC/Filter.** The digital-to-analog converter converts the digital amplitude values emerging from the RAM into a stair-step waveform. The 2MHz output filter removes the 10MHz clock frequency and its harmonics to produce a smooth analog waveform.

Simple Examples. Follow the table for each example to see how the values loaded in the frequency and phase control registers produce the fixed frequency, swept frequency, and swept phase outputs shown.

Swept Phase Illustration. The swept phase illustration shows three snapshots in the leftward progression of a sine wave. The wave begins in the position shown in the top figure. The middle figure shows it after it jumps 90° to the left, and the bottom one shows it after another jump 90° to the left. In actual operation, these large jumps would consist of thousands of very small jumps that would produce a smooth sweep.

Realistic Example. The phase engine actually loads a phase value (such as 0.9°) into the frequency control register. The phase value accumulates in the summing register at the fixed clock rate (10MHz for the 650). This phase accumulation controls addressing of the RAM memory and therefore the frequency of the waveform. To see more realistically how this phase accumulator technique works, assume a phase value of 0.9° and a clock rate of 10MHz:

$$\frac{0.9^{\circ}}{\text{step}} \times \frac{10 \times 10^{6} \text{ steps}}{1 \text{ second}} \times \frac{1 \text{ cycle}}{360^{\circ}} = \frac{9 \times 10^{6} \text{ cycles}}{360 \text{ seconds}} = 25 \text{ kHz output.}$$

$$\frac{360^{\circ}}{\text{cycle}} \times \frac{1 \text{ step}}{0.9^{\circ}} = 400 \text{ discrete steps in each cycle of a 25 kHz outout}$$

Next, assume a phase value of 9° and a clock rate of 10MHz:

$$\frac{9^{\circ}}{\text{step}} \times \frac{10 \times 10^{6} \text{ steps}}{1 \text{ second}} \times \frac{1 \text{ cycle}}{360^{\circ}} = \frac{90 \times 10^{6} \text{ cycles}}{360 \text{ seconds}} = 250 \text{ kHz output}$$

$$\frac{360^{\circ}}{\text{cycle}} \times \frac{1 \text{ step}}{9^{\circ}} = 40 \text{ discrete steps in each cycle of a 250 kHz output.}$$

Main Menu. When you enter a frequency in the main menu, the 650 loads the non-changing phase value that will produce that fixed frequency into the frequency control register.

Sweep Menu. When you enter START and STOP frequencies in the sweep menu, the 650 converts these into the incrementing series of phase values that it loads successively into the frequency control register as the sweep progresses. All channels sweep frequency simultaneously. Similarly, when you enter different START and STOP phases for each channel in the sweep menu, the 650 converts these into a separate series of incrementing values for each channel, then loads these series successively into the phase control registers of the channels as the sweeps progress. Each channel sweeps phase independently.

Channel Menu. When you use the channel menu to select a waveform for a channel, the 650 loads that waveform into the channel's RAM. Similarly, when you enter an amplitude and voltage offset for the waveform, the 650 loads these values into the channel's amplitude and offset circuits. Finally, when you enter a fixed phase shift for a channel, the 650 loads the value that will produce that shift into the channel's phase control register.

76

- DIRECTION OF SWEEP

т3

**T4**

T5

Figure 2-1. How the 650 Generates Phase-Coherent Waveforms

Fixed Frequency

# 2.1.3 What Does Each Board Do?

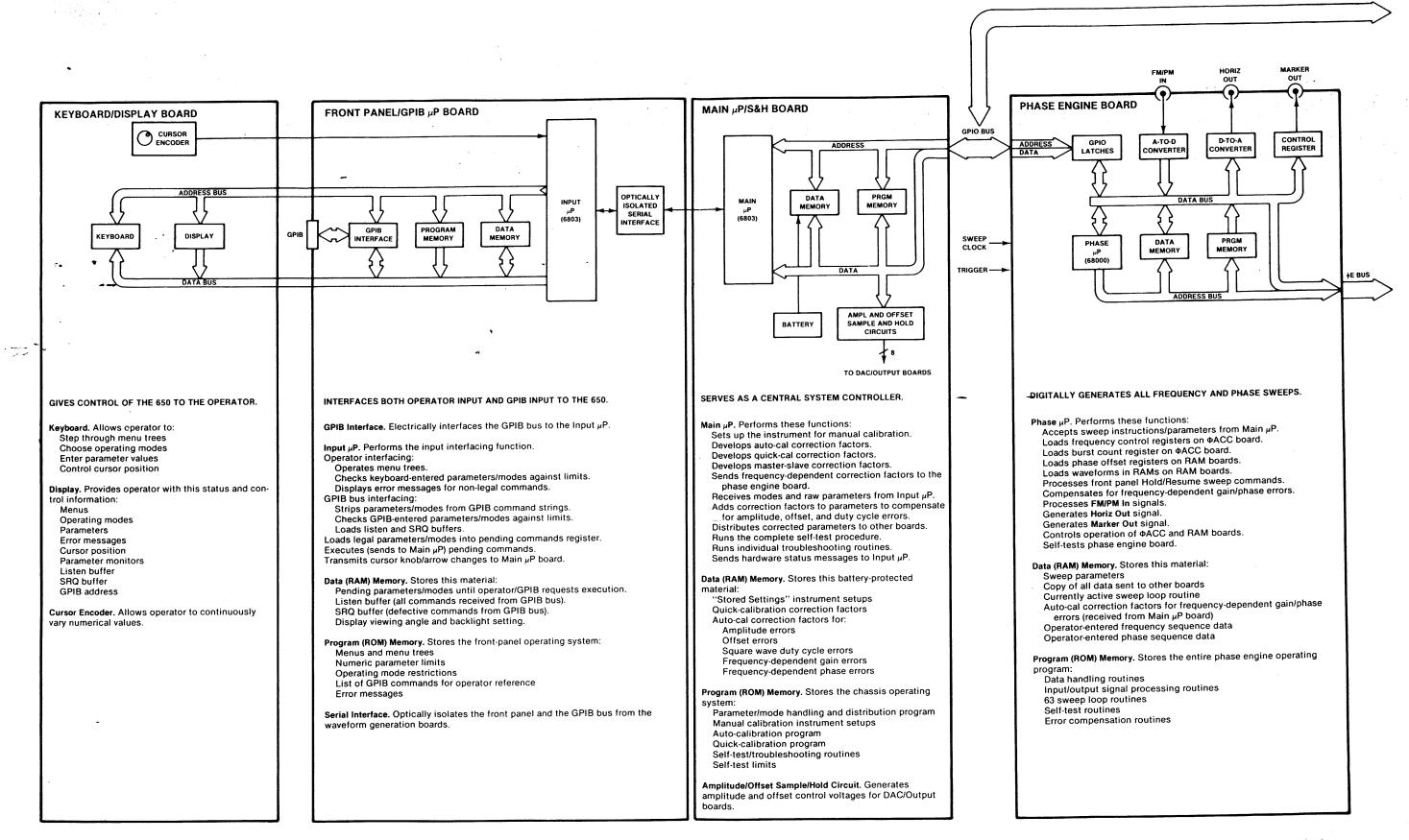

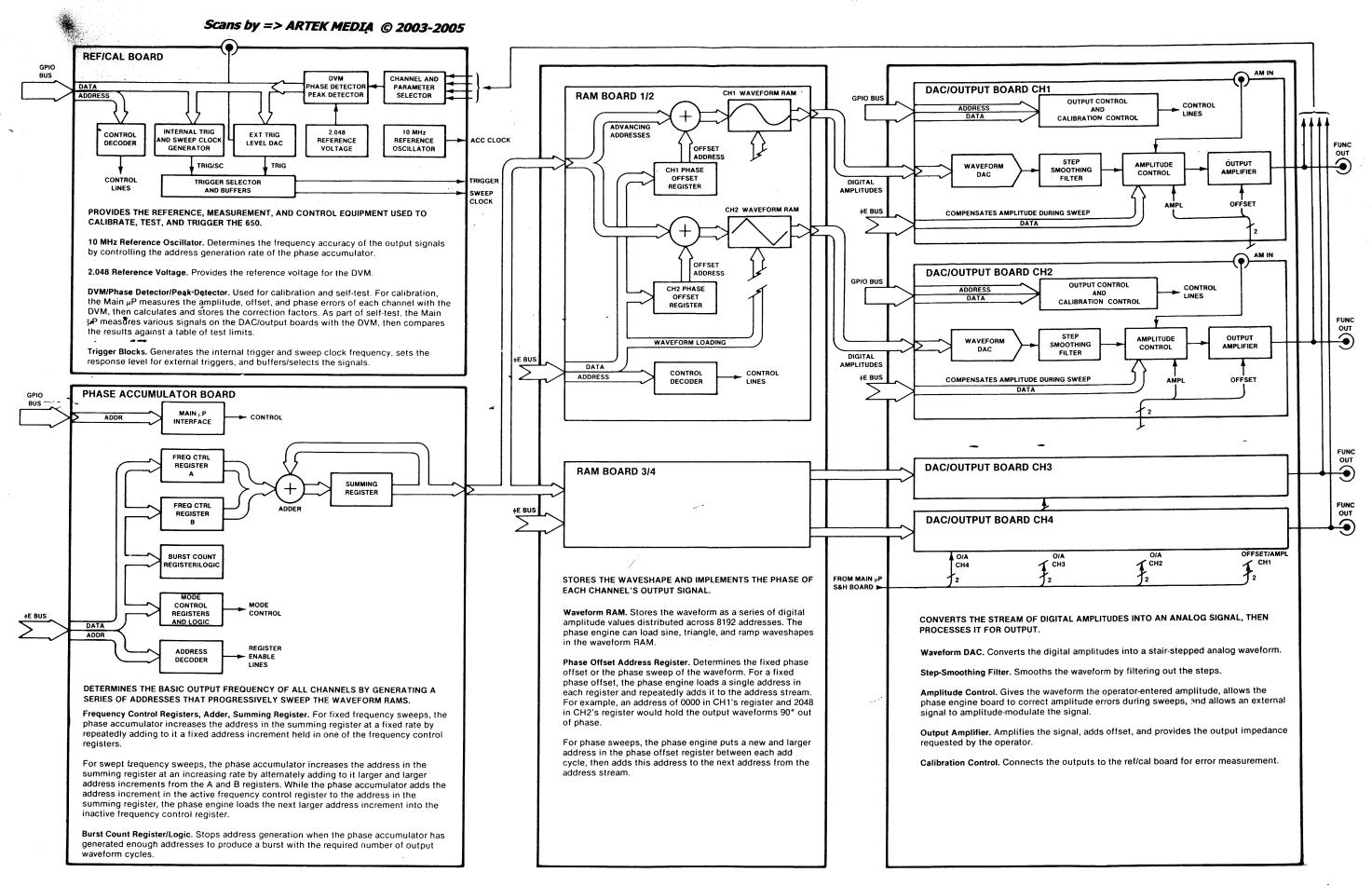

This section provides a system block diagram that shows all the boards of the 650 and lists the functions each one performs. Study this diagram so you can relate the 650's functions to the circuits that perform them.

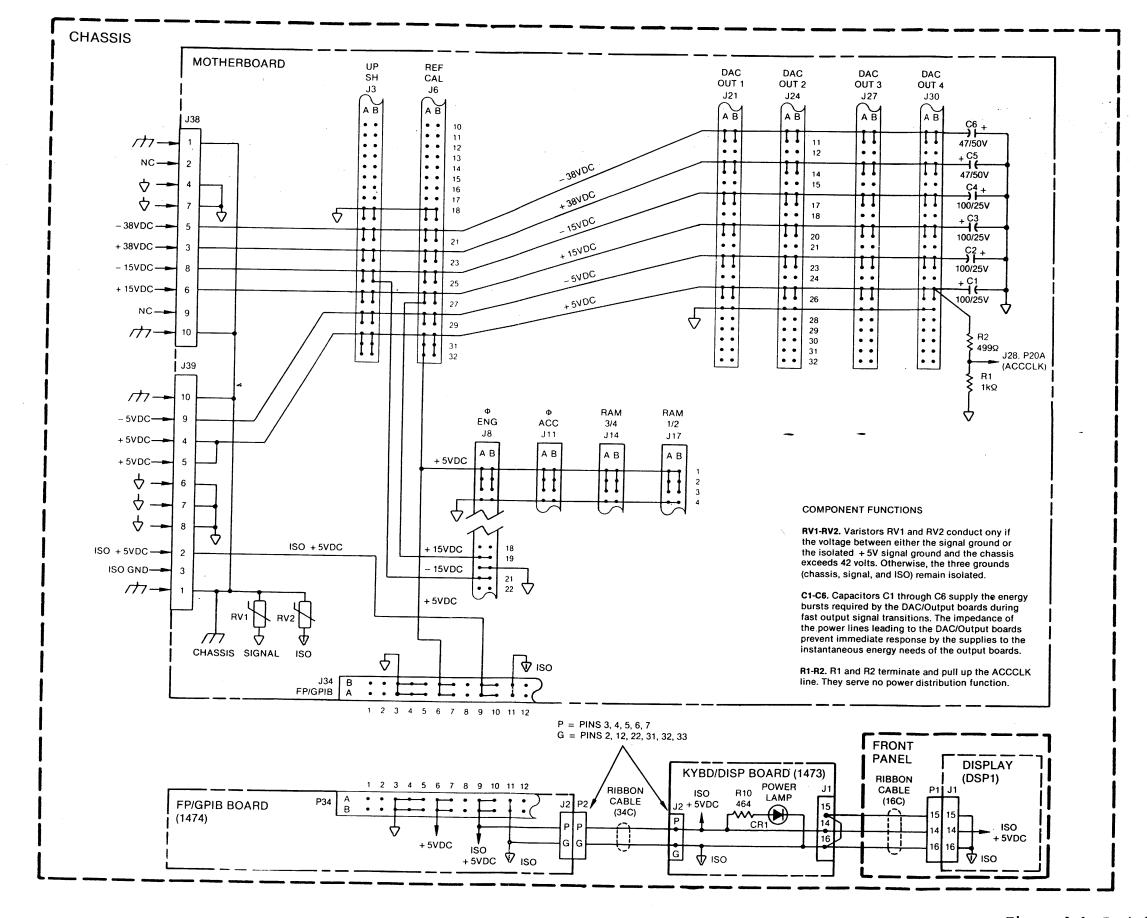

Diagram Explanation. Figure 2-0 shows the system block diagram for the 650. Data and signal processing flows from the keyboard/GPIB inputs at the left to the signal outputs at the right. The blocks of text list the major functions of each board.

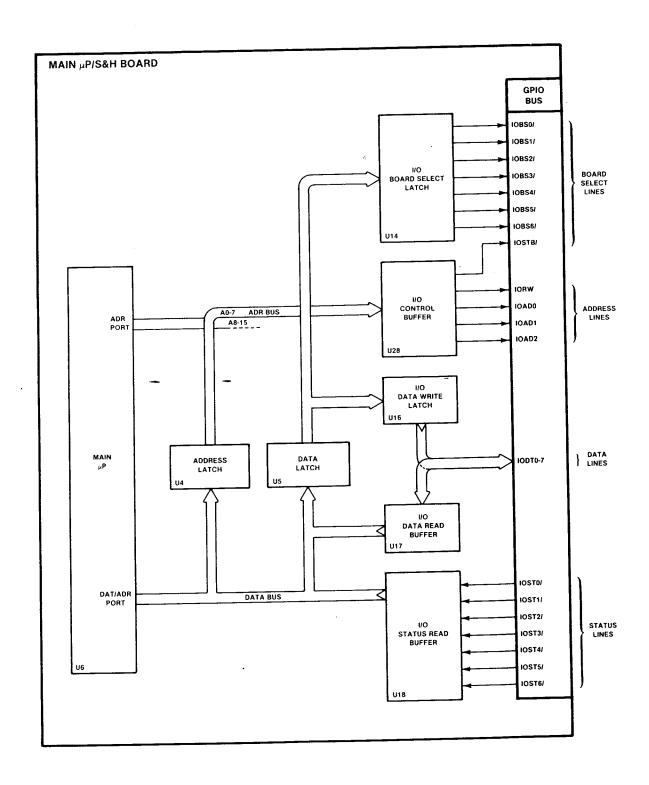

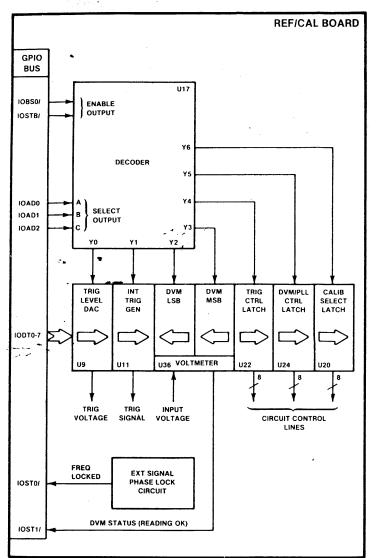

- 2.2 INPUT BOARD SET (1473, 1474) (Refer to figure 2-0.)

- 2.3 MAIN MICROPROCESSOR/SAMPLE AND HOLD BOARD (1531) (Refer to figure 2-0.)

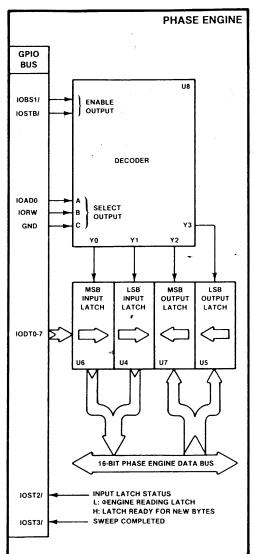

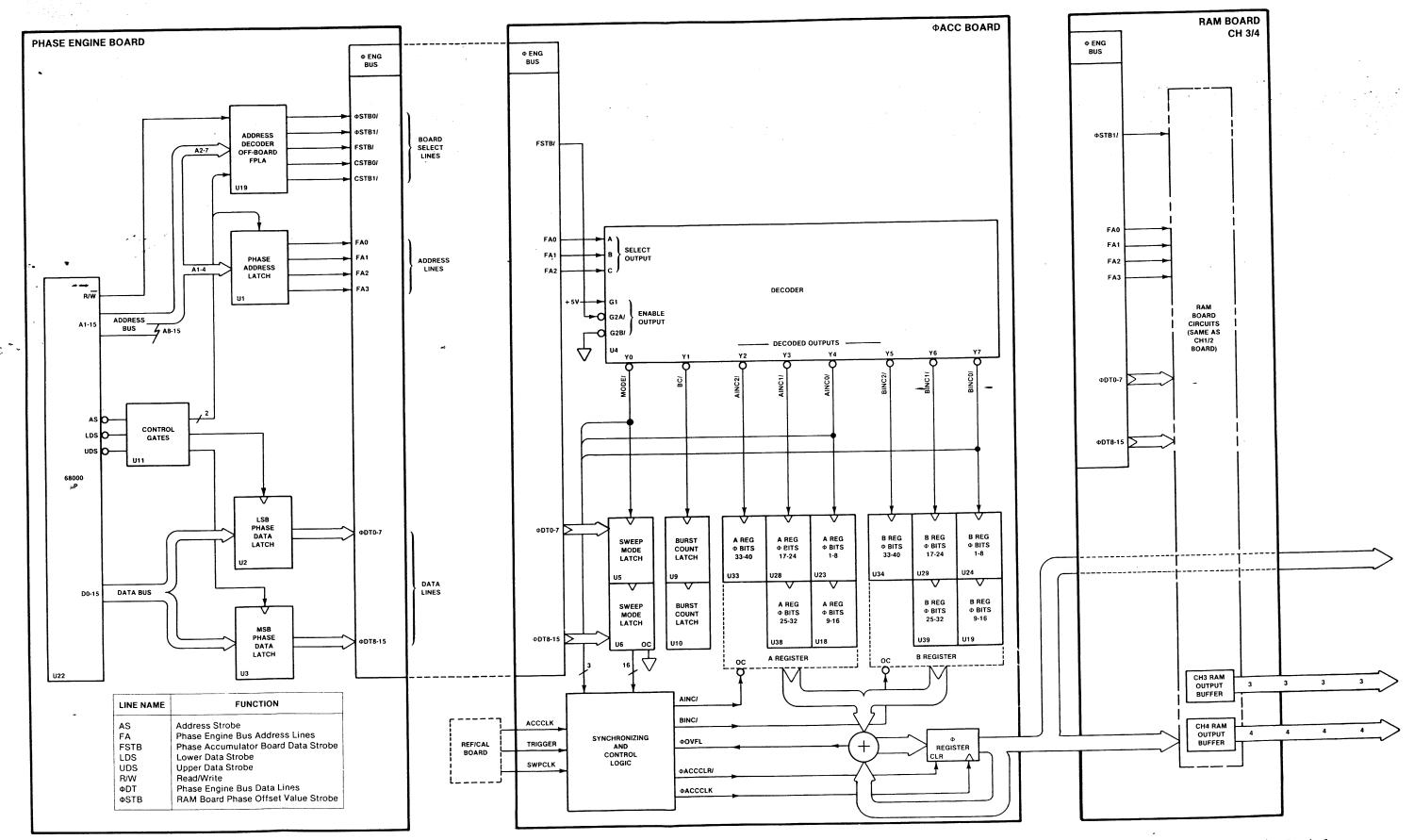

- 2.4 PHASE ENGINE BOARD (1625)

(Refer to figure 2-0.)

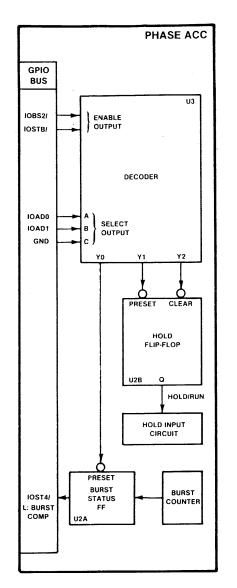

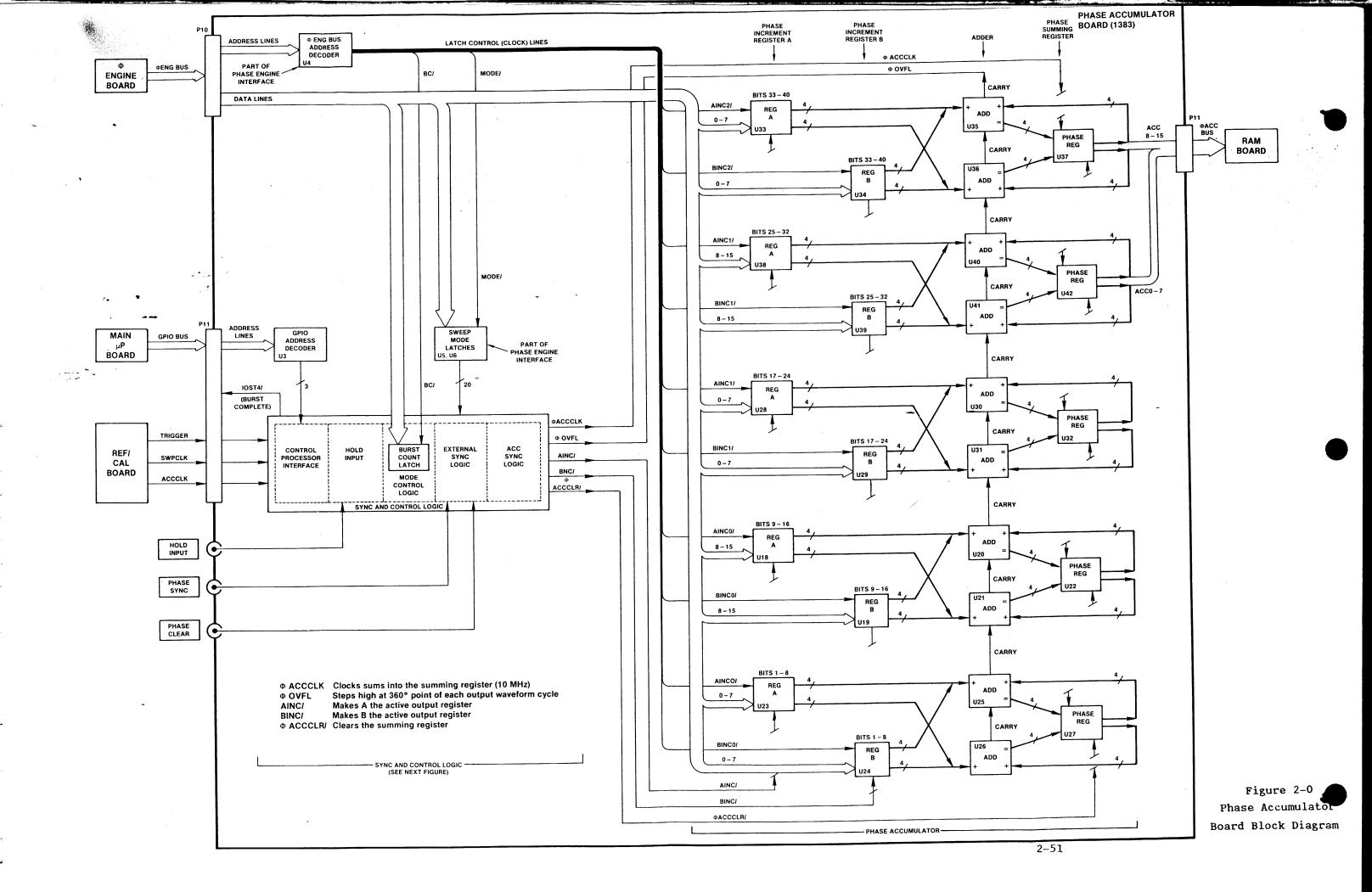

# 2.5 PHASE ACCUMULATOR BOARD (1383)

Major Function. The phase accumulator board determines the basic output frequency of all channels by generating a series of addresses that sweep through the waveforms stored in the RAMs on the RAM boards.

| SUBFUNCTION                                                                 | ACTIVE PHASE ACC BOARD CIRCUITS                                                                     | SECTION                                   |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------|

| Sweep/Waveform Hold via the Hold Input Connector                            | Hold Input                                                                                          | 2.5.4                                     |

| Sweep Hold via [Hold/Resume] key or the GPIB bus                            | Control Processor Interface<br>Hold Input                                                           | 2.5.3<br>2.5.4                            |

| Master/Slave Operation                                                      | External Sync Logic  Phase Sync and Phase Clear  Connectors                                         | 2.5.6                                     |

| [Main] CONT, TRIG, A-GATE,<br>S-GATE, and PHSLK Modes<br>[Sweep] Modes 1-29 | Mode Control Logic<br>External Sync Logic<br>Acc Sync Logic<br>Phase Accumulator                    | 2.5.5<br>2.5.6<br>2.5.7<br>2.5.1          |

| [ <u>Main</u> ] BURST Mode                                                  | Control Processor Interface Mode Control Logic External Sync Logic Acc Sync Logic Phase Accumulator | 2.5.3<br>2.5.5<br>2.5.6<br>2.5.7<br>2.5.1 |

| Control by Main MicroP Board<br>(over the GPIO bus)                         | Control Processor Interface                                                                         | 2.5.3                                     |

| Control by Phase Engine Board<br>(over the phase engine bus)                | Phase Engine Interface<br>(bus address decoder/mode<br>latches)                                     | 2.5.2                                     |

| •                                | INFORMATION IN THIS SECTION                                                                              |                            |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|--|

| INFORMATION FUNCTION             |                                                                                                          | LOCATION                   |  |

| Block Diagram                    | Shows data and control flow, circuit interaction, and related boards.                                    | Figure 2-0                 |  |

| Sync and Control<br>Logic Figure | Shows how the sync and control logic circuits generate the five major phase accumulator control signals. | Figure 2-0                 |  |

| Circuit Description Text         | Individually describes the operation of each phase accumulator circuit.                                  | Sections 2.5.1<br>to 2.5.7 |  |

| Signal Description<br>Table      | Describes the function and action of each phase accumulator board signal. Alphabetical by signal name.   | Table 2-0                  |  |

| RELATED INFORMATION IN OTHER SECTIONS |                                                                                          |                           |

|---------------------------------------|------------------------------------------------------------------------------------------|---------------------------|

| INFORMATION                           | FUNCTION                                                                                 | LOCATION                  |

| GPIO Bus Figure                       | Shows how the main $\mu P$ board controls the phase accumulator board over the GPIO bus. | Figure 2-0 in section 2.3 |

| ΦENG Bus Figure                       | Shows how the phase engine board controls the phase accumulator board over the ΦENG bus. | Figure 2-0 in section 2.4 |

# 2.5.1 Phase Accumulator Circuit

<u>Function</u>: Generate a series of increasing addresses by repeatedly adding a small phase increment to a running total.

Components. A and B phase increment registers, an adder, and a phase summing register.

Operation. The phase increments in the A/B registers determine the frequency of the output signal. In operation, the phase accumulator adds the phase increment in register A or B to the current address in the phase summing register to produce a new and larger address. This new address addresses the waveform RAMs and calls up another point further along on the waveform stored in the RAM.

For a fixed-frequency output signal, the phase engine holds a fixed value in one of the phase increment registers. This value, repeatedly added to the value in the phase summing register at the fixed rate of 10MHz, makes the summing register address the waveform RAMS in equal steps and therefore produces a fixed-frequency output. Large phase increments produce higher frequencies by making the phase summing register step through the RAM (at 10MHz) with fewer, but larger, steps. Lower phase increments produce lower frequencies by stepping through the RAM (at 10MHz) with more, but smaller, steps.

For a swept-frequency output signal, the phase accumulator loads the phase increment registers with a series of larger and larger phase increments as the sweep progresses. In step-by-step operation, the phase accumulator adds the address increment in register A to the total in the summing register while the phase engine simultaneously loads the next larger address increment into the B register. Then, the control logic switches the registers and adds the new increment in the B register to the total in the summing register while the phase engine loads the next value in the series into the A register. The rate of increase of the series determines the rate and linearity of the sweep.

Although the phase accumulator sends a 16-bit address to the RAMs, it accepts and adds 40-bit phase increment values to allow extremely precise frequency control.

The following table shows how the phase engine uses the  ${\tt A}$  and  ${\tt B}$  registers to produce the operating modes.

| TO IMPLEMENT THESE MODES:                                  | THE PHASE ENGINE LOADS:                                                                                           |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| All Main (Non-Sweeping) Modes (CONT/TRIG/GATE/BURST/PHSLK) | An unchanging value in one register.                                                                              |

| CONT/TRIG Frequency Sweep Modes (1-6)                      | A series of slowly incrementing values into alternating registers.                                                |

| Frequency-Shift-Keyed Modes<br>(7-8)                       | The base value in one register and the keyed value in the other register.                                         |

| Frequency Sequence Modes                                   | A series of values from an internal table into alternating registers.                                             |

| Frequency Modulation Modes (12, 29)                        | A series of values, each determined by<br>the voltage level of an external signal,<br>into alternating registers. |

# 2.5.2 Phase Engine Interface Circuit

Function. Lets the phase engine board control the phase accumulator board.

Operation. The phase engine controls the phase accumulator by sending bytes of data over the  $\Phi$ ENG bus. The phase engine interface circuit accepts these bytes and loads them into the appropriate registers. The registers determine the operating mode, the burst count, and the output frequency.

U4. Address decoder U4 selects the register to receive the data on the data bus (see figure 2-0, phase engine bus). To load a register, the phase engine first puts data and an address on the ΦENG bus, then strobes U4 with line FSTB/. The FSTB/ strobe causes the particular Y output selected by the address to strobe and clock the data bus data into the register controlled by that Y output. In addition to loading registers, three of U4's Y outputs also serve as control signals for the sync and control logic.

U5, U6. To make the phase accumulator board operate in a given mode, the phase engine loads various bit patterns in sweep mode latches U5 and U6. The latched outputs of U5 and U6 then make the sync and control logic generate the specific control signals required by the selected operating mode. Figure 2-0, sync and control logic, shows how the outputs of U5 and U6 affect the sync and control logic and contains a table that lists the bit pattern for each mode.

# 2.5.3 Control Processor Interface Circuit

$\underline{Function}$ . Accepts the hold-sweep, resume-sweep, and reset-status-line-IOST4/commands from the main  $\mu P$  board; returns the burst-complete response to it.

U2A. Flip-flop U2A converts the BURST END pulse into a held signal level so that the main  $\mu P$  does not have to monitor status line IOST4/ continuously. Selecting the [Main] BURST mode will pull D of U2A low and allow the BURST END pulse to set status line IOST4/ low. After the main  $\mu P$  has processed the burst-complete response, it resets U2A with the Y0 output of U3.

U2B. Flip-flop U2B converts the sweep hold/resume commands into a line level for the hold input circuit.

U3. Address decoder U3 converts the GPIO addresses into the sweep hold, sweep resume, and reset status line commands.

### 2.5.4 Hold Input Circuit

<u>Function</u>. Accepts all hold requests and sends a hold signal to the proper circuit.

| · · · · · · · · · · · · · · · · · · · |                            | HOLD INPUT CIRCU | JIT SIGNALS  |

|---------------------------------------|----------------------------|------------------|--------------|

| TYPE OF HOLD                          | SOURCE                     | INPUTS           | OUTPUTS      |

| Sweep Holds                           | GPIB Bus                   | μΡΗΟLD/ low      | 15D Out high |

| (Frequency                            | [ <u>Hold/Resume</u> ] Key | μΡΗOLD/ low      | 15D Out high |

| or Phase)                             | Hold Input Connector       | Hold Input low   | 15D Out high |

| Waveform Hold                         | Hold Input Connector       | Hold Input low   | 16A Q/ low   |

U15BC, U16A. NAND gates U15BC, flip-flop U16A, and HOLDEN determine the function of the <u>Hold Input</u> connector. HOLDEN low makes <u>Hold Input</u> hold frequency or phase sweeps by routing the hold signal through gate U15B to the phase engine. HOLDEN high makes <u>Hold Input</u> hold waveforms by allowing the hold signal to set Q/ of U16A low. ACCHOLD/ allows the phase engine board to apply a waveform hold.

U15D. Gate U15D accepts frequency and phase hold commands from either the main  $\mu P$  board or the <u>Hold Input</u> connector and sends them to the phase engine board.

U17B. Gate U17B either allows the  $\Phi$ ACCCLK clock line to run at 10MHz or holds it low, depending on the state of Q/ of U16A. If the clock runs, the system generates output waveforms point by point. Stopping the clock stops address generation and holds the waveform at the point reached when the hold was applied. Releasing the hold allows waveform generation to resume from the held point.

UllA, Ul7A. Buffers UllA and Ul7A put identical clock signals  $\Phi$ ACCCLK and BACCCLK on two lines for distribution to the mode, sync, and accumulator circuits. Fan-out limits prevent the use of just one clock line.

# 2.5.5 Mode Control Logic Circuit

$\underline{\text{Major Function}}$ : Generates the  $\Phi ACCCLR/$  signal for the phase accumulator.

Secondary Function: Generates the LΦOVFL, LΦOVFL/, and the SELINCLK signals for the other control circuits; accepts the CLEAR/ signal from the external sync logic circuit.

| SIGNAL        | FUNCTION                                                                                                                                                                  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ΦACCCLR/      | Clears the $\Phi$ summing register. Low stops generation of output waveforms; high allows generation of output waveforms.                                                 |

| ΦOVFL<br>σ. • | Positive going 0.1µsec pulse generated whenever the phase accumulator adder reaches the highest address supplied to the waveform RAM (360° point of the stored waveform). |

| LΦOVFL        | Positive-going 0.1 usec pulse formed by synchronizing <b>ΦOVFL</b> to <b>ΦACCCLK</b> . Used by the external sync logic.                                                   |

| LΦOVFL/       | Inverse of LΦOVFL. Used by the external sync logic.                                                                                                                       |

| SELINCLK      | Either ΦACCCLK or LΦOVFL, as selected by INCLK/. Used by the acc sync logic.                                                                                              |

| CLEAR/        | Allows the external sync logic or the phase engine to generate a $\Phi$ ACCCLR/ and clear the phase summing register.                                                     |

Operation. The phase engine sends the bit patterns shown in figure 2-0 (sync and control logic) to the phase accumulator to make the mode control logic generate the following five versions of  $\Phi$ ACCCLR/:

| MODE                                                       | ACTION OF ΦACCCLR/                                                                             |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------|

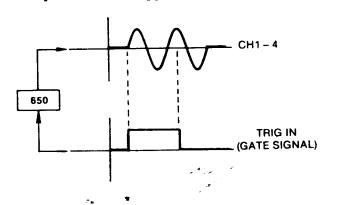

| [ <u>Main</u> ] CONT, PHSLK<br>[ <u>Sweep</u> ] Modes 1-29 | Stays high continuously (the phase engine handles triggered sweeps).                           |

| ( <u>Main</u> ) TRIG                                       | Steps high when TRIGGER steps high, then steps low on the next ΦOVFL.                          |

| [Main] A-GATE                                              | Steps high when TRIGGER steps high, then steps low when TRIGGER steps low.                     |

| [ <u>Main</u> ] S-GATE                                     | Steps high when TRIGGER steps high, then steps low on the first ΦOVFL after TRIGGER steps low. |

| [Main] BURST                                               | Steps high when TRIGGER steps high, then steps low when RCO (burst counter carry) steps low.   |

CONT, PHSLK, and All [Sweep] Modes. PACCCLR/ stays high continuously. Circuit Setup: CONT/ low holds flip-flop U13A cleared (Q/ output high) to block clearing of the phase summing register by the burst counter or flip-flop U7A. AGATE low disables gate U14B to prevent clearing of the phase summing register by the TRIGGER line. Operation: Holding  $\Phi ACCCLR/$  high allows the phase accumulator to run continuously and generate a continuous output waveform. The phase engine board handles triggering of the triggered sweep modes.

TRIG Mode. ΦACCCLR/ steps high when TRIGGER steps high, then steps low on the next  $\Phi$ OVFL. Circuit Setup: TGATE/ low (through U12C, U12B, and U13B) allows gate U14C to pass the output pulses of flip-flop U7A.

Operation: Stepping TRIGGER high clocks flip-flop U13A and sets output Q/ high. Rippling this high through gates U14D and U14A sets **\$\Phi\$ACCCLR**\$/ high and begins output waveform generation. When the waveform reaches the 360° point, ΦOVFL will shift high, causing flip-flop U7A to generate a high-going pulse. This pulse will pass through gate U14C and preset the Q/ output of flip-flop U13A low. Rippling this low through gates 14D and 14A sets ΦACCCLR/ low and stops output waveform generation.

A-GATE Mode. PACCCLR/ steps high when TRIGGER steps high, then steps low when TRIGGER steps low. Circuit Setup: AGATE high lets gate U14B pass the TRIGGER signal. Operation: A low TRIGGER prevents signal generation by holding PACCCLR/ low through U14B and U14A. Stepping TRIGGER high releases the  $\Phi$  summing register and begins waveform generation. Returning TRIGGER to low immediately clears the  $\Phi$ summing register and stops the output waveform in mid-cycle.

S-GATE Mode.  $\Phi$ ACCCLR/ steps high when TRIGGER steps high, then steps low on the first  $\Phi$ OVFL after TRIGGER steps low. Circuit Setup: SGATE high lets TRIGGER clear flip-flop U7A, and CONT/ high lets TRIGGER clock flip-flop U13A. Operation: Stepping TRIGGER high clocks flip-flop U13A and sets output Q/ high.

Rippling this high through gates U14D and U14A sets \$\PhiACCCLR/\) high and begins output waveform generation. Stepping TRIGGER low releases the clear on flip-flop U7A and enables \$\PhiACCCLK\$ to clock the next positive-going pulse of \$\PhiOVFL\$ through to Q of U7A. Gate U14C converts this positive-going pulse to a negative going pulse that resets Q/ of flip-flop U13A to low. Rippling this low through gates 14D and 14A sets \$\PhiACCCLR/\) low and stops the output waveform at its 360° point.

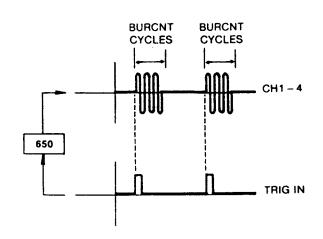

BURST Mode.  $\Phi$ ACCCLR/ steps high when TRIGGER steps high, then steps low when RCO (burst counter carry) steps low. Circuit Setup: BURST/ low lets L $\Phi$ OVFL clock the burst counter, TGATE/ high lets the burst counter clear flip-flop Ul3B, and CONT/ high lets flip-flop Ul3A accept TRIGGER signals.

The phase engine sets up the mode control logic for burst operation as follows: First, it puts 65535 minus the Burst Count on the  $\Phi$ ENG data bus (for a burst of 100 cycles, 65435 would appear on the bus). Second, it loads this modified burst count into the internal register of the burst counter by pulling line Y1 (BC/) low via the address bus. The modified burst count immediately transfers from the internal register to the counter register because **PACCCLR**/ holds CLOAD/ low between bursts. Finally, when the operator selects BURST from the main mode menu, the phase engine loads the burst bit pattern into the mode latches.

The mode control logic controls the burst as follows: With the TRIGGER line low, output Q/ of flip-flow U13A stays low and holds  $\Phi$ ACCCLR/ low through gates U14D and A. When TRIGGER steps high, Q/ of U13A steps high,  $\Phi$ ACCCLR/ steps high, and the phase accumulator starts running. Flip-flop U7B generates pulse L $\Phi$ OVFL at the end of each complete cycle of the output waveform. This pulse clocks input CCK of the burst counter, which begins counting up from the modified burst count loaded into its counter register. Output RCO/ steps low when the count reaches 65535 and back high when the count reaches 00000. RCO/ stepping low clears flip-flop U13B, which enables gate U14C. Flip-flop U7A produces pulses identical to the L $\Phi$ OVFL pulses from flip-flop U7B. When the L $\Phi$ OVFL pulse from U7B steps the count to 00000, the same pulse from U7A passes through gate U14C and presets flip-flop U13A. This sets Q/ low which, in turn, pulls  $\Phi$ ACCCLR/ low and stops generation of the output waveform.

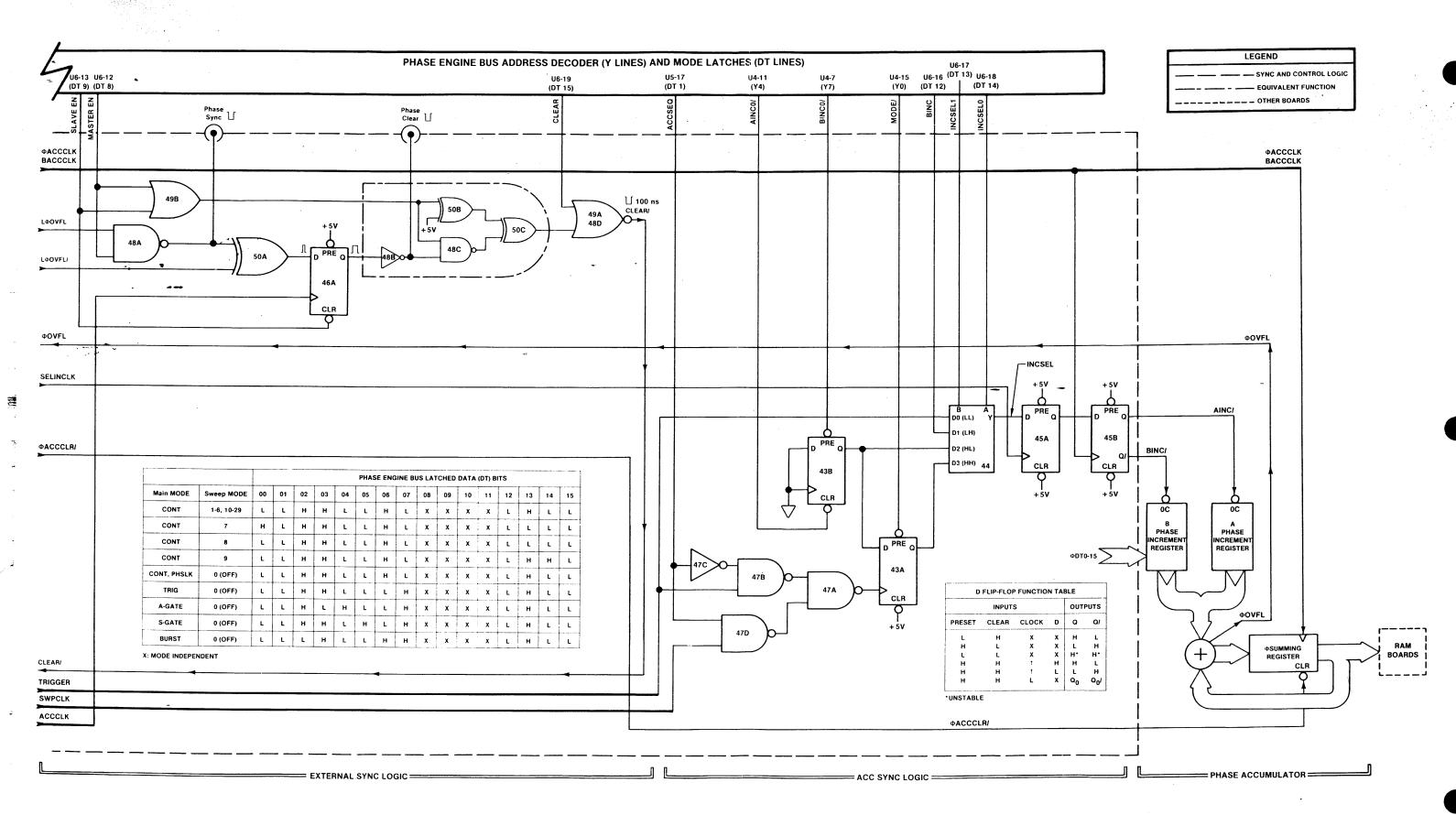

# 2.5.6 External Sync Logic Circuit

Function. Synchronizes the output waveforms of interconnected 650 units.

System Interconnection. The synchronized group consists of a master and several slaves. The <a href="Phase Clear">Phase Clear</a> connector of the master connects to the <a href="Phase Sync">Phase Sync</a> connector of the master connects to the <a href="Phase Sync">Phase Sync</a> connector of the master connectors of all the slaves. The <a href="10 MHz Ref">10 MHz Ref</a> connectors of all the slaves. The last slave has a 50 ohm termination at the <a href="10 MHz Ref">10 MHz Ref</a> input.

Unit Configuration. To determine the configuration of each 650, the operator selects INDEPN, MASTER, or SLAVE in the [Utility] CONFIG menu. The front panel sends the operator's choice over the optolink to the main  $\mu P$  board, the main  $\mu P$  sends it over the GPIB bus to the phase engine board, and the phase engine sends'it over the  $\Phi$ ENG data bus (as bits 8 and 9) to the phase accumulator board. Bits 8 and 9 appear at the output of the sweep mode latches as the MASTER EN and SLAVE EN lines.

System Operation. All units, whether master or slave, generate  $\Phi$ OVFL, a pulse that occurs each time the adder of the phase accumulator reaches the highest address in the address generation cycle. This address represents the end (or 360° point) of the waveforms stored in the RAM board RAMs.

The master 650 converts  $\Phi$ OVFL into a phase-sync pulse. The phase-sync pulse travels out <u>Phase Sync</u> of the master and into <u>Phase Sync</u> of all the slaves. Each slave compares the master phase-sync pulse to its internal sync pulse. If the pulses do not match, the slave generates a phase-clear pulse. The phase-clear pulse travels out <u>Phase Clear</u> of the out-of-sync slave and into <u>Phase Clear</u> of all the other slaves and the master. The phase-clear pulse resets the phase accumulator addresses of <u>all</u> units (master and slaves) to 0.

Unit Master Operation. Setup: MASTER EN line high, SLAVE EN line low.

Function 1: Generate phase-sync pulses for all the slaves. MASTER EN high allows NAND gate U48A to convert the L $\Phi$ OVFL signal into the phase-sync signal. Phase-sync consists of a series of negative-going 0.1  $\mu$ sec pulses. SLAVE EN low holds flip-flop U46A cleared (Q low) to keep the master-sync signal from passing through U50A, U46A, and U48B and out the Phase Clear connector.

Function 2: Accept a phase-clear pulse from any slave. MASTER EN high and SLAVE EN low makes OR gate 49B generate a high and enable the equivalent AND gate shown in dotted lines (U48BC, U50BC). This enables a phase-clear pulse from any slave to enter the <u>Phase Clear</u> connector and propagate through the gates to generate a CLEAR/ pulse and clear the master unit.

Unit Slave Operation. Setup: MASTER EN line low, SLAVE EN line high.

Function 1: Generate phase clear pulses. MASTER EN low holds the output of gate U48A continuously high so that exclusive-OR gate U50A can compare the phase-sync pulses from the master to the slave's internal LΦOVFL/ signal. If the signals don't match, a varying width pulse will appear at the output of gate U50A. Flip-flop U46A (enabled by SLAVE EN high) converts the mismatch pulse into a 0.1 µsec pulse. U48B converts this signal into a negative-going phase-clear pulse for this slave, all other slaves, and the master.

Function 2: Accept phase clear pulses. MASTER EN high and SLAVE EN low makes OR gate 49B generate a high and enable the equivalent AND gate shown in dotted lines (U48BC, U50BC). Enabling this gate allows a phase-clear pulse generated by this slave or any other slave to propagate through and clear this slave.

Unit Independent (Single-Unit) Operation. Setup: Both MASTER EN and STAVE EN low.

Function 1: Do not generate or accept phase-sync pulses. MASTER EN low disables gate U48A to stop generation of phase-sync pulses. SLAVE EN low holds  $flip_{\pi}flop$  U46A cleared to block acceptance of phase-sync signals.

Function 2: Do not generate or accept phase clear pulses. SLAVE EN low holds flip-flop U46A cleared to block generation of phase clear pulses. MASTER EN low and SLAVE EN low makes OR gate 49B generate a low. This signal disables the equivalent AND gate shown in dotted lines (U48BC, U50BC) and stops acceptance of phase clear pulses.

#### 2.5.7 Acc Sync Logic Circuit

<u>Function</u>: Generates the AINC/ and BINC/ signals for the phase increment registers of the phase accumulator.

Operation. The complementary AINC/ and BINC/ signals make the registers accept and deliver data as follows:

AINC/ Low Register A sends current data to the adder, while register B takes new data from the phase engine data bus.

AINC/ High Register A takes new data from the phase engine data bus, while BINC/ Low register B sends current data to the adder.

The components of the acc sync logic circuit perform the following functions:

U45B. Flip-flop U45B synchronizes register switching to the ΦACCCLK.

U45A. Flip-flop U45A synchronizes register switching to either the  $\Phi$ ACCCLK or the L $\Phi$ OVFL signal, as selected by the multiplexer formed by gates U8A-D. All modes except sweep mode 7, SYNC-FSK, use  $\Phi$ ACCCLK.

U44. Data selector U44 selects the signal that will control AINC/ and BINC/. The "active" register feeds data to the adder, while the "inactive" register can, if required by the mode, receive new data from the phase engine.

|              | T                 |                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INCSEL<br>10 | SELECTS<br>SIGNAL | IN ORDER TO                                                                                                                                                                                                                                                                                                                                                                                                                              |

| LL           | TRIGGER           | Make the TRIGGER signal select the active/inactive register. Modes: SYNC-FSK (7) and ASYNC-FSK (8).                                                                                                                                                                                                                                                                                                                                      |

| LH           | BINC              | Make the phase engine directly select the active/inactive register by setting line BINC.                                                                                                                                                                                                                                                                                                                                                 |

| HL           | 43B-Q             | Make the register currently receiving data from the phase engine send that data to the adder as soon as the phase engine finishes loading it. AINCO/ clearing Q to low says register A just received the last 16 bits of its 40-bit load; BINCO/ setting Q to high says B just received the last 16 bits of its 40-bit load.  Modes: All main and sweep modes use this signal except SYNC-FSK (7), ASYNC-FSK (8), and EXTR-SEQUENCE (9). |

| нн           | 43A-Q             | Make the register that last received data from the phase engine send that data to the adder, but not until directed to by the TRIGGER or SWPCLK signal, as selected by ACCSEQ and gates U47A-D.  Modes: EXTR-SEQUENCE (9). The ACCSEQ signal selects TRIGGER for mode 9.                                                                                                                                                                 |

Table 2-0. Signal Functions of the Phase Accumulator Board

| ACCHOLD/ | Sweep mode latch line 10. Allows the phase engine to hold the waveform by stopping the ΦACCCLK. Low applies hold; high releases it.                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACCCLK   | 10MHz system reference clock supplied by the ref/cal board.                                                                                                                                                                                                                              |

| ACCSEQ   | Sweep mode latch line 1. Allows the phase engine to choose either TRIGGER or SWPCLK as the signal that will cause the last-loaded phase increment register to send its data to the adder. ACCSEQ low chooses TRIGGER; high chooses SWPCLK.                                               |

| AGAC/    | Sweep mode latch line 3. Asynchronous gate asynchronous clear control line. The phase engine sets this line low for the main A-GATE mode so that TRIGGER can immediately clear the $\Phi$ summing register, rather than wait for the output waveform to reach 360°.                      |

| AGATE    | Sweep mode latch line 4. The phase engine sets this line high for the main A-GATE mode so that the TRIGGER signal can directly clear the $\Phi$ summing register.                                                                                                                        |

| AINC2/   | Output Y2 of the $\Phi$ ENG address bus decoder. Strobes the most significant 8 bits of the phase increment from the $\Phi$ ENG data bus into U33 of the A register.                                                                                                                     |

| AINC/    | Major control signal. Low directs the A phase increment register to send its stored phase increment to the adder.                                                                                                                                                                        |

| AINC1/   | Output Y3 of the $\Phi$ ENG address bus decoder. Strobes the middle 16 bits of the phase increment from the $\Phi$ ENG data bus into U38 and U28 of the A register.                                                                                                                      |

| AINCO/   | Output Y4 of the ΦENG address bus decoder. Two functions: 1) Strobes the least-significant 16 bits of the phase increment from the ΦENG data bus into U18 and U23 of the A register, and 2) tells the acc sync logic circuit that the phase engine has completed loading the A register. |

| BACCCLK  | Major control signal. Switched version of ACCCLK. This 10MHz clock synchronizes operation of the sync and control logic. Also called <b>PACCCLK</b> .                                                                                                                                    |

| BC/      | Output Y1 of the $\Phi$ ENG address bus decoder. Strobes the burst count on the $\Phi$ ENG data bus into the burst counter's internal register.                                                                                                                                          |

| BINC     | Sweep mode latch line 12. Allows the phase engine to directly select the phase increment register that will add its phase increment to the $\Phi$ summing register.                                                                                                                      |

Table 2-0. Signal Functions of the Phase Accumulator Board

| BINC/      | Major control signal. Low directs the B phase increment register to send its stored phase increment to the adder.                                                                                                                                                                        |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BINC2/     | Output Y5 of the ФENG address bus decoder. Strobes the most significant 8 bits of the phase increment from the ФENG data bus into U34 of the B register.                                                                                                                                 |

| BINC1/     | Output Y6 of the ФENG address bus decoder. Strobes the middle<br>16 bits of the phase increment from the ФENG data bus into U39<br>and U29 of the B register.                                                                                                                            |

| BINCO/     | Output Y7 of the ΦENG address bus decoder. Two functions: 1) Strobes the least-significant 16 bits of the phase increment from the ΦENG data bus into U19 and U24 of the B register, and 2) tells the acc sync logic circuit that the phase engine has completed loading the B register. |

| BURST/     | Sweep mode latch line 2. Low for main BURST mode operation. Allows the burst counter to count the number of complete output waveform cycles.                                                                                                                                             |

| BURSTCOMP/ | Board output signal line. The control processor interface sets this line low to tell the main µP that the phase accumulator has finished generating the requested number of output cycles.                                                                                               |

| CLEAR      | Sweep mode latch line 15. Allows the phase engine to clear the phase summing register as required. For example, the phase engine pulses this line high to clear the phase summing register when the operator changes from sweep mode 12 to 13, from 24 to 23, and from 1 to 0.           |

| CLEAR/     | Output of external sync logic circuit. Clears the phase summing register.                                                                                                                                                                                                                |

| CONT/      | Sweep mode latch line 7. Low for all the sweep modes and for the main CONT and PHSLK modes. Blocks generation of ΦACCCLR pulses so that the phase accumulator can run free.                                                                                                              |

| Hold In    | Rear-panel BNC input for sweep or waveform holds (see HOLDEN). Low applies, high releases the hold.                                                                                                                                                                                      |

| HOLDEN     | Sweep mode latch line 11. Allows the phase engine to select the function of the <u>Hold In</u> connector.                                                                                                                                                                                |

|            | [ <u>Utility</u> ] CONFIG WAVFM sets HOLDEN high for waveform hold, [ <u>Utility</u> ] CONFIG SWEEP sets HOLDEN low for sweep hold.                                                                                                                                                      |

. Table 2-0. Signal Functions of the Phase Accumulator Board

| HOLD REQ         | Board output signal line. The hold input circuit sends the hold request signal to the phase engine board. High requests the phase engine to hold the current frequency or phase sweep.                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INCLK/           | Sweep mode latch line 0. Chooses either \$\PhiACCCLK\$ or L\PhiOVFL as the signal that controls when the phase increment registers swap their add/load functions. The SYNC-FSK sweep mode uses L\PhiOVFL; all other main and sweep modes use \$\PhiACCCLK\$.                                                                                                                                                                                                                                                                                               |

| INSEL1<br>INSELO | Sweep mode latch lines 13 and 14. Allows the phase engine to select one of four phase increment register control lines. The control lines determine 1) which register will drive the adder while the other gets new data and 2) when the registers will swap functions. LL lets the TRIGGER line choose the adding register, LH lets the phase engine select the adding register with the BINC line, HL makes the most recently loaded register add immediately, and HH makes the most recently loaded register add when directed to by TRIGGER or SWPCLK. |

| LФOVFL           | Positive-going 0.1 $\mu$ sec pulse formed by synchronizing $\Phi$ OVFL to $\Phi$ ACCCLK. Used by the external sync logic.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MASTER EN        | Sweep mode latch line 8. Determines the function of the 650 in a group of synchronized units. MASTER EN high and SLAVE EN low makes the unit a master. Both lines low make it independent (single unit operation).                                                                                                                                                                                                                                                                                                                                         |

| μPHOLD/          | Internal output of control processor interface circuit. Low indicates a sweep hold request from the front panel or GPIB bus.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MODE/            | Output YO of the ФENG address bus decoder. Two functions: 1) Strobes the bits on the ФENG data bus into the sweep mode latches and 2) presets the Q output of flip-flop 43A to an initial state of 1.                                                                                                                                                                                                                                                                                                                                                      |

| <b>PACCCLK</b>   | Major control signal. Switched version of ACCCLK. This 10MHz clock synchronizes operation of the sync and control logic. Also called BACCCLK.                                                                                                                                                                                                                                                                                                                                                                                                              |

| ΦACCCLR/         | Major control signal. Clears the $\Phi$ summing register. Pulsing this line low clears the register; holding it low stops generation of output waveforms.                                                                                                                                                                                                                                                                                                                                                                                                  |

| ΦOVFL            | Major control signal. Positive-going 0.1µsec pulse generated whenever the phase accumulator adder reaches the highest address supplied to the waveform RAM (360° point of the stored waveform)                                                                                                                                                                                                                                                                                                                                                             |

• Table 2-0. Signal Functions of the Phase Accumulator Board

| Phase Sync  | Rear-panel BNC input/output. Synchronizes the output waveforms of interconnected 650 units. Consists of a series of 100 nsec negative-going pulses.                                                                                                                    |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase Clear | Rear-panel BNC input/output. Synchronizes the output waveforms of interconnected 650 units. 100 nsec negative-going pulse.                                                                                                                                             |

| SLAVE EN    | Sweep mode latch line 9. Determines the function of the 650 in a group of synchronized units. SLAVE EN high and MASTER EN low makes the unit a slave. Both lines low make it independent (single unit operation).                                                      |

| SWPCLK      | Input signal supplied by the ref/cal board. SWPCLK's frequency depends on sweep mode (1-29), sweep function (linear, log, sine, random), and sweep compensation (on or off). One cycle of SWPCLK                                                                       |

|             | takes slightly more time than the phase engine needs to calculate and load the next phase increment of the sweep.  Non-linear and compensated sweeps require more calculation time and therefore have lower SWPCLK frequencies than linear and non-compensated sweeps. |

| TGATE/      | Sweep mode latch line 6. The phase engine sets this line low to disable the burst counter for the main TRIG, A-GATE, and S-GATE modes.                                                                                                                                 |

| TRIGGER     | Input signal supplied by the ref/cal board. Controls the TRIG, A-GATE, S-GATE, and BURST modes. A TRIGGER signal can come from any of these sources: internal trigger generator, Trig In BNC connector, front panel [Manual Trigger] key, or the GPIB bus.             |

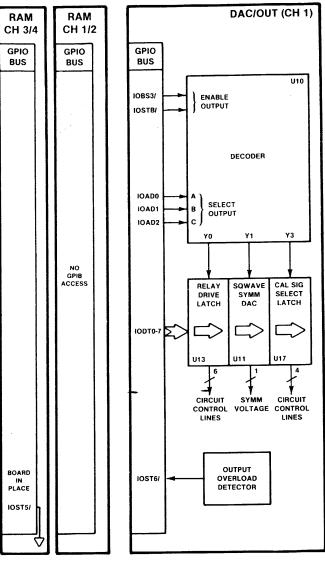

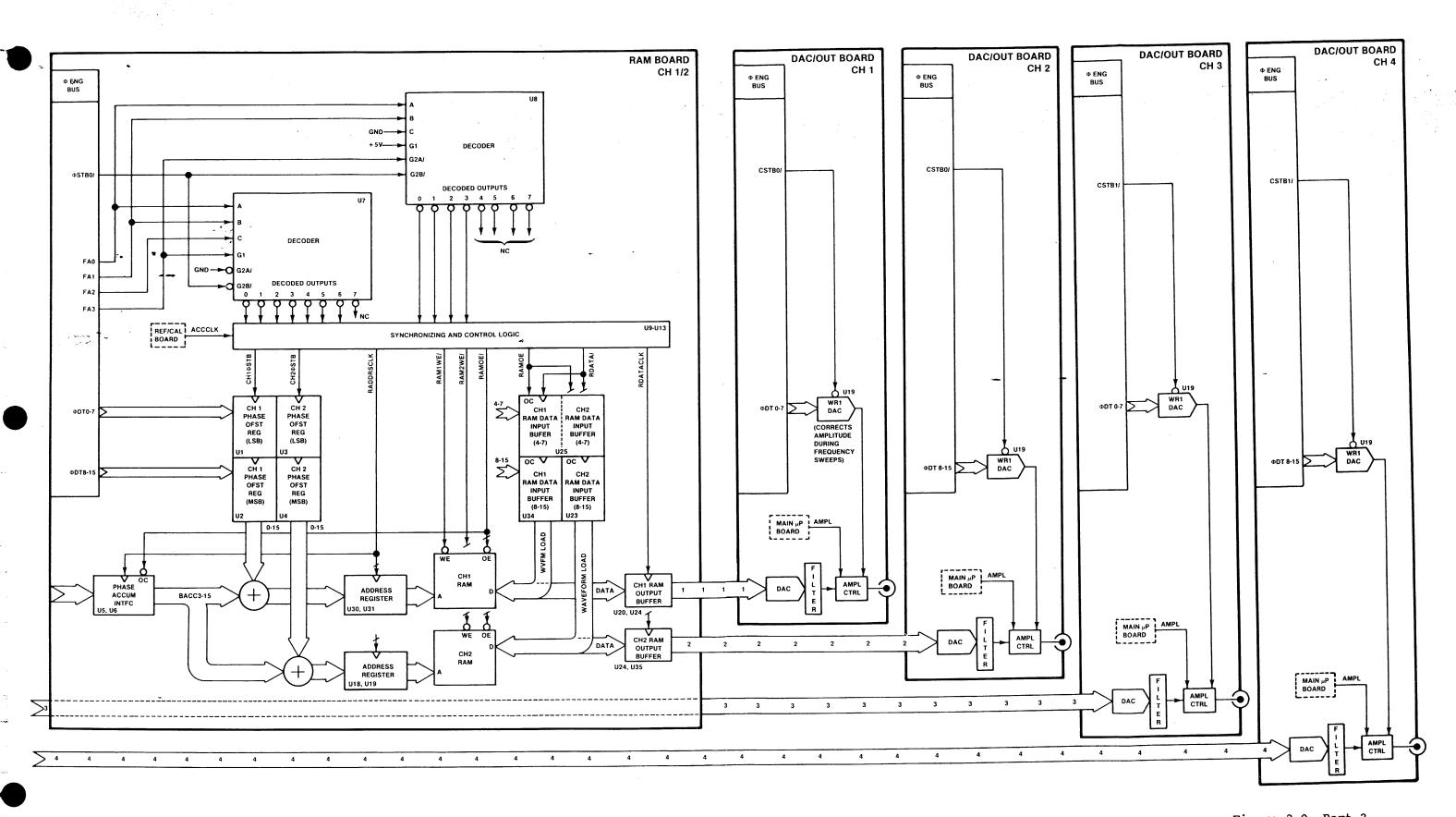

#### 2.6 RAM BOARD (1458)

Major Function. Stores the waveshape and controls the phase of two independent output channels.

|                                                             | Waveform RAM                                                                                         | 2.6.6                                              |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Generate Waveforms<br>Add Fixed Phase Offset<br>Sweep Phase | Control Logic Phase Accumulator Interface Phase Offset Register Adder Waveform RAM RAM Output Buffer | 2.6.1<br>2.6.3<br>2.6.5<br>2.6.4<br>2.6.6<br>2.6.7 |

| INFORMATION IN THIS SECTION |                                                                                          |                                 |  |

|-----------------------------|------------------------------------------------------------------------------------------|---------------------------------|--|

| INFORMATION                 | FUNCTION                                                                                 | LOCATION                        |  |

| Block Diagram               | Shows data flow, circuit control, and related boards.                                    | Figure 2-0                      |  |

| Circuit Description<br>Text | Individually describes the operation of each RAM board circuit.                          | Sections 2.6.1<br>through 2.6.7 |  |

| Signal Description<br>Table | Describes the function and action of each RAM board signal. Alphabetical by signal name. | Table 2-0                       |  |

|                 | INFORMATION IN OTHER SECTIONS                                                            |                           |

|-----------------|------------------------------------------------------------------------------------------|---------------------------|

| INFORMATION     | FUNCTION                                                                                 | LOCATION                  |

| ΦENG Bus Figure | Shows how the phase engine board controls the phase accumulator board over the ΦENG bus. | Figure 2-0 in section 2.4 |

THEORY OF OPERATION RAM BOARD

### 2.6.1 Control Logic Circuit

<u>Function</u>. Lets the phase engine control the data processing circuits of the RAM board.

Components. Address decoders U7 and U8, NAND gates U9 and U10, and flip-flops U11, U12, and U13.

U7, U8. Address decoders U7 and U8 form the phase engine interface. All the Y outputs of each decoder stay high. The phase engine pulses them low one at a time by placing an address on the ΦENG address bus, then strobing the ΦSTBO/ line of the bus low. The resulting pulse on the selected Y output either controls circuits directly through gates or indirectly through the D flip-flops.

U10A, UI0B. Gates U10A and U10B allow the phase engine to load a waveform into RAM1 (with the RAM1WRITE/ signal), into RAM2 (with the RAM2WRITE/ signal), or into both RAMs simultaneously (with the RAMWRITE/ signal). These signals strobe the waveform amplitudes byte by-byte from the RAM data input buffers into the waveform RAMs.

UllA. Flip-flop UllA allows the phase engine to turn RDATACLK off (to load waveforms), then back on (to generate output signals).

UllB. Flip-flop UllB allows the phase engine to control the RAM data bus. Signal RAMOE/ makes the RAM data bus either accept data from the data input buffers (load new waveform) or send data to the output buffers (generate output signals). Complimentary signal RAMOE disables the outputs of the data input buffers during output signal generation.

U9C, U10C. Gates U9C and U10C allow the phase engine to load a phase value into the channel 1 offset register (with the RAM10FST/ signal), into the channel 2 offset register (with the RAM20FST/signal), or into both RAMs simultaneously (with the RAM0FST/ signal). Flip-flops U12A, U12B, U13A, and U13B synchronize the loading with RADRSCLK.

# 2.6.2 RAM Data Input Buffer Circuit

<u>Function</u>. The RAM data input buffer lets the phase engine load sine, triangle, and ramp waveshapes into the waveform RAMs.

Components. D-Type flip-flops U23, U25, and U34.

Operation. The phase engine loads a waveform as a series of individual amplitude bytes, one for every addressable location in the RAM. To load one byte, the phase engine first latches that byte into the RAM data input buffers. Next, it loads the address of the RAM location that will store that byte into the phase offset register. Finally, it strobes the byte from the input buffer to the RAM.

The RAM data input buffer consists of 74ALS574 D-type edge-triggered flip-flops. Setting the OC/ line low makes the Q outputs deliver data to the

THEORY OF OPERATION RAM BOARD

RAM. Setting OC/ high makes the outputs assume the high-Z state. A positive-going clock pulse clocks the bit present at the D input to the corresponding Q output.

# 2.6.3 Phase Accumulator Interface Circuit

<u>Function</u>. Stores each address generated by the RAM board. This lets the RAM board generate the next address while the adder processes the old one.

Components. D-Type flip-flops U5 and U6.

Operation. During waveform generation, the phase accumulator interface reads the output of the phase accumulator board each time RADDRSCLK steps high. The output of the phase accumulator interface then remains fixed for use by the adder for the rest of the RADDRSCLK cycle. During waveform loading, RAMOE/pulls the OC/ line high to make the Q outputs assume the high-Z state. With the outputs high-Z, resistor networks RN1 and RN2 pull the adder input lines BACC3-15 high.

#### 2.6.4 Adder Circuit

<u>Function</u>. Adds the address in the phase offset register to the address in the phase accumulator and places the total in the RAM address register.

Components. U14-U17, U26-U29 (adder) and D-type flip-flops U18, U19, U30, U31 (RAM address register).

Operation. The adders continously sum their inputs and present the result at their outputs. The RAM address register reads the output of the adders each time RADDRSCLK steps high. The output of the RAM address register then remains fixed for use by the RAM memories for the rest of the RADDRSCLK cycle.

# 2.6.5 Phase Offset Register Circuit

<u>Function</u>. Lets the phase engine either give a fixed phase offset (such as 35°) to the channel output signal or phase sweep the channel output signal.

Components. D-type flip-flops U1 through U4.

Fixed Phase Operation. The operator specifies a fixed phase by pressing [Channel], then PHASE, then entering a phase in degrees. The phase engine applies this phase by loading a fixed address in the phase offset register, then repeatedly adding it to the addresses delivered by the phase accumulator.

Swept Phase Operation. The operator specifies a phase sweep by pressing [Sweep], then PHASE, then following the menus to specify the type of phase sweep and its parameters. To apply a phase sweep, the phase engine puts a new and larger address in the phase offset register before each add cycle, then adds this address to the next address from the phase accumulator board.

THEORY OF OPERATION RAM BOARD

#### 2.6.6 Waveform RAM Circuit

<u>Function</u>. Stores the waveshape of the channel's output signal. The RAM puts out 12-bit digital bytes that represent amplitudes along the stored waveform.

Components. U20 and U21 (channel 1 or 3), and U32 and U33 (channel 2 or 4).

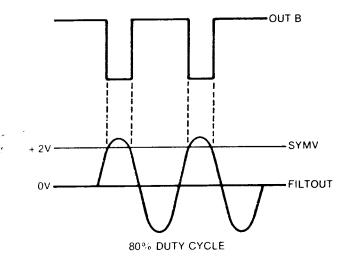

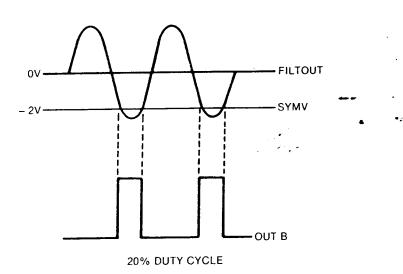

Operation. Each channel's RAM consists of two 8192-word x 8-bit CMOS chips that store the waveform as 12-bit amplitude values distributed across 8192 addresses. The phase engine loads sine, triangle, and ramp waveshapes in the waveform RAM. For square waves, the phase engine loads a sine in the RAM, then has the DAC/output board convert it to a square wave.

The RAM's OE/ line controls the mode of the data output line: L to read data out, H to write data in: Pulling the WE/ line low writes data into the currently addressed word.

#### 2.6.7 RAM Output Buffer Circuit

<u>Function</u>. Stores each digital amplitude called from the RAM memories. This lets the control logic call the next amplitude from the RAMs while the DAC/output board processes the old one.

Components. D-type flip-flops U22, U24, U35.

Operation. RDATACLK clocks the values through at 10MHz.