# COS/MOS Integrated Circuits Manual

# COS/MOS Integrated Circuits Manual

COS/MOS (Complementary-Symmetry Metal-Oxide Semiconductor) devices were developed at the RCA David Sarnoff Research Laboratories in Princeton, New Jersey, in the early 1960's. The first commercial series of integrated COS/MOS circuits was announced by the RCA Solid State Division in 1968.

COS/MOS made possible orders-of-magnitude reduction in the power consumption of digital logic circuits. Perhaps the most dramatic demonstration of the potential of this new technology was the development, in 1970, of a totally new consumer product the digital wrist watch. Battery-powered and quartz-crystal-controlled, this watch was an achievement in accuracy and compactness made possible only by COS/MOS integrated-circuit technology.

Today, the original series of COS/MOS integrated circuits has been expanded with increasingly complex designs, so that virtually any digital logic system can be implemented with commercially available packaged units. This Manual is intended as a guide to COS/MOS integrated circuits for the systems engineer and logic designer. It discusses the basic principles involved in the design and application of COS/MOS digital integrated circuits, and describes many of the circuit building blocks, ranging from basic NOR and NAND gates to complex phase-locked loops and rate multipliers.

Although this Manual is intended primarily for circuit and system designers working with solid-state circuits, it will also be useful to educators, students, radio amateurs, hobbyists, and others interested in the use of semiconductor devices and circuits.

#### **Contents**

|       | Pa                                                                                                                                                                                                                                                                                                              | ıge          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| l.    | COS/MOS Integrated Circuit Fundamentals                                                                                                                                                                                                                                                                         | . <b>.</b> 3 |

|       | Basic MOS transistors, complementary symmetry                                                                                                                                                                                                                                                                   | _            |

| II.   | Basic Circuit Building Blocks                                                                                                                                                                                                                                                                                   | 6            |

|       | Inverters, gates, transmission gates, flip-flops, shift registers, memory cells                                                                                                                                                                                                                                 |              |

| III.  | Characteristics of RCA COS/MOS Devices                                                                                                                                                                                                                                                                          | . 17         |

|       | Features of COS/MOS B-series types, A-series characteristics, B-series characteristics, packages, maximum ratings and recommended operating conditions, extra-value and MIL types                                                                                                                               |              |

| IV.   | Handling and Operating Considerations                                                                                                                                                                                                                                                                           | . 27         |

|       | Handling COS/MOS devices, built-in protection networks, operating precautions, voltage and dissipation considerations, noise immunity and noise margin, voltage logic-level definitions, input considerations, output considerations, power-supply considerations. clock requirements, cascading considerations |              |

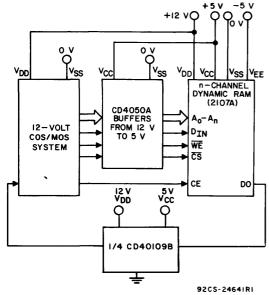

| ٧.    | Interfacing COS/MOS                                                                                                                                                                                                                                                                                             | . 36         |

|       | Positive/negative logic conversion, interfacing with p-channel MOS, interfacing with n-channel MOS, interfacing with saturated bipolar logic, COS/MOS and TTL. COS/MOS and HNIL, COS/MOS and DTL, COS/MOS and ECL, interfacing discrete and electromechanical devices, interfacing op-amps to COS/MOS           |              |

| VI.   | Astable and Monostable Multivibrators                                                                                                                                                                                                                                                                           | . 47         |

|       | Astable circuits, monostable circuits, COS/MOS integrated one-shots, Schmitt-trigger multivibrator circuits                                                                                                                                                                                                     |              |

| VII.  |                                                                                                                                                                                                                                                                                                                 | . 57         |

|       | Basic oscillator design considerations, practical oscillator-circuits                                                                                                                                                                                                                                           |              |

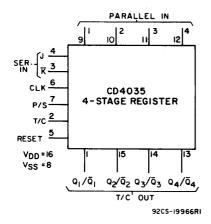

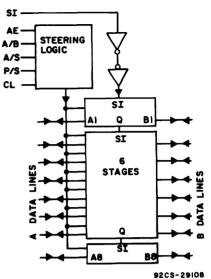

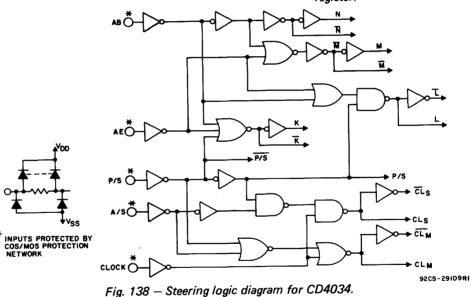

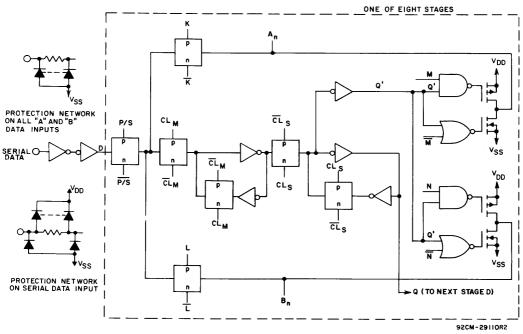

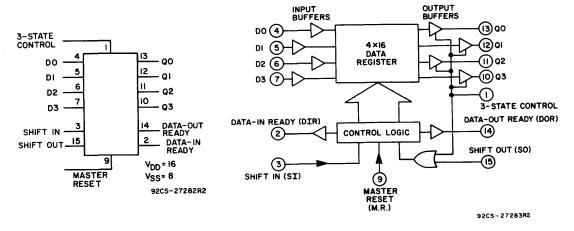

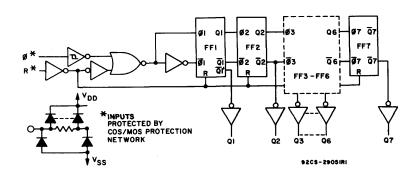

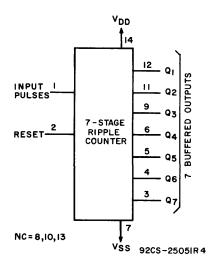

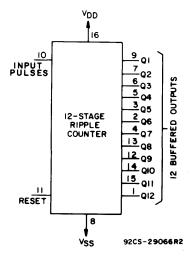

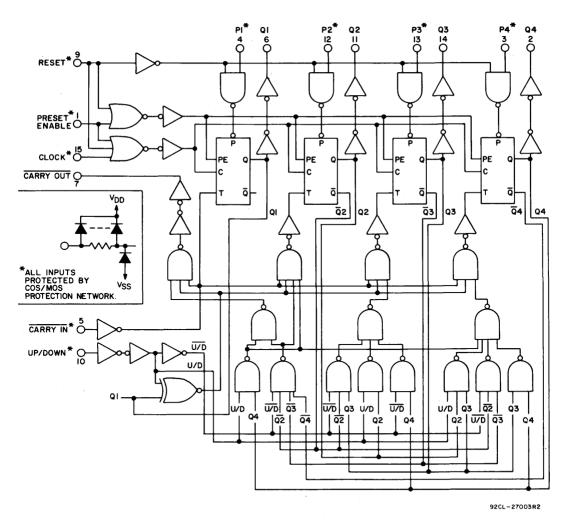

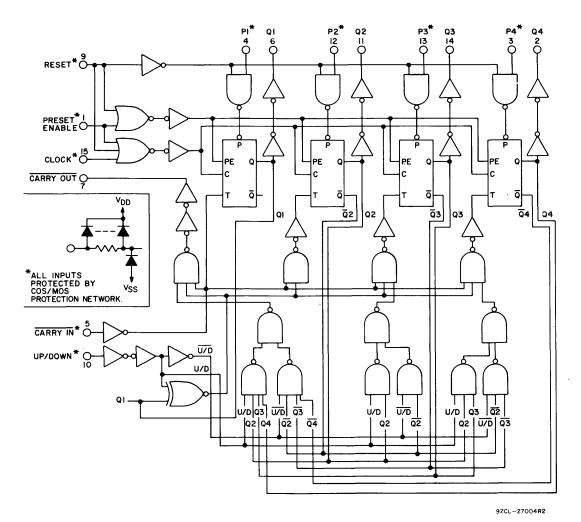

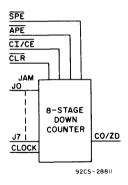

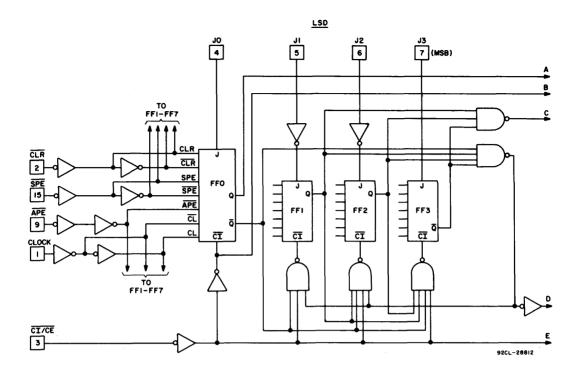

| VIII. | Shift Registers and Counters                                                                                                                                                                                                                                                                                    | . 65         |

|       | Static shift registers, dynamic shift registers, storage registers, FIFO buffer register, binary ripple-carry counters, clock timer, synchronous counters                                                                                                                                                       |              |

| IX.   | Display Drivers                                                                                                                                                                                                                                                                                                 | 104          |

|       | Liquid-crystal displays. light-emitting diode displays                                                                                                                                                                                                                                                          |              |

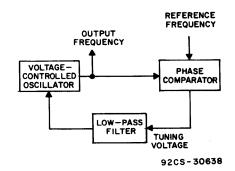

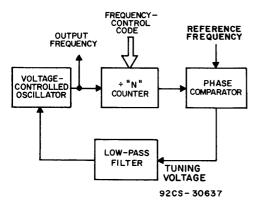

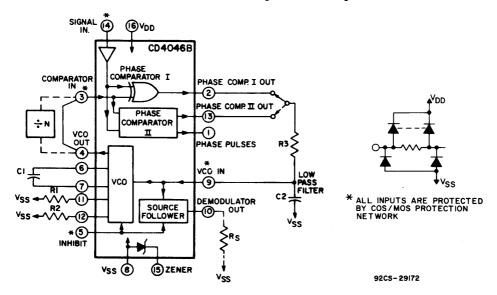

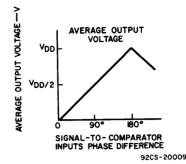

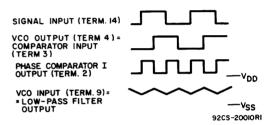

| X.    | Frequency synthesizers                                                                                                                                                                                                                                                                                          | 109          |

|       | Phase-locked loop, programmable divide-by-N counter, rate multipliers                                                                                                                                                                                                                                           | 400          |

| XI.   | Introduction to Microprocessors and Memory Interfacing                                                                                                                                                                                                                                                          | 122          |

|       | COSMAC microprocessor internal structure, operation and interfacing                                                                                                                                                                                                                                             | 422          |

| XII.  | Circuits and Applications                                                                                                                                                                                                                                                                                       | 153          |

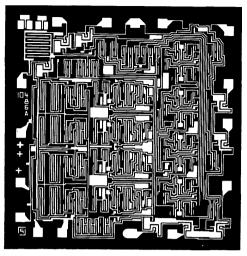

| XIII. | Custom LSI Design                                                                                                                                                                                                                                                                                               | 101          |

|       | MOS design parameters, fabrication of COS/MOS integrated circuits, custom designs                                                                                                                                                                                                                               | 165          |

|       | Index                                                                                                                                                                                                                                                                                                           | 100          |

Information furnished by RCA is believed to be accurate and reliable. However, no responsibility is assumed by RCA for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of RCA.

$\operatorname{Trademark(s)}^{igotimes}\operatorname{Registered}$  Marca(s) Registrada(s)

Copyright 1979 by RCA Corporation (All rights reserved under Pan-American Copyright Convention)

Printed in USA/1-79

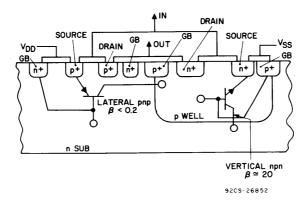

# I. COS/MOS Integrated Circuit Fundamentals

COS/MOS (Complementary-Symmetry MOS) integrated circuits provide a number of significant advantages as compared to integrated circuits using bipolar or single-MOS (PMOS channel or NMOS) technology. These advantages include ultralow power dissipation (microwatt level), high noise immunity (30 percent of supply voltage), and the use of a single power supply with a wide operating-voltage range (the recommended range is 3 to 18 volts; the maximum rating for B-series devices is 3 to 20 volts).

COS/MOS devices are voltage-controlled switches that have a high input impedance. They differ in both fabrication and operation from bipolar transistors, which are low-impedance current-switched devices. Although more devices are required to implement logic in COS/MOS than in single-channel MOS, COS/MOS circuits operate faster and require only a single 'clock' or control signal.

#### **BASIC MOS TRANSISTORS**

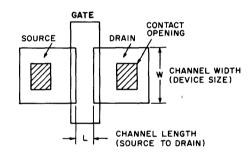

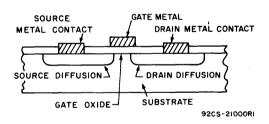

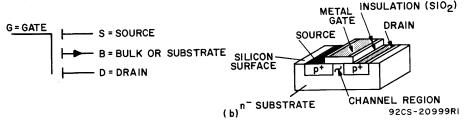

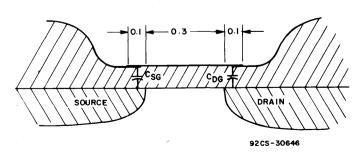

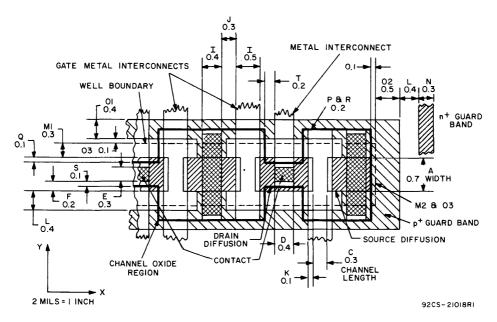

Every MOS transistor has three basic parts: the gate, the source diffusion, and the drain diffusion, as shown in Fig. 1. The gate acts as a control electrode to increase or decrease conduction in the channel between the source and drain diffusions.

All MOS transistors used in COS/MOS integrated circuits are enhancement-mode types. In this type, the transistors remain in the "off" state with a bias of zero volts from gate to source. To turn the transistors "on", conduction must be "enhanced" by ap-

plication of a bias voltage of the proper polarity to the gate electrode.

There are two types of MOS transistors: n-channel (electron conduction) and p-channel ("hole" conduction).

Fig. 1 — Cross-section views of a typical MOS transistor.

#### **N-Channel Types**

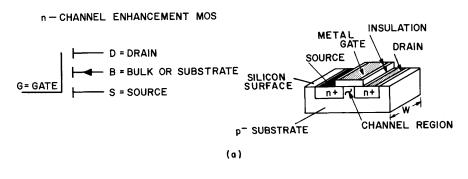

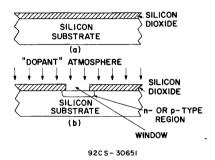

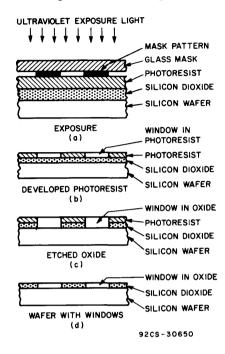

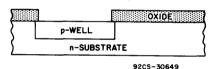

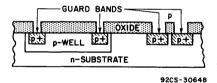

In n-channel MOS transistors, two heavily doped n<sup>+</sup> diffusions (source and drain) are closely spaced in a lightly doped p<sup>-</sup> silicon substrate, as shown in Fig. 2(a). The metal gate is located on top of a thin insulating layer of silicon dioxide (SiO<sub>2</sub>) directly over the channel between the diffusions.

During operation of an n-channel type, the source diffusion is connected to the substrate,

p-CHANNEL ENHANCEMENT MOS

Fig. 2 — Structure of enhancement-type MOS transistors: (a) n-channel type; (b) p-channel type.

which is at the most negative potential (-V<sub>SS</sub>). The drain diffusion is the output of the device. The impedance between the two diffusions is very high because it is the combination of back-biased diodes and the high resistance of the lightly doped substrate.

When a positive gate-to-source potential is applied, however, electrons are attracted to the channel along the surface of the silicon and form an ohmic path between the source and drain diffusions. (This action is capacitive, and no current flows through the gate electrode.)

#### P-Channel Types

In p-channel MOS transistors, the structure is similar, but the source and drain diffusions are heavily doped p<sup>+</sup> in a lightly doped n substrate, as shown in Fig. 2(b). In operation, the source is again connected to the substrate, which in this case is at the most positive potential (+V<sub>DD</sub>), and the drain diffusion is the output of the device. When the gate-to-source potential is zero, the device is off and the impedance between the two diffusions is very high.

When a negative potential is applied between the gate and the source, however, positive electrical charges ("holes") are attracted to the channel along the surface of the silicon, establishing a low-resistance path.

#### **Threshold Voltage**

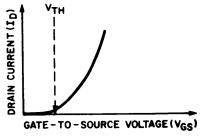

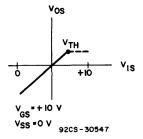

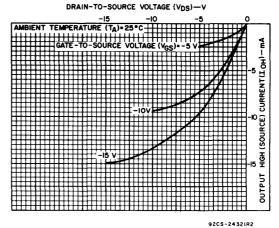

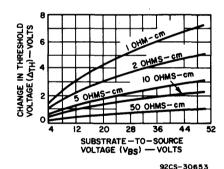

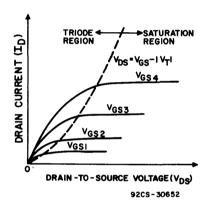

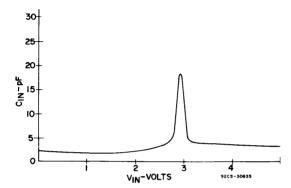

In both n-channel and p-channel MOS enhancement-mode devices, no current flows when the gate-to-source potential is zero. As the potential difference is increased (positive for n-channel, negative for p-channel devices), conduction starts at a point defined as the "threshold voltage" (typically 1.5 volts for both types of devices). Increasing the potential difference increases the current (i.e., reduces the drain-to-source impedance), as shown in Fig. 3. In digital

92CS-30617

Fig. 3 — Drain current as a function of gate-tosource voltage in an MOS transistor.

operations, the voltages applied to the gates to turn transistors on are normally at the "supply rails", or the maximum levels in the system. The positive supply +V<sub>DD</sub> is used for n-channel conduction and the negative supply -V<sub>SS</sub> for p-channel conduction.

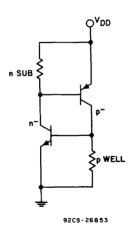

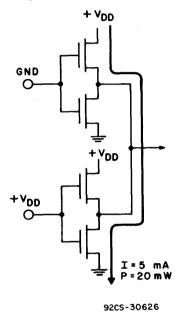

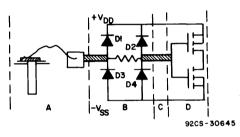

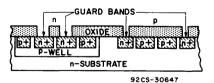

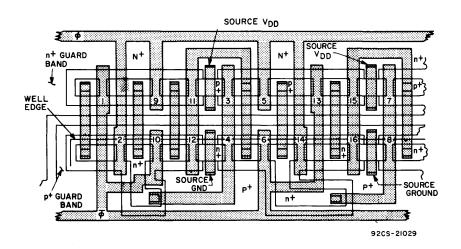

#### **COMPLEMENTARY SYMMETRY**

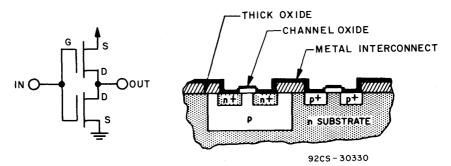

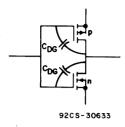

Because n-channel and p-channel transistors have diffusions with opposite polarity dopings, they operate with voltages of opposite polarity. That is, a positive voltage turns an n-channel device on and a p-channel device off; a negative voltage turns a p-channel device on and an n-channel device off. In COS/MOS integrated circuits, both p-and n-channel transistors are fabricated in the same semiconductor wafer, with metal connections between the paired inputs (gates) and outputs (drains), as shown in Fig. 4.

Because the gate of a COS/MOS device is essentially a capacitor (the gate metal and the substrate are the two plates, and the SiO<sub>2</sub> is the dielectric), there is no input current. When the output of one COS/MOS device drives the capacitive input of another, therefore, no IR drop occurs in the drain as a result of input current, and the output voltages are at full VDD and VSS levels.

Because the gates of the p-channel and n-channel pair are connected, one device must always be off regardless of the polarity of the signal on the gate. Therefore, there is never a direct path from supply to ground, and the only current from VDD to VSS is the very small leakage current of the MOS device that is off

(More detailed information on device characteristics, wafer processing, and custom IC layout design is given in Chapter XIII Custom LSI Design.)

Fig. 4 — Complementary-symmetry structure used in COS/MOS integrated circuits.

### **II. Basic Circuit Building Blocks**

This chapter describes the building-block units that form the basis for the more complex circuits discussed in the following chapters. These basic building blocks include inverters, gates, transmission gates, flipflops, shift registers, counters, and memory cells.

#### **INVERTERS**

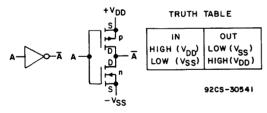

The n- and p-channel combination shown in Fig. 4 of the previous chapter is the inverter, the most fundamental of COS/MOS circuits. Fig. 5 shows its logic representation, simplified schematic, and truth table.

Fig. 5 — Logic diagram, simplified schematic, and truth table for a COS/MOS inverter.

A high (or positive) voltage ( $+V_{DD}$ ) on the gate electrode turns the n-channel device on and the p-channel device off, and the output is switched to its low level ( $-V_{SS}$ ). Similarly, a low (or negative) voltage ( $-V_{SS}$ ) on the gate turns the p-channel device on and the n-channel device off, and the output is switched to its high level ( $+V_{DD}$ ).

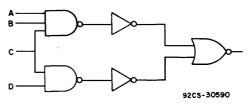

#### **GATES**

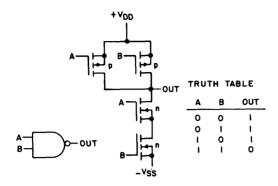

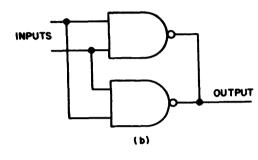

Each input to a COS/MOS gate requires a pchannel and n-channel device. In the NOR gate, the p-channel devices of the two inputs are connected in series and the n-channel devices in parallel, as shown in Fig. 6. A high

Fig. 6 — Logic diagram, simplified schematic, and truth table for a COS/MOS NOR gate.

level  $(+V_{DD})$  at either input (A or B) turns the corresponding p-channel device off and n-channel device on, and the output switches to a low level  $(-V_{SS})$ . Both input signals (A and B) must be low in order to turn both p-channel devices on and both n-channel devices off to switch the output to a high level  $(+V_{DD})$ .

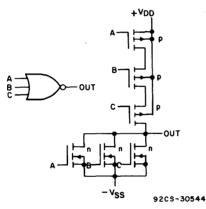

In the NAND gate, the n-channel devices are connected in series and the p-channel devices in parallel, as shown in Fig. 7. A low level (-V<sub>SS</sub>) at either input (A or B) turns the corresponding n-channel device off and p-channel device on, and switches the output to +V<sub>DD</sub>. Both inputs (A and B) must be high to turn both n-channel devices on and both p-channel devices off and switch the output to -V<sub>SS</sub>.

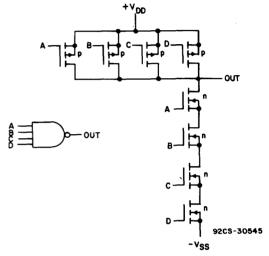

Larger gates can be made by adding additional inputs (but always with a p-

92CS-30543

Fig. 7 — Logic diagram, simplified schematic, and truth table for a COS/MOS NAND gate.

channel and n-channel device for each input). Figs. 8 and 9 show a three-input NOR gate and a four-input NAND gate.

Fig. 8 — Logic diagram, simplified schematic, and truth table for a 3-input NOR gate.

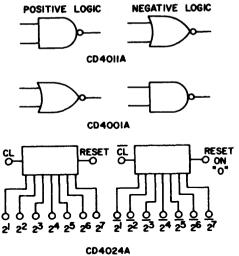

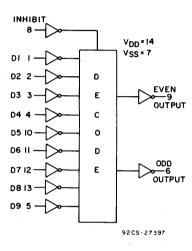

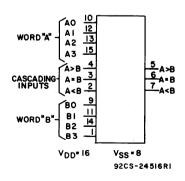

RCA COS/MOS gates are commercially available in a variety of configurations, as shown in Table I. (An OR gate is simply a NOR gate with an inverter added at the output; adding an inverter to a NAND gate provides the AND function.)

If all the inputs of a particular gate are not used in a circuit, the unused inputs cannot be allowed to "float". Otherwise, any static charge accumulating at the unused high-impedance input might cause the gate potential to rise to a level which turns on both the p-channel and the n-channel devices, resulting in excessive power dissipation. For

Fig. 9 — Logic diagram, simplified schematic, and truth table for a 4-input NAND gate.

example, if the eight-input CD4078 is used as a seven-input NOR gate, the unused input should be tied to  $-V_{SS}$  or to one of the active inputs to assure that all the p-channel devices will be on and all the n-channel devices off when all the active inputs are low. For a NAND gate, unused inputs must be tied to  $+V_{DD}$  or to an active input to assure that all n-channel devices will be on and all p-channel devices off when all active inputs are high.

Table I — Commercially Available RCA COS/MOS Gates

| Gate<br>Configuration      | NOR    | NAND   | OR     | AND    |

|----------------------------|--------|--------|--------|--------|

| Quad 2-input               | CD4001 | CD4011 | CD4071 | CD4081 |

| Triple 3-input             | CD4025 | CD4023 | CD4075 | CD4073 |

| Dual 4-input               | CD4002 | CD4012 | CD4072 | CD4082 |

| Dual 3-input plus inverter | CD4000 |        |        |        |

| Single 8-input             | CD4078 | CD4068 |        |        |

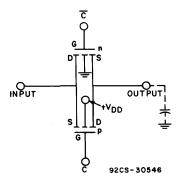

#### TRANSMISSION GATES

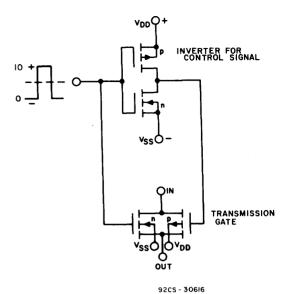

A perfect switch is characterized by zero resistance in both the forward and reverse directions when closed and an infinite resistance in both directions when open. The COS/MOS transmission gate, with its low on-state impedance and high off-state impedance (approximately 100 megohms), is a voltage-controlled device which approaches the characteristics of the theoretical perfect switch. The transmission-gate circuit consists of an n-channel device and a p-channel device connected in parallel, as shown in Fig. 10; complementary voltages (C and  $\overline{C}$ ) are applied to the gate electrodes.

Fig. 10 - COS/MOS transmission gate.

The transmission gate provides an excellent example of how the complementary characteristics of a p-channel and n-channel pair exceed those of the individual devices. If the transmission gate were a single-channel device, it could not transmit signals over the full VDD - VSS voltage range. For example, assume that the supply voltage (VDD - VSS) is 10 volts, that the signal to be switched rises to 10 volts, and that the device used is an n-channel MOS transistor with a threshold voltage of 1.5 volts. As described in the previous chapter, conduction occurs when the gate-to-source potential exceeds the threshold voltage. With a gate signal of 10 volts and an input signal of zero, therefore, the n-channel device is on

$$(V_{\text{gate-source}} = 10 \cdot 0 = 10 \text{ V};$$

10 V > 1.5 V or the threshold voltage).

However, as the input signal rises to 8.5

volts, the gate-to-source potential drops to the threshold voltage

$$(V_{gate-source} = 10 - 8.5 = 1.5 V),$$

and the device no longer conducts. Thus, the full 10-volt excursion of the input signal cannot be transmitted, as shown in Fig. 11.

Fig. 11 — Switch characteristics of a single n-channel MOS transistor.

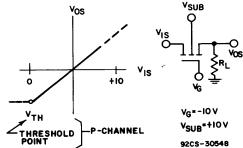

When a p-channel device is used in parallel with the n-channel device, and with a signal of the opposite polarity on its gate (i.e., zero volts), the p-channel is on when the input signal is 8.5 volts

$$(V_{\text{gate-source}} = 0 - 8.5 = -8.5 \text{ V};$$

-8.5 V > -1.5 V, or the threshold voltage).

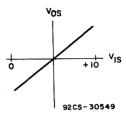

Fig. 12 shows the switch characteristics of a single p-channel device. As a result, the complementary switch does not turn off prematurely, and the full 10-volt input signal can be switched, as shown by the composite

LEGEND:

VIS = INPUT SIGNAL VOLTS

VOS = OUTPUT SIGNAL VOLTS

VG = GATE CONTROL VOLTS

VSUB = SUBSTRATE VOLTS

VOS

Fig. 12 — Switch characteristics of a single p-channel MOS transistor.

COS/MOS transmission-gate characteristics in Fig. 13.

Fig. 13 — Composite switch characteristics of a COS/MOS transmission gate.

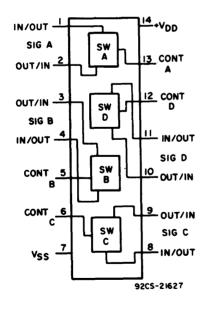

#### CD4016 Switch

The RCA COS/MOS CD4016 is a quad bilateral switch, or transmission gate. Each of the four independent transmission gates requires only a single control signal (an inverter is built in for each control line); i.e., both the p-channel and n-channel devices in a given switch are biased on or off simultaneously by the control signal. A functional diagram for the CD4016 is shown in Fig. 14. The schematic diagram for one of the four identical stages is given in Fig. 15.

Fig. 14 — Functional diagram for the CD4016 quad bilateral switch.

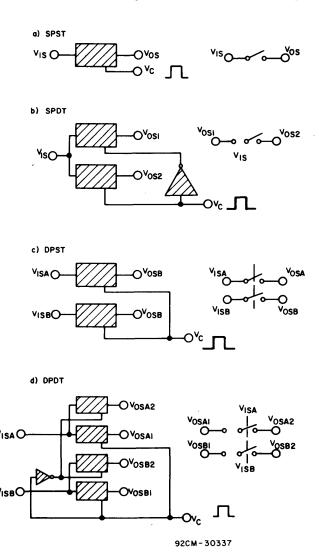

The CD4016 quad bilateral switch can be used to perform the four common switch

Fig. 15 — Schematic diagram for one of the four identical stages of the CD4016 guad bilateral switch.

functions (i.e., SPST, SPDT, DPST, and DPDT), as shown in Fig. 16.

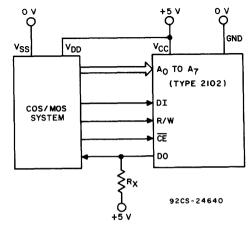

#### Three-State Logic (Common Busing)

Transmission gates and analog multiplexer/demultiplexer circuits are extremely useful in coupling and decoupling from a common bus line. Either high or low signals can be placed on the bus line; with both gates off, the transmission gate presents a very high impedance to the line. (More information on busing is given in Chapter XI Microprocessors and Memory Interfacing.)

#### FLIP-FLOPS

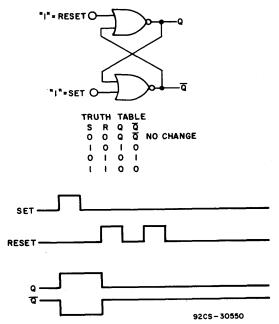

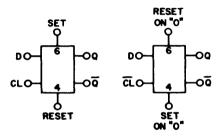

Three basic types of flip-flops can be configured in COS/MOS: R-S (Set-Reset), D-type (Master-Slave), and the J-K flip-flop.

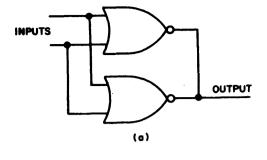

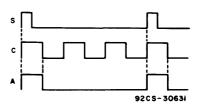

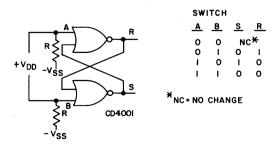

#### **Set-Reset Flip-Flops**

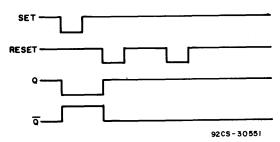

Two NOR gates may be connected as shown in Fig. 17 to form a set-reset flip-flop. When the set and reset inputs are low, one output is low and the other high, and there is a stable condition. If a positive pulse is applied to the

set input, its associated n-channel device is turned on; the  $\overline{Q}$  output then goes low and the Q output goes high. After the pulse period both inputs are again low, and the flip-flop is in another stable condition.

Applying a positive pulse to the reset input causes the Q output to go low and the  $\overline{Q}$

output to go high; after the pulse period both inputs are again low and the flip-flop is in the original stable condition. Additional positive pulses on the same input do not cause any change in the output, i.e., the pulses must be applied alternately to the inputs to change the condition of the flip-flop.

Fig. 16 — Basic switch functions using the CD4016 quad bilateral switch. a) Single-pole single-throw, b) Single-pole double throw, c) Double-pole single-throw, and d) Double-pole double-throw.

Fig. 17 — Logic diagram, truth table, and associated pulse shapes for a set-reset flip-flop using NOR gates.

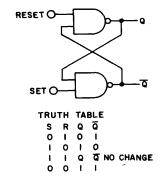

Two NAND gates may also be used to form a set-reset flip-flop, as shown in Fig. 18. In this configuration, negative-going pulses are used to switch the outputs.

Fig. 18 — Logic diagram, truth table, and associated pulse shapes for a setreset flip-flop using NAND gates.

#### D Flip-Flops

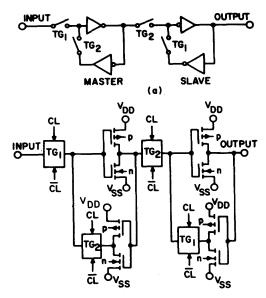

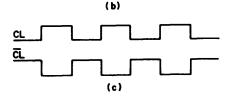

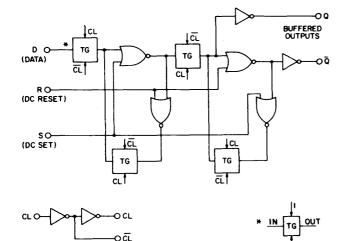

Fig. 19 shows the circuit for a D-type (Master-Slave) flip-flop. The block diagram shows a master flip-flop formed from two inverters and two transmission gates (shown as switches) that feed a slave flip-flop having a similar configuration. The transmission-gate control signal is called the "clock" because it controls the timing of the operations. When the clock is at a low level, the TG1 transmission gates are closed and the TG2 gates are open. This configuration allows the master flip-flop to sample incoming data, while the slave holds the data from the previous input and feeds it to the

ALL p-UNIT SUBSTRATES CONNECTED TO  ${\rm V}_{DD}$  ; all n-Unit substrates to  ${\rm V}_{SS}.$

92CS-30332

Fig. 19 — Logic diagram, simplified schematic, and clock-pulse diagrams for a D-type flip-flop.

output. When the clock is high, the TG1 transmission gates open and the TG2 gates close, so that the data is held in the master and fed to the slave.

The D-type flip-flop is static and holds its state indefinitely if no clock pulses are applied, i.e., it stores the state of the input prior to the last clocked input pulse. As shown in Fig. 19, both the clock (CL) and the inverted clock  $(\overline{CL})$  are required to control the transmission gates; clock inversion is accomplished by an inverter.

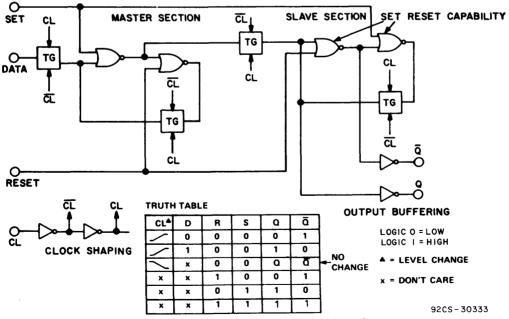

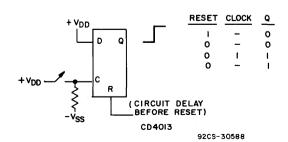

Set and reset capability are added to the D-type flip-flop by changing the inverters in the master and slave sections to NOR gates. Fig. 20 shows the logic diagram and truth table for a D-type flip-flop with set and reset capability. As shown in the truth table, a high on the reset input sets the Q output low; a high on the set input forces the Q output high.

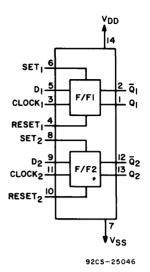

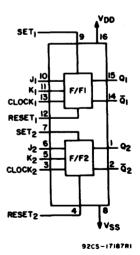

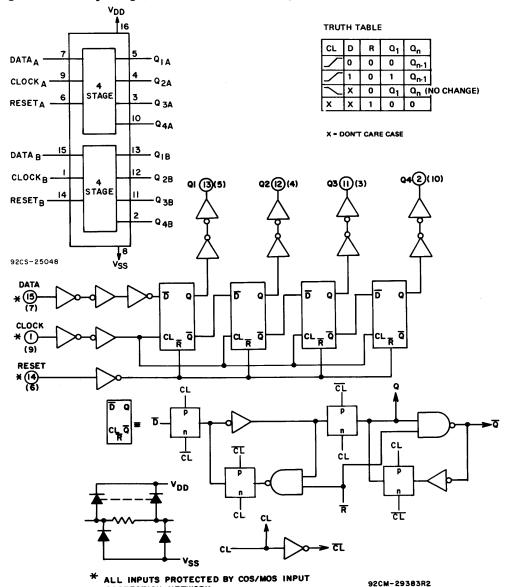

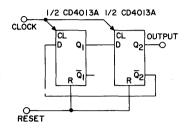

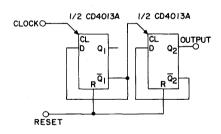

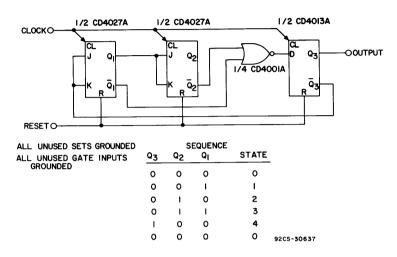

The RCA-CD4013 consists of two identical independent D-type flip-flops. Each flip-flop has independent data, set, reset, and clock inputs, and Q and  $\overline{Q}$  outputs, as shown in Fig. 21. The logic level present at the data (D) input is transferred to the Q output during the positive-going transition of the clock pulse. Setting or resetting is accomplished by a high level on the set or reset line, respectively. (If the set or reset inputs are not used, they must be tied low so the gate does not float.)

Fig. 21 — Functional diagram for CD4013 dual D flip-flop with set-reset capability.

#### J-K Flip-Flops

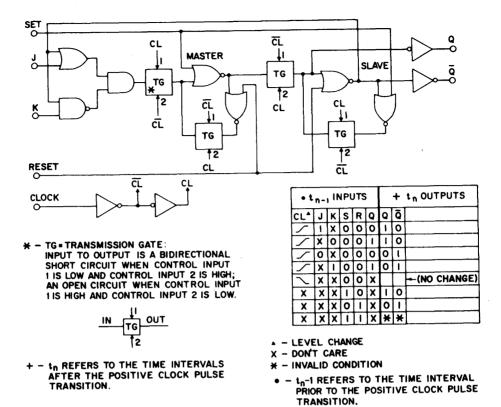

The logic diagram and truth table for a J-K flip-flop are shown in Fig. 22. The J-K flip-flop is similar to the D-type flip-flop, but has some additional circuitry to accommodate

Fig. 20 — Logic diagram and truth table for a D-type flip-flop with set-reset capability.

Fig. 22 — Logic diagram and truth table for a J-K flip-flop.

the J and K inputs. The J and K inputs provide separate clocked set and reset inputs, and allow the flip-flop to change state on successive clock pulses (this capability is known as the "toggle mode"). The J-K flip-flop circuit also has set and reset capability; the inverters in the master and slave flip-flop each have an added OR input for direct (unclocked) setting or resetting of the flip-flop.

The RCA-CD4027 is a single monolithic integrated circuit containing two identical independent J-K master-slave flip-flops, as shown in Fig. 23. Each flip-flop has provisions for individual J,K, set, reset, and clock input signals; buffered Q and  $\overline{Q}$  signals are provided as outputs.

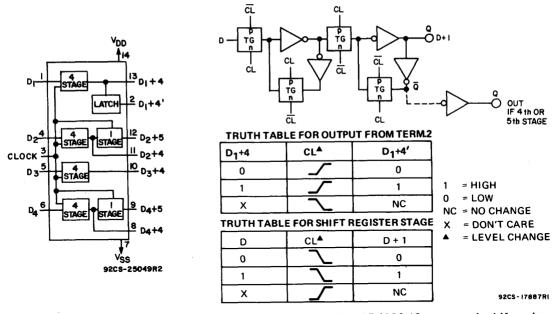

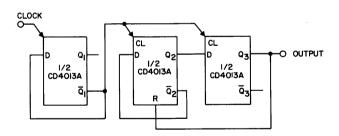

#### SHIFT REGISTERS

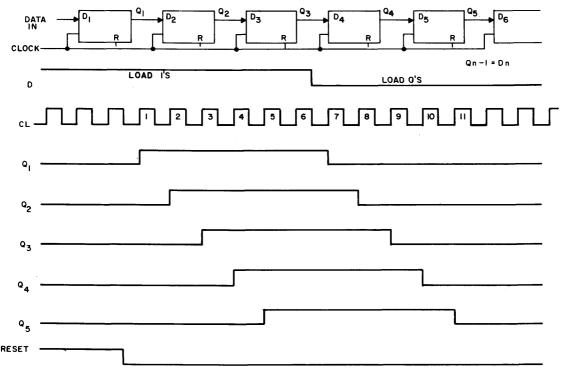

Shift registers are basically flip-flops (usually D-type) connected so that the Q output of

92CS-30336

Fig. 23 — Functional diagram for CD4027 dual J-K flip-flop with set-reset capability.

each stage becomes the D input of the following stage. The clock is common so that all shifting occurs synchronously.

#### Static Shift Registers

Fig. 24 shows a block diagram for a basic multi-stage static shift register and illustrates the associated pulse shapes. RCA provides a variety of static shift registers ranging from four stages (CD4015) to 64 stages (CD4031). (Additional information is given in Chapter VIII Shift Registers and Counters.)

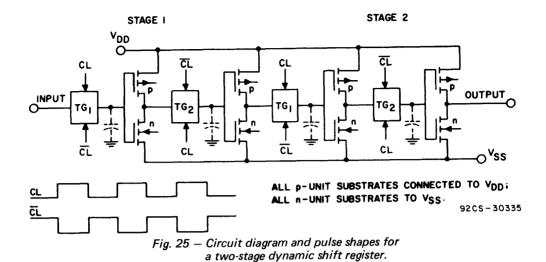

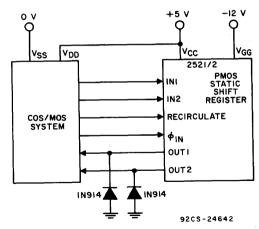

#### **Dynamic Shift Registers**

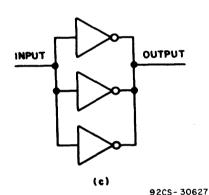

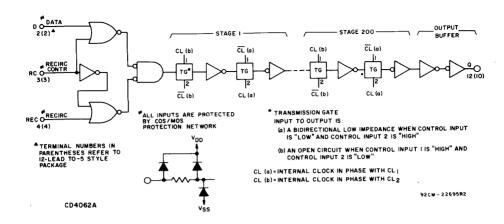

Fig. 25 shows the circuit diagram and clock-pulse diagram for a two-stage dynamic shift register; each stage consists of two inverters and two transmission gates. Each transmission gate is driven by two out-of-phase clock signals arranged so that when alternate transmission gates are turned on, the others are turned off. The shift register uses the input capacitance of the inverters for temporary storage of the signals. When the first transmission gate in each stage is turned on, it couples the signal from the previous stage

to the inverter. When the transmission gate is turned off on the next half-cycle of the clock, the signal is stored on the input capacitance to the inverter. The signal remains at the output of the inverter, where it is available to the next transmission gate, which is then turned on. Again, this signal is applied to the input of the next inverter where it is stored in the input capacitance of the inverter, making the signal available at the output of the stage. Thus, a signal progresses to the right by one-half stage on each half-cycle of the clock, or by one stage per clock cycle.

Because dynamic shift registers depend on stored charge, which is subject to slow decay, there is a minimum frequency at which they will operate; reliable operation can be expected at frequencies as low as 5 kHz.

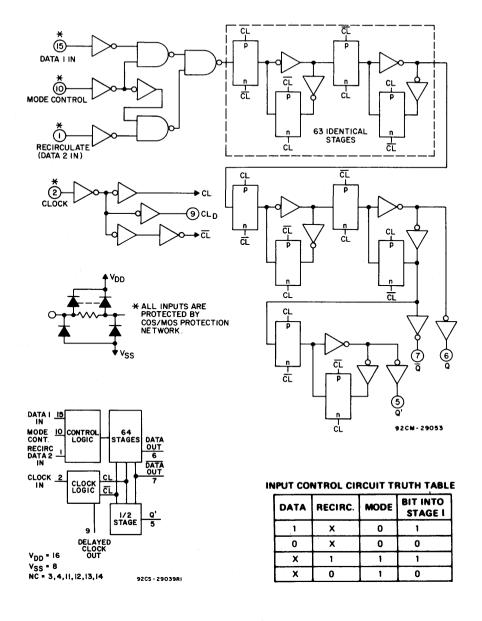

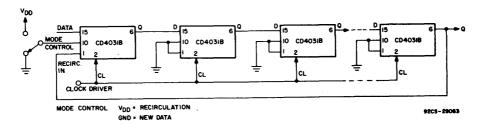

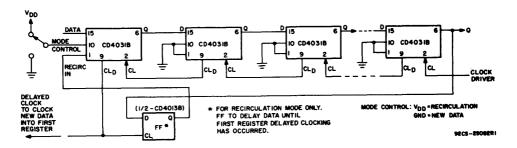

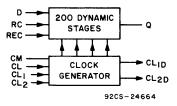

The RCA-CD4062 is a 200-bit dynamic shift register with recirculating capability, useful as a long serial memory or time-delay circuit. This circuit is described in Chapter VIII Shift Registers and Counters.

Fig. 24 – Block diagram and pulse shapes for a multi-stage static shift register.

92CM-30552

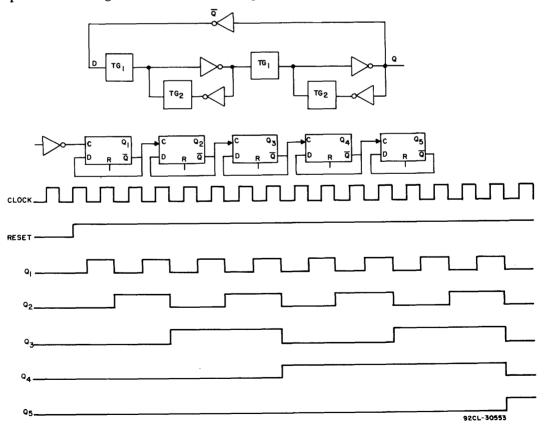

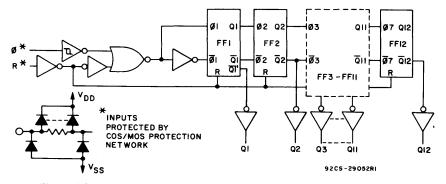

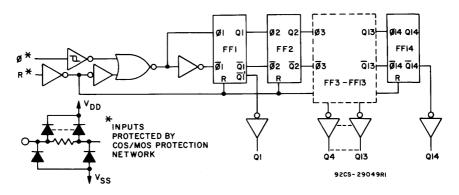

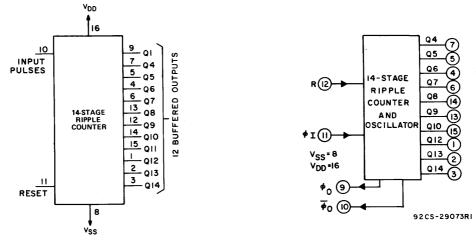

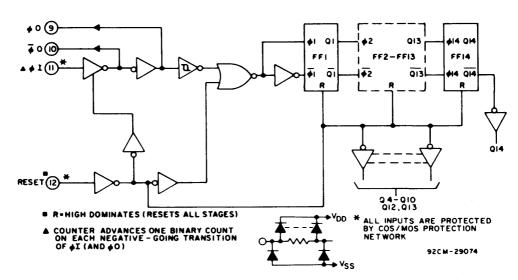

#### **COUNTERS**

Binary (divide-by-two per stage) counters are similar to shift registers except that the  $\frac{D}{Q}$  input to each stage is connected to the  $\frac{D}{Q}$

output of the stage. The Q and Q outputs of one stage become the Clock and Clock inputs of the following stage. Fig. 26 shows the logic diagram, block diagram, and associated pulse shapes for a five-stage binary counter.

Fig. 26 — Logic diagram, block diagram, and pulse shapes for a five-stage binary counter.

The counter is advanced one count on the negative-going transition of each input pulse.

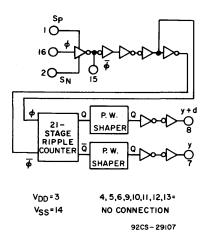

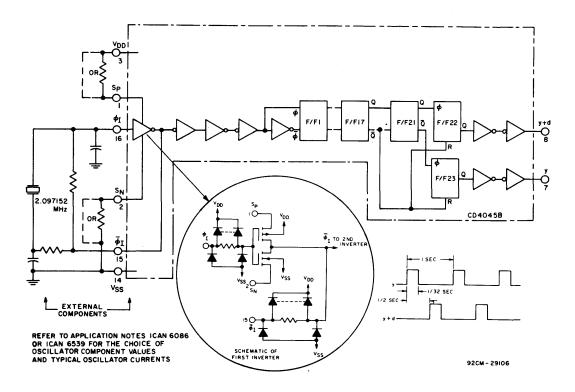

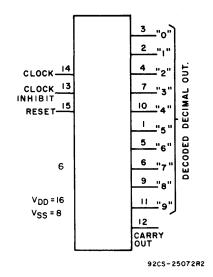

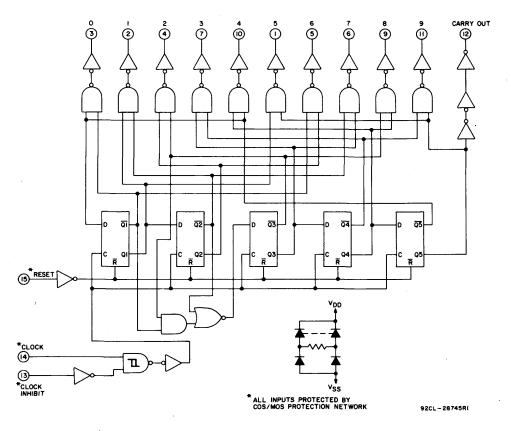

RCA provides a variety of binary counters ranging from seven stages (CD4024) to 21 stages (CD4045). These circuits are described in Chapter VIII Shift Registers and Counters.

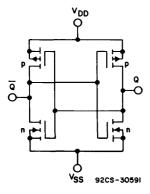

#### **MEMORY CELLS**

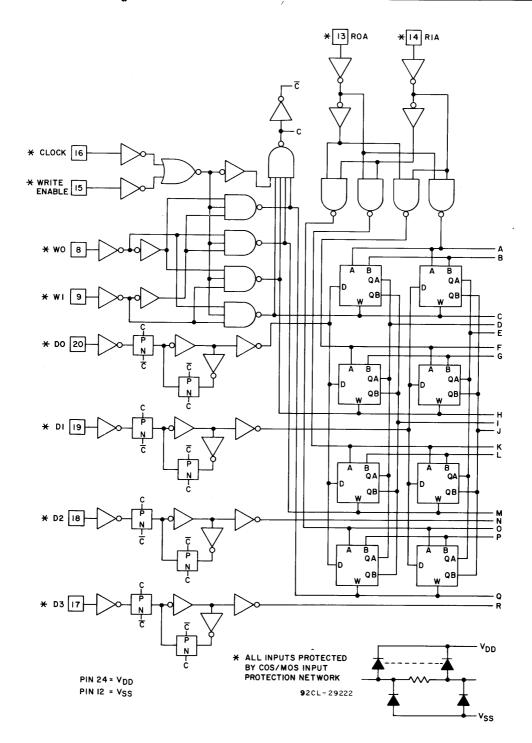

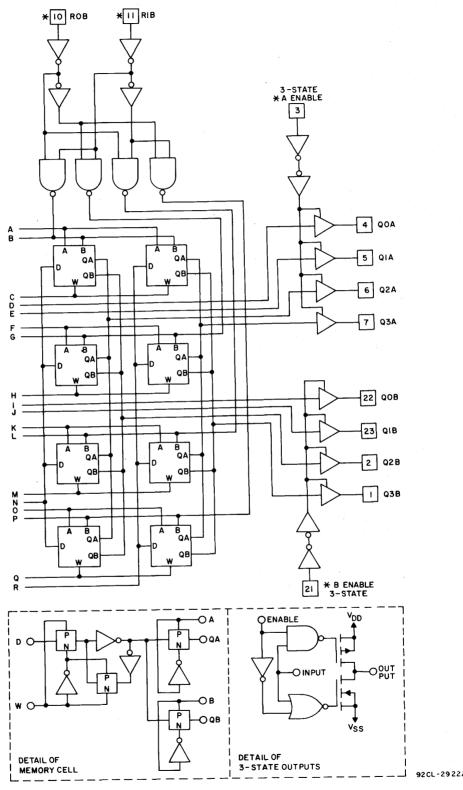

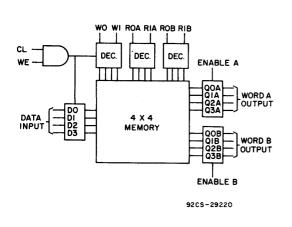

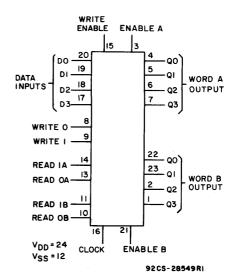

The basic storage element common to most RCA COS/MOS memories consists of two COS/MOS inverters cross-coupled to form a flip-flop, as shown in Fig. 27. Single-transistor transmission gates are used as a simple and efficient means of performing the logic functions associated with storage-cell selection (i.e., the sensing and storing operations).

Fig. 27 — Basic storage element of COS/MOS memories.

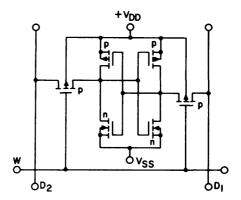

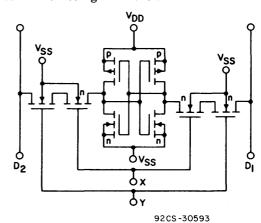

The resulting word-organized storage cell, shown in Fig. 28, is composed of six transistors, a word line W, and two digit-sense lines D1 and D2. Addressing is accomplished by energizing a word line; this action turns on

92CS-30592

Fig. 28 — A word-organized storage cell

(W is the word line; D1 and D2

are data lines).

the p-channel devices on both sides of the selected cell. (Because the cell in Fig. 28 uses p-channel devices, a ground-level voltage is required for selection.)

Fig. 29 shows an eight-transistor bitorganized memory cell that uses X-Y selection. Large memory arrays use a modification of this circuit in which the Yselect transistors are common for each column of storage elements.

Fig. 29 — Eight-transistor bit-organized memory cell with X-Y selection.

### III. Characteristics of **RCA COS/MOS Devices**

RCA COS/MOS digital integrated circuits are specified in two voltage-supply ranges: Aseries types operate from 3 to 15 volts, and Bseries types operate from 3 to 20 volts.

#### FEATURES OF COS/MOS B-SERIES **TYPES**

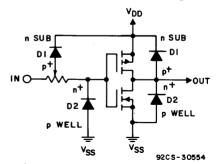

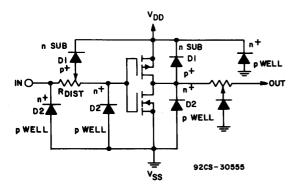

As compared to A-series types, COS/MOS B-series types are characterized by higher output-drive-current capability, balanced outputs (symmetrical p-channel and nchannel characteristics), and improved static protection circuitry. RCA B-series types meet or exceed all the requirements of the IEDEC Tentative Standard "Standard Specifications for B-Series CMOS Devices".

The JEDEC Standard establishes the use of a suffix "UB" for CMOS products that meet all the B-series specifications except that the logical outputs of the devices are not buffered and the input low voltage ( $m V_{IL}$ ) and input high voltage (VIH) specifications are 20 percent and 80 percent of the supply voltage, VDD, respectively. The "B" suffix defines only buffered-output devices in which the output "on" impedance is independent of any and all valid input logic conditions, both preceding and present.

RCA supplies both buffered (B) and unbuffered (UB) versions of the popular NOR and NAND gates to make the advantages of both available to designers. Table II briefly compares the features of the two versions. (For additional information.

refer to RCA Application Note ICAN-6558, "Understanding Buffered and Unbuffered CMOS Characteristics".)

#### A-SERIES CHARACTERISTICS

Static electrical characteristics for RCA Aseries COS/MOS digital integrated circuits are given in Table III.

#### **B-SERIES CHARACTERISTICS**

Static electrical characteristics for RCA Bseries COS/MOS digital integrated circuits

Table II — Comparison of Features of Buffered (B) and Unbuffered (UB) Versions of NOR and NAND Gates

| Characteristic                                             | Buffered<br>Version<br>("B") | Unbuffered<br>Version<br>("UB") |

|------------------------------------------------------------|------------------------------|---------------------------------|

| Propagation Delay (Speed)                                  | Moderate                     | Fast                            |

| Noise Immunity/Margin                                      | Excellent                    | Good                            |

| Output Impedance and<br>Output Transition Time<br>AC Gain  | Constant<br>High             | Variable<br>Low                 |

| Output Oscillation for<br>Slow Inputs<br>Input Capacitance | Yes<br>Low                   | No<br>High                      |

| Table III - Static Electrical Characteristics for "A"-Series COS/MOS Digital |

|------------------------------------------------------------------------------|

| Integrated Circuits (Full Package-Temperature Range)                         |

|                                   |                                   |                                    | CONDITIONS |                 |         |              |                    |              |    |

|-----------------------------------|-----------------------------------|------------------------------------|------------|-----------------|---------|--------------|--------------------|--------------|----|

| SYMBOL                            | PARAMETER                         | V <sub>IN</sub> V <sub>O</sub> (V) |            | V <sub>DD</sub> |         |              |                    | UNITS        |    |

|                                   |                                   |                                    | Min.       | Max.            |         | Min.         | Тур.               | Max.         |    |

| VOL                               | Output Low<br>Voltage             | 5<br>10                            | _<br>_     |                 | 5<br>10 | _            | 0                  | 0.05<br>0.05 | V  |

| V <sub>OH</sub>                   | Output High<br>Voltage            | 0                                  | -          |                 | 5<br>10 | 4.95<br>9.95 | 5<br>10            | -            | V  |

| V <sub>NL</sub><br>(SSI Types)    | Noise Voltage<br>(Input Low)      | _                                  | 3.6<br>7.2 | _               | 5<br>10 | 1.5<br>3     | 2.25<br>4.5        |              | V  |

| V <sub>NH</sub><br>(SSI Types)    | Noise Voltage<br>(Input High)     | -                                  | _          | 1.4<br>2.8      | 5<br>10 | 1.5<br>3     | 2.25<br>4.5        |              | V  |

| V <sub>NL</sub><br>(MSI Types)    | Noise Voltage<br>(Input Low)      | _                                  | 4.2<br>9   | _               | 5<br>10 | 1.5<br>3     | 2.25<br>4.5        | _            | V  |

| V <sub>NH</sub><br>(MSI Types)    | Noise Voltage<br>(Input High)     | _                                  | _          | 0.8<br>1        | 5<br>10 | 1.5<br>3     | 2.25<br>4.5        | _            | V  |

| V <sub>NML</sub>                  | Noise Margin<br>(Input Low)       | _                                  | 4.5<br>9   |                 | 5<br>10 | 1            | _                  |              | V  |

| V <sub>NMH</sub>                  | Noise Margin<br>(Input High)      | _                                  |            | 0.5<br>1        | 5       | 1            | _                  | _            | V  |

| ηΓ <sub>1</sub> ΙΗ                | Input Leakage<br>Low              | _                                  | -          | _               | 15      | _            | ± 10 <sup>-5</sup> | ± 1          | μΑ |

| ار                                | Quiescent Device<br>Leakage       | -                                  | -          | -               | 5,10,15 | See Da       | ta Sheets          |              | μΑ |

| I <sub>DN</sub> , I <sub>DP</sub> | Output Source and<br>Sink Current | -                                  | _          | -               | 5,10    | See Da       | ta Sheets          |              | mA |

NOTE: Logic Level Inversion Assumed.

are given in Table IV. Table V shows the B-series types included in each of three categories of device complexity: (1) gates and inverters; (2) buffers, flip-flops, latches and multi-level gates (MSI-1 types); and (3) complex logic (MSI-2 types).

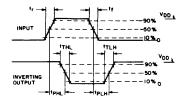

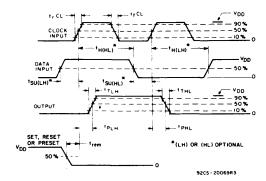

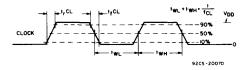

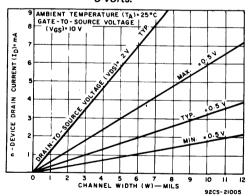

Table VI lists the standard definitions for many of the specified ac parameters for

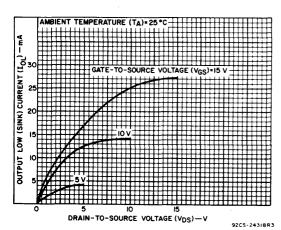

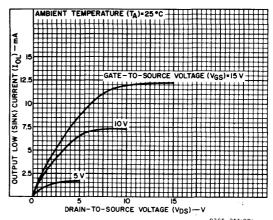

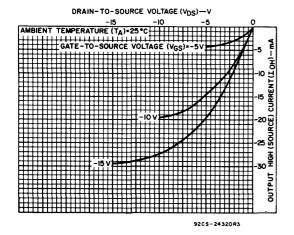

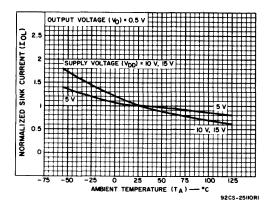

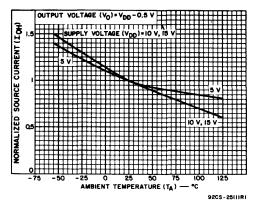

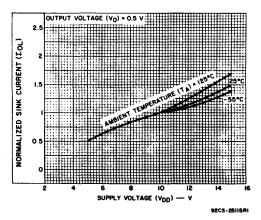

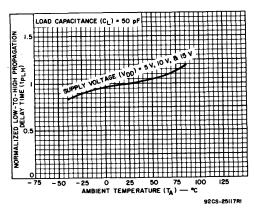

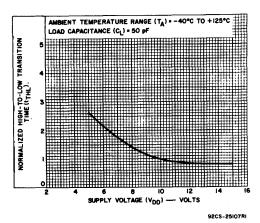

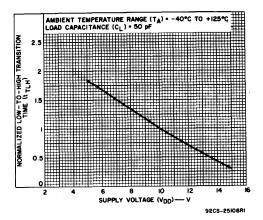

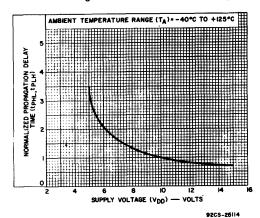

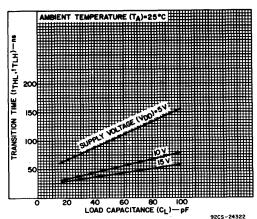

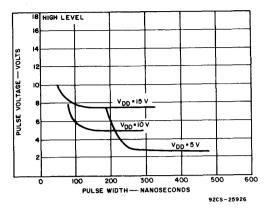

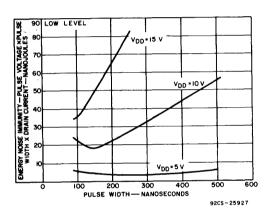

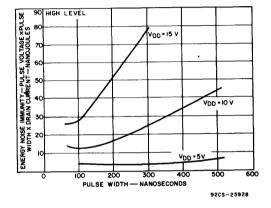

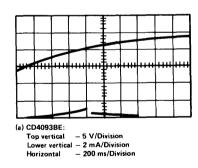

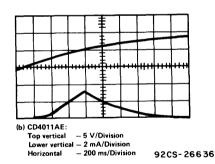

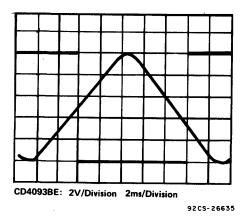

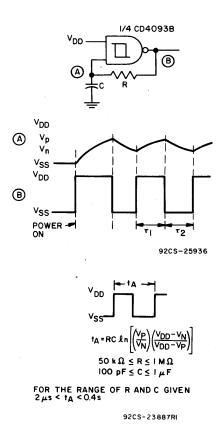

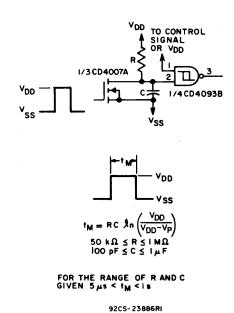

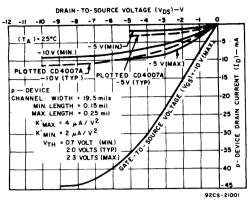

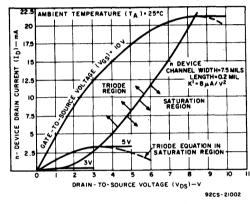

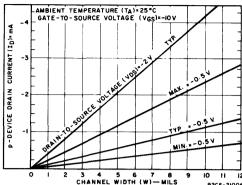

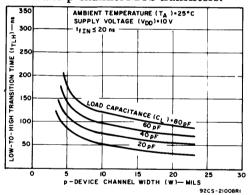

COS/MOS devices. The figures associated with Table VI show the parameter waveforms and test requirements. Figs. 30 through 45 show curves of device characteristics and include data on transition time, propagation delay time, and output drive current as a function of supply voltage.

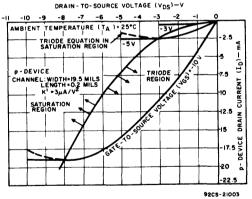

Fig. 30 — Typical output n-channel drain characteristics for COS/MOS B-series types.

Fig. 31 – Minimum output n-channel drain characteristics for COS/MOS

B-series types.

Table IV — Static Electrical Characteristics for "B"-Series COS/MOS Digital Integrated Circuits (Full Package-Temperature Range)

| CHARACTER                                | CON       | DITIONS          | \$  | Value        | es at -55.                  | +25. +12   | 25 Apply | to D,F,H      | JRES (°C<br>Packages<br>Package                  | )        | UNITS      |  |

|------------------------------------------|-----------|------------------|-----|--------------|-----------------------------|------------|----------|---------------|--------------------------------------------------|----------|------------|--|

| ISTIC                                    |           |                  |     | 1            | Values at -40, +25, +85 App |            |          | +25           |                                                  |          |            |  |

| ,56                                      | Vo        | VIN              | VDD | F= 1         | -40                         | +85        | +125     | Min.          | Typ.                                             | Max.     |            |  |

|                                          | (V)       | (V)              | (V) | -55          |                             | 7.5        | 7.5      | 1411111       | 0.01                                             | 0.25     |            |  |

| Quiescent Device                         |           | 0,5              | 5   | 0.25         | 0.25                        | 15         | 15       |               | 0.01                                             | 0.5      |            |  |

| Current, IDD Max. Gates, Inverters       |           | 0,10             | 10  | 0.5          | 0.5                         | 30         | 30       | =+            | 0.01                                             | 1        |            |  |

|                                          |           | 0,15             | 15  | 1            | 1                           |            | 150      |               | 0.02                                             | 5        |            |  |

|                                          | -         | 0,20             | 20  | 5            | 5                           | 150        |          |               |                                                  |          |            |  |

| Buffers, Flip-Flops,                     |           | 0,5              | 5   | 1            | 1                           | 30         | 30       |               | 0.02                                             | 1        | İ          |  |

| Latches, Multi-                          |           | 0,10             | 10  | 2            | 2                           | 60         | 60       |               | 0.02                                             | 2        | μΑ         |  |

| Level Gates                              | T T       | 0.15             | 15  | 4            | 4                           | 120        | 120      |               | 0.02                                             | 4        | <b>"</b> " |  |

| (MSI-1 Types)                            |           | 0,20             | 20  | 20           | 20                          | 600        | 600      |               | 0.04                                             | 20       |            |  |

| Complex Logic                            |           | 0.5              | 5   | 5            | 5                           | 150        | 150      | -             | 0.04                                             | 5        |            |  |

| (MSI-2 Types)                            | ŀ         | 0,10             | 10  | 10           | 10                          | 300        | 300      | - 1           | 0.04                                             | 10       | }          |  |

|                                          | <u> </u>  | 0,15             | 15  | 20           | 20                          | 600        | 600      | -             | 0.04                                             | 20       |            |  |

|                                          | <b> </b>  | 0.20             | 20  | 100          | 100                         | 3000       | 3000     | - 1           | 0.08                                             | 100      |            |  |

| Output Low                               | 0.4       | 0,20             | 5   | 0.64         | 0.61                        | 0.42       | 0.36     | 0.51          | 1                                                |          |            |  |

| Output Low<br>(Sink) Current<br>IOL Min. | 0.5       | 0.10             | 10  | 1.6          | 1.5                         | 1.1        | 0.9      | 1.3           | 2.6                                              |          | 1          |  |

|                                          | 1.5       | 0.15             | 15  | 4.2          | 4                           | 2.8        | 2.4      | 3.4           | 6.8                                              | _        | mA         |  |

|                                          | 4.6       | 0,13             | 5   | -0.64        | -0.61                       | -0.42      | -0.36    | -0.51         | -1                                               | _        |            |  |

| Output High<br>(Source)                  | 2.5       | 0,5              | 5   | -2           | -1.8                        | -1.3       | -1.15    | -1.6          | -3.2                                             |          |            |  |

| Current,                                 |           |                  | 10  | -1.6         | -1.5                        | -1.1       | -0.9     | -1.3          | -2.6                                             |          |            |  |

| IOH Min.                                 | 9.5       | 0,10             | 15  | -4.2         | -4                          | -2.8       | -2.4     | -3.4          | -6.8                                             |          | 1          |  |

|                                          | 13.5      | 0,15             | 5   | -4.2         |                             | 05         |          | -             | 0                                                | 0.05     | 1          |  |

| Output Voltage:                          |           | 0,5              | 10  |              |                             | 05         |          | <del>  </del> | 0                                                | 0.05     | .05        |  |

| Low-Level,                               |           | 0,10             |     | +            |                             | 05         |          | <del> </del>  | 0                                                | 0.05     |            |  |

|                                          |           | 0,15             | 15  |              |                             | .95        |          | 4,95          | 5                                                |          | <b>┤ ∨</b> |  |

| Output Voltage:                          |           | 0,5              | 5   | <del> </del> |                             | .95<br>.95 |          | 9.95          | 10                                               |          | 1          |  |

| High-Level                               |           | 0,10             | 10  | <b>_</b>     |                             |            |          | 14.95         | 15                                               |          | ┪          |  |

| VOH Min.                                 |           | 0,15             | 15  |              |                             | .95        |          | 14.95         | -                                                | 1.5      | _          |  |

| Input Low                                | 0.5, 4.5  |                  | 5   |              |                             | .5         |          | +             | <del>                                     </del> | 3        | 4          |  |

| Voltage,                                 | 1,9       |                  | 10  |              |                             | 3          |          |               | <del>                                     </del> | 4        | -          |  |

| VIL Max.<br>B Types                      | 1.5, 13.5 | -                | 15  | 1            |                             | 4          |          | -             |                                                  |          |            |  |

| UB Types                                 | 0.5, 4.5  |                  | 5   |              |                             | 1          |          |               |                                                  | 1        |            |  |

| OB Types                                 | 1, 9      | <del>  _</del> _ | 10  |              |                             | 2          |          | _             |                                                  | 2        | _}         |  |

|                                          | 1.5, 13.5 |                  | 15  | $\dashv$     |                             | 2.5        |          | _             | _                                                | 2.5      | J ∨        |  |

| Input High                               | 0.5, 4.5  | <del> </del> _   | 5   | +            |                             | 3.5        |          | 3.5           | _                                                | _        | ]          |  |

| Voltage.                                 | 1, 9      | <del>  _</del>   | 10  | <del></del>  |                             | 7          |          | 7             |                                                  |          |            |  |

| VIH Min.<br>B Types                      | 1.5, 13.5 |                  | 15  |              |                             | 11         |          | 11            | _                                                | _        |            |  |

| UB Types                                 | 0.5, 4.5  | =                | 5   |              |                             | 4          |          | 4             | <del>  -</del>                                   | <u> </u> | -          |  |

|                                          | 1, 9      | _                | 10  |              |                             | 8          |          | 8             | <del>  -</del>                                   | <b>↓</b> | 4          |  |

|                                          | 1.5, 13.5 | -                | 15  |              |                             | 12.5       |          | 12.5          | <u> </u>                                         | 1 =      |            |  |

| Input Current                            | -         | 0,18             | 18  | ±0.1         | ±0.1                        | ±1         | ±1       | _             | ±10-5                                            | ±0.1     | μΑ         |  |

| 3-State Output Leakage Current IOUT Max. | 0, 18     | 0,18             | 18  | ±0.4         | ±0.4                        | ±12        | ±12      | _             | ±10-4                                            | ±0.4     | μΑ         |  |

Table V - Classification According to Circuit Complexity

| Gates/<br>Inverters |                                                                                                                    | Buffers/Flip<br>Latches/Mul<br>Gates (MS                                                                   | ti-Level                                                                                                                               | Complex Logic (MSI-2)                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                     | CD4023UB CD4025B CD4025UB CD4048B CD4066B CD4069UB CD4071B CD4072B CD4073B CD4075B CD4075B CD4078B CD4078B CD4082B | CD4009UB CD4010B CD4013B CD4019B CD4027B CD4030B CD4041UB CD4042B CD4043B CD4044B CD4047B CD4049UB CD4050B | CD4070B CD4077B CD4085B CD4086B CD4093B CD4095B CD4096B CD4098B CD4502B CD40106B CD40107B CD40107B CD40174B CD40174B CD40174B CD40174B | CD4006B CD4008B CD4014B CD4015B CD4017B CD4018B CD402B CD4021B CD4022B CD4024B CD4026B CD4028B CD4031B CD4032B CD4031B CD4032B CD4033B CD4034B CD4034B CD4034B CD4035B CD4034B CD4035B CD4035B CD4046B CD4046B | CD4051BBCD4052BBCD4053BBCD4054BBCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4060BCD4510BCD4510BCD4512BCD4514BCD4515BCD4516BCD4516BCD4517BCD4518BCD4520B | CD4527B CD4532B CD4536B CD4556B CD4556B CD4585B CD4724B CD40100B CD40101B CD40102B CD40103B CD40105B CD40108B CD40114B CD40147B CD40160B CD40161B CD40161B CD40162B CD40163B |  |

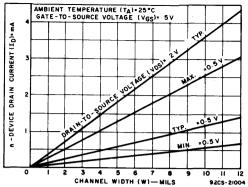

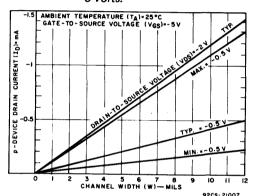

Fig. 32 — Typical output p-channel drain characteristics for COS/MOS B-series types.

CD40208B

Fig. 33 — Minimum output p-channel drain characteristics for COS/MOS B-series types.

| Table VI - Dynamic | Electrical | Characteristics    | - Definitions   |

|--------------------|------------|--------------------|-----------------|

| Table VI — Dynamic | LICCLICA   | Ollai actel istics | - Dellillicions |

| Characteristic                           | Symbol                              | Lii  | Limits |         |  |

|------------------------------------------|-------------------------------------|------|--------|---------|--|

|                                          |                                     | Max. | Min.   | (Fig.)  |  |

| Propagation Delay:                       |                                     |      |        |         |  |

| Outputs going high to low                | <sup>t</sup> PHL                    | X    |        | (A)     |  |

| Outputs going low to high                | <sup>t</sup> PLH                    | X    |        | , ,,    |  |

| Output Transition Time:                  |                                     |      |        |         |  |

| Outputs going high to low                | <sup>t</sup> THL                    | ×    |        | (A)     |  |

| Outputs going low to high                | <sup>t</sup> TLH                    | X    |        | 1       |  |

| Pulse Width-Set, Reset, Preset           |                                     |      | v      | 4 (0)   |  |

| Enable, Disable, Strobe, Clock           | tWL or tWH                          |      | X      | 1 (B)   |  |

| Clock Input Frequency                    | <sup>f</sup> CL                     | X    |        | 1,2 (B) |  |

| Clock Input Rise and Fall Time           | <sup>t</sup> rCL <sup>, t</sup> fCL | X    |        | (B)     |  |

| Set-Up Time                              | <sup>t</sup> SU                     |      | X      | 1 (C)   |  |

| Hold Time                                | <sup>t</sup> H                      |      | X      | 1 (C)   |  |

| Removal Time - Set, Reset, Preset-Enable | <sup>t</sup> REM                    |      | X      | 1 (C)   |  |

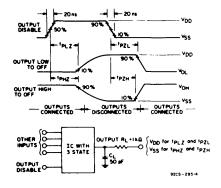

| Three-State Disable Delay Times:         |                                     |      |        |         |  |

| High level to high impedance             | <sup>t</sup> PHZ                    | X    |        | (D)     |  |

| High impedance to low level              | <sup>t</sup> PZL                    | X    |        | (D)     |  |

| Low level to high impedance              | <sup>t</sup> PLZ                    | ×    |        | (D)     |  |

| High impedance to high level             | <sup>t</sup> PZH                    | X    |        | (D)     |  |

NOTE: (1) By placing a defining min. or max. in front of definition, the limits can change from min. to max., or vice versa.

(2) Clock input waveform should have a 50% duty cycle and be such as to cause the outputs to be switching from 10% Vpp to 90% Vpp in accordance with the device truth table.

Fig. A — Transition times and propagation delay times, combination logic.

Fig. C — Setup times, hold times, removal time, and propagation delay times for positive-edge triggered sequential logic circuits.

Fig. B — Clock-pulse rise and fall times and pulse width.

Fig. D — Three-state propagation delay wave shapes and test circuit.

Fig. 34 — Variation of normalized sink current (IOL) with temperature for COS/MOS B-series types.

Fig. 35 — Variation of normalized source current (IOH) with temperature for COS/MOS B-series types.

Fig. 36 — Variation of normalized sink current (IOL) with supply voltage for COS/MOS B-series types.

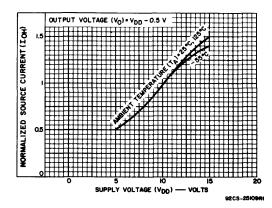

Fig. 37 — Variation of normalized source current (IOH) with supply voltage for COS/MOS B-series types.

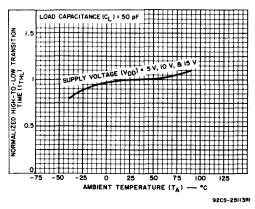

Fig. 38 — Variation of normalized high-to-low transition time (tTHL) with temperature for COS/MOS B-series types.

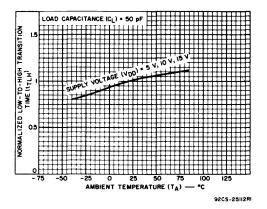

Fig. 39 — Variation of normalized low-to-high transition time (tтрн) with temperature for COS/MOS B-series types.

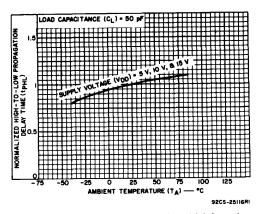

Fig. 40 — Variation of normalized high-to-low propagation delay time (tpHL) with temperature for COS/MOS B-series types.

Fig. 41 — Variation of normalized low-to-high propagation delay time (tpl H) with temperature for COS/MOS B-series types.

Fig. 42 — Variation of normalized high-to-low transition time (t<sub>THL</sub>) with supply voltage for COS/MOS B-series types.

Fig. 43 — Variation of normalized low-to-high transition time (tŢĹĦ) with supply voltage for COS/MOS B-series types.

Fig. 44 — Variation of normalized propagation delay time (tpHL, tpLH) with supply voltage for COS/MOS B-series types.

Fig. 45 — Variation of normalized transition time (t<sub>THL</sub>, t<sub>TLH</sub>) with load capacitance at three levels of supply voltage for COS/MOS B-series types.

#### **PACKAGES**

Maximum ratings for power dissipation and the operating temperature range depend on package type. RCA COS/MOS integrated circuits are available in four types of packages:

| Dual-in-line   | welded-seal     | or       | brazed-seal    |

|----------------|-----------------|----------|----------------|

| ceramic .      |                 |          | D suffix       |

| Dual-in-line f | rit-seal cerami | <b>c</b> | F suffix       |

| Dual-in-line   | lastic          |          | E suffix       |

| Ceramic flat   | oack (MIL typ   | es on    | ly) . K suffix |

Depending on the requirements of the individual integrated-circuit type, the number of leads may range from 8 to 40 per package.

For bonding on hybrid substrates, unpackaged die (chips) are also available; they are indicated by an H suffix.

#### MAXIMUM RATINGS AND RECOM-MENDED OPERATING CONDITIONS

The maximum ratings for both A- and B-series COS/MOS digital integrated circuits are given in Table VII. Ratings which differ because of the package type used are indicated. Table VIII gives the recommended operating conditions for A- and B-series types.

#### TYPES CLASSIFIED BY FUNCTION

The RCA COS/MOS digital integrated circuit types are classified by function in Table IX. The Table includes A, B, and UB types. Types suitable for more than one of the functions listed are indicated by footnote symbols which cross-refer the type to the additional functional category.

### Table VII – Maximum Ratings for "A"- and "B"-Series Types (Absolute-Maximum Values)

| DC SUPPLY-VOLTAGE RANGE, (V <sub>DD</sub> )                                                               |             |

|-----------------------------------------------------------------------------------------------------------|-------------|

| (Voltages referenced to V <sub>SS</sub> Terminal):                                                        |             |

| STANDARD "A"-SERIES TYPES                                                                                 | ٧           |

| HIGH-VOLTAGE "B"-SERIES TYPES0.5 to +20                                                                   | ٧           |

| INPUT VOLTAGE, RANGE, ALL INPUTS                                                                          | ٧           |

| DC INPUT CURRENT, ANY ONE INPUT ("B"-series only) ±10 m                                                   | ۱A          |

| POWER DISSIPATION PER PACKAGE (PD):                                                                       |             |

| For T <sub>A</sub> = -40 to +60°C (PACKAGE TYPE E)                                                        | W           |

| For T <sub>A</sub> = +60 to +85°C (PACKAGE TYPE E) Derate Linearly at 12 mW/°C to 200 m                   |             |

| For T <sub>A</sub> = -55 to +100°C (PACKAGE TYPES D,F)                                                    |             |

| For TA = +100 to +125°C (PACKAGE TYPES D, F) Derate Linearly at 12 mW/°C to 200 m                         | W           |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                                                  |             |

| For TA = FULL PACKAGE-TEMPERATURE RANGE (All Package Types) 100 m                                         | ١ <b>VV</b> |

| OPERATING-TEMPERATURE RANGE (TA):                                                                         | ۰.          |

| PACKAGE TYPES D, F, H                                                                                     | ٠<br>د      |

| PACKAGE TYPE E                                                                                            | o C         |

| STORAGE TEMPERATURE RANGE (T <sub>stg</sub> )                                                             | Ü           |

| LEAD TEMPERATURE (DURING SOLDERING): At distance 1/16 + 1/32 inch (1.59 + 0.79 mm) from case for 10 s max | ٥,          |

| AT DISTANCE 1/10 7 1/32 INCOLUMN 7 U./MINDU FROM CASE FOR TUS MAX                                         | •           |

#### Table VIII - Recommended Operating Conditions for the "A"- and "B"-Series Types

|                                                           |            | Li   |      |       |

|-----------------------------------------------------------|------------|------|------|-------|

| Characteristic                                            |            | Min. | Max. | Units |

| Supply-voltage range                                      | "A" series | 3    | 12   | volts |

| (For T <sub>A</sub> = Full package-<br>temperature range) | "B" series | 3    | 18   | volts |

Table IX - RCA COS/MOS Digital Integrated Circuit Types Classified by Function

|                        |                       |                      |                     |                                      |                       |                     | MULTIVIB           | PATORS            |

|------------------------|-----------------------|----------------------|---------------------|--------------------------------------|-----------------------|---------------------|--------------------|-------------------|

| GATES                  |                       |                      |                     |                                      |                       |                     | MOLITAID           | TATORIO           |

| Single-Level           |                       |                      |                     | Multi-Level    Multi-Level   Schmitt |                       |                     |                    |                   |

|                        |                       |                      | Buffers &           | Multi-                               | Decoders/<br>Encoders | Trigger             | Flip-Flops/        | Latches           |

| NOR/N                  |                       | OR/AND               | Inverters           | function/AOI                         |                       |                     |                    | CD4096B           |

|                        | CD4012B               | CD4071B              | CD4007UB            | CD4019B                              | CD4028B               | CD4093B<br>CD40106B | CD4013B<br>CD4013A | CD4090B**         |

|                        | CD4012UB              | CD4072B              | CD4007A             | CD4019A                              | CD4028A<br>CD4514B    | CD40106B            |                    | CD4508B           |

| CD4000A                | CD4012A               | CD4073B              | CD4009UB            | CD4030B                              | CD4514B<br>CD4515B    |                     |                    | CD4724B**         |

|                        | CD4023B               | CD4075B              | CD4009A             | CD4030A<br>CD4037A                   | CD4532B               |                     | CD4042B            | CD40174B          |

|                        | CD4023UB              | CD4081B              | CD4010B             | CD4037A<br>CD4048B                   | CD4555B*              |                     | CD4042A            |                   |

|                        | CD4023A               | CD4082B              | CD4010A<br>CD4041UB | CD4048A                              | CD4556B*              |                     | CD4043B            | Astable/<br>Mono- |

| CD4002B                | CD4025B<br>CD4025UB   |                      | CD404108            | CD4070B=                             | CD40147B              |                     | CD4043A            | stable            |

| CD4002UB   CD4002A     | CD40250B              |                      | CD4049UB            | CD4077B=                             | 00.401.11.2           |                     | CD4044B            | stable            |

| CD4002A<br>CD4011B     | CD4068B               |                      | CD4049A             | CD4085B                              |                       |                     | CD4044A            | CD4047B           |

|                        | CD4078B               |                      | CD4050B             | CD4086B                              |                       |                     | CD4076B**          | CD4047A           |

| CD4011A                | CD40107B              |                      | CD4050A             |                                      |                       |                     | CD4095B            | CD4098B           |

| 05401111               |                       |                      | CD4069UB            | -6                                   | *See                  |                     | **See              |                   |

|                        |                       |                      | CD4502B             | ■See<br>Comparators                  | Demultiplexers        |                     | Storage            |                   |

|                        |                       |                      | CD40107B            | Comparation                          |                       | l                   | Registers          |                   |

|                        | DECICTED              | ,                    |                     | NTERS                                | MULTIPLEXERS/         | PHASE.              | QUAD               | INTER-            |

|                        | REGISTER              | •                    | 000                 | MICHS                                | DEMULTIPLEXERS        | LOCKED              | BILATERAL          | FACE              |

|                        |                       | FIFO                 | Diagon.             |                                      | Analog/Digital        | LOOP                | SWITCHES           | CIRCUITS          |

| Ob. de                 | ~                     | Buffer               | Binary<br>Ripple    | Synchronous                          | Data Selectors        |                     |                    |                   |

| Shift                  | Storage               |                      |                     | <u> </u>                             |                       | CD4046B             | CD4016B+           | CD4009UB          |

| CD4006B                | CD4076B               | CD40105B             | CD4020B             | CD4017B<br>CD4017A                   | CD401684<br>CD4016A4  | CD4046B             | CD4016A+           | CD4009A           |

| CD4006A                | CD4099B<br>CD4724B    |                      | CD4020A<br>CD4024B  | CD4017A                              | CD4019B               | 0040407             | CD4066B+           | CD4010B           |

| CD4014B<br>CD4014A     | CD4724B<br>CD40108B•  |                      | CD4024B             | CD4018A                              | CD4019A               | İ                   | CD4066A+           | CD4010A           |

| CD4014A<br>CD4015B     | CD40108B•             |                      | CD4040B             | CD4022B                              | CD4051B               |                     |                    | CD4049UB          |

| CD4015B                | CD40200B*             |                      | CD4040A             | CD4022A                              | CD4052B               |                     |                    | CD4049A           |

| CD4021B                | }                     | 1                    | CD4060B             | CD4029B                              | CD4053B               | ì                   | 1                  | CD4050B           |

| CD4021A                |                       | ŀ                    | CD4060A             | CD4029A                              | CD4066B▲              | i                   |                    | CD4050A           |

| CD4031B                |                       |                      |                     | CD4059A                              | CD4066A*              | l                   | l                  | CD40107B          |

| CD4031A                | Ì                     | 1                    | <u> </u>            | CD4510B                              | CD4067B               |                     |                    | CD40109B          |

| CD4034B                | l                     | 1                    |                     | CD4516B                              | CD4097B               |                     | Ì                  | CD40115           |

| CD4034A                | ļ                     | ļ                    | TIMERS              | CD4518B                              | CD4555B4              | 1                   | ł .                | ł                 |

| CD4035B                | l                     |                      |                     | CD4520B                              | CD4556B®              | 1                   |                    |                   |

| CD4035A                | l                     |                      | CD4045B             | CD40102B                             | CD40257B              | l                   |                    |                   |

| CD4062A                | 1                     | 1                    | CD4045A             | CD40103B                             |                       | 1                   | 1                  |                   |

| CD4094B                |                       |                      | CD4536B             | CD40160B                             |                       | 1                   |                    |                   |

| CD4517B                | l.,                   |                      |                     | CD40161B                             | ≜See ⊕See             | 1                   | ◆See               | 1                 |

| CD40100B               | ●See                  |                      |                     | CD40162B                             | Quad Decoders/        | i                   | Multiplexers       |                   |

|                        | Multiport<br>Register |                      |                     | CD40163B                             | Bilateral Encoders    | 1                   | I management       | I                 |

| 1                      | register              |                      |                     | CD40192B<br>CD40193B                 | Switch                |                     | 1                  | 1                 |

| <del>-</del>           | DITUMET               | CCIRCUIT             | <u></u>             |                                      | DISPLAY DRIVERS       | <del></del>         | CROSS-             | MEMORY            |

| ARITHMETIC CIRCUITS    |                       |                      | 1                   | For For                              |                       |                     | POINT              |                   |

| A 44 /                 | ALU/Rate              | Parity<br>Generator/ | Multiport           |                                      | LCD*                  | LEDOO               | SWITCHES           |                   |

| Adders/<br>Comparators | Multipliers           | Checker              | Register            | With Counter                         | Drive                 | Drive               |                    |                   |

|                        | <u> </u>              |                      | <u> </u>            | CD4026B                              | CD4054B               | CD4511B             | CD22100 ▼          | CD40114B          |

| CD4008B                | CD4057A               | CD40101B             | CD40108B*           | CD4026B<br>CD4026A                   | CD4054B<br>CD4055B    | 55-5116             | CD22101 V          | 1                 |

| CD4008A<br>CD4030B     | CD4089B<br>CD4527B    |                      | CD40206B*           | CD4026A                              | CD4056B               |                     | CD22102 V          | l                 |

| CD4030B<br>CD4030A     | CD45278<br>CD40181B   | 1                    | 1                   | CD4033A                              |                       | 1                   |                    | 1                 |

| CD4030A                | CD40181B              | 1                    | 1                   | CD40110B                             |                       |                     | 1                  | 1                 |

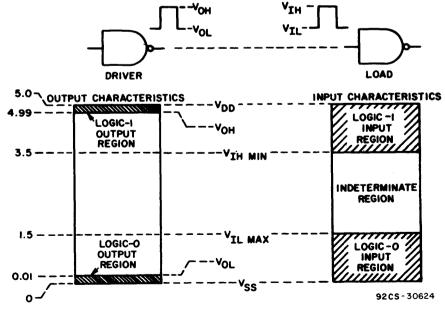

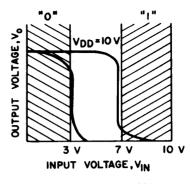

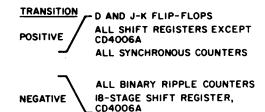

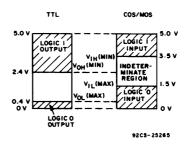

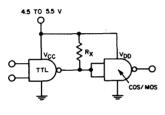

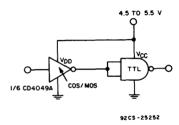

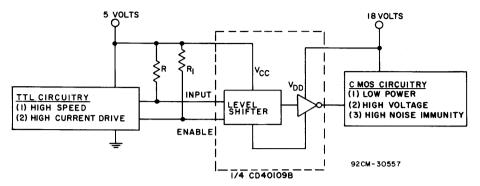

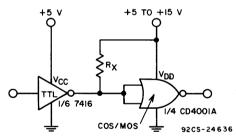

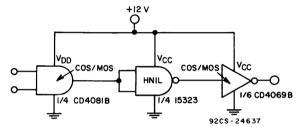

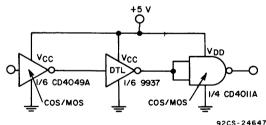

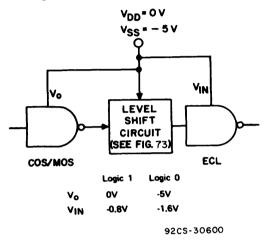

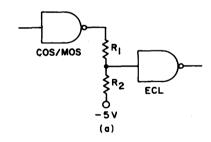

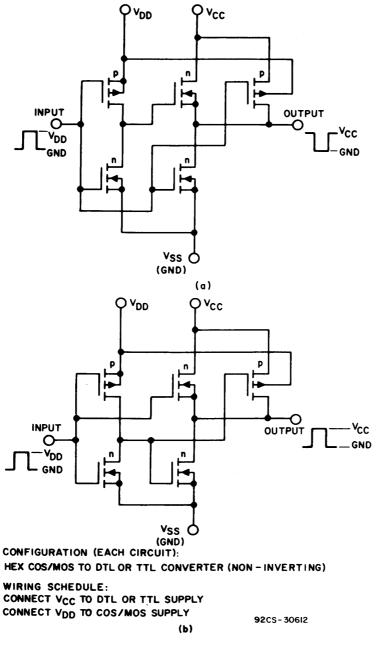

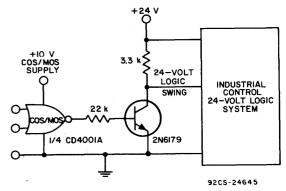

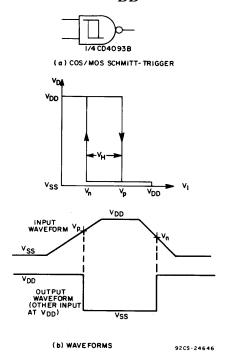

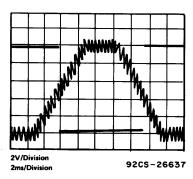

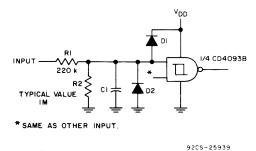

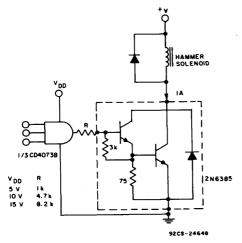

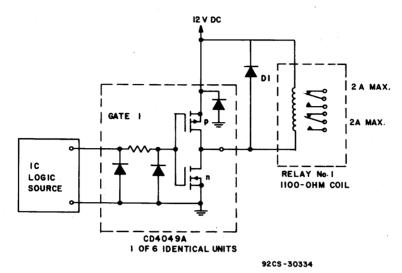

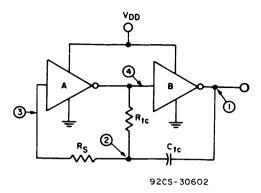

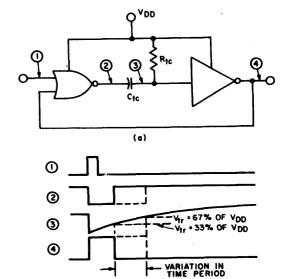

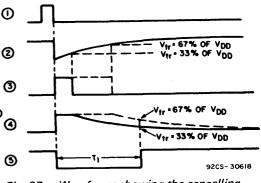

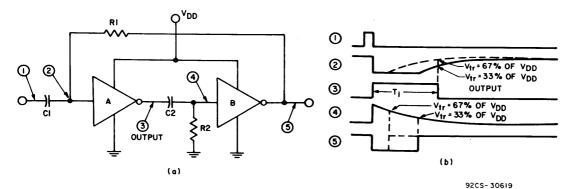

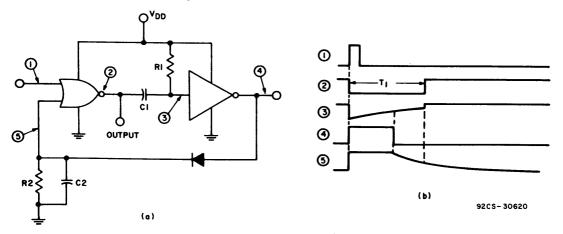

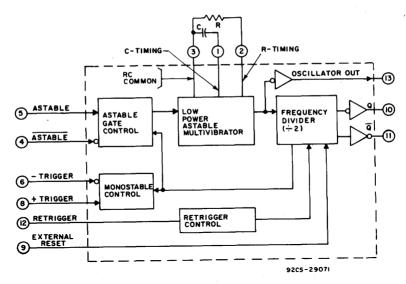

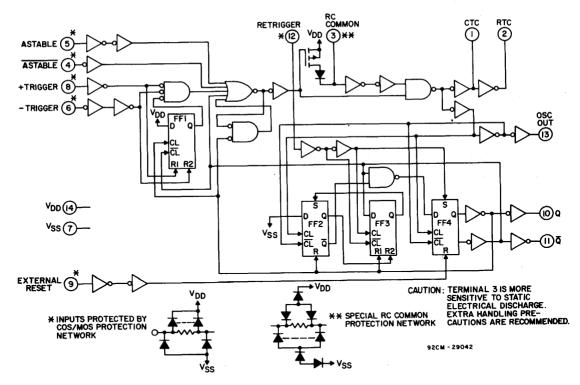

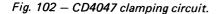

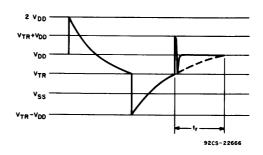

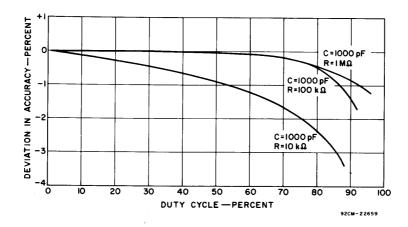

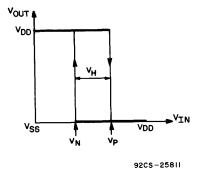

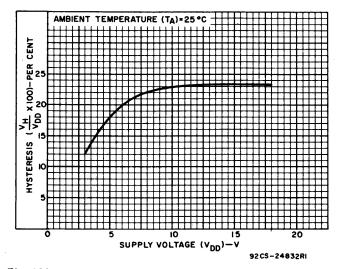

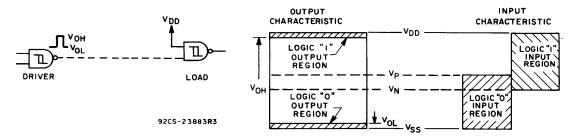

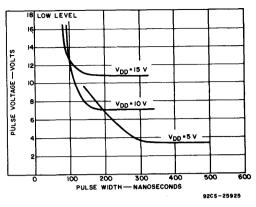

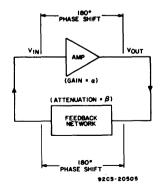

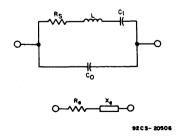

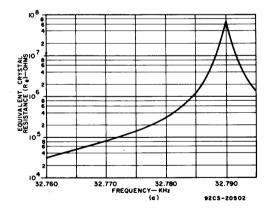

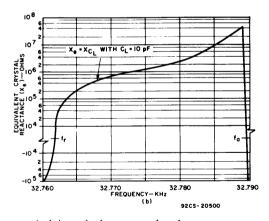

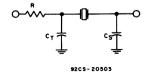

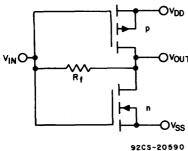

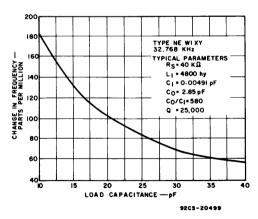

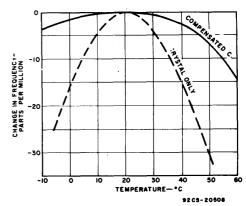

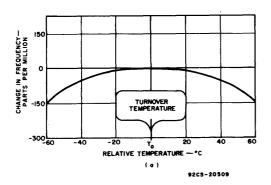

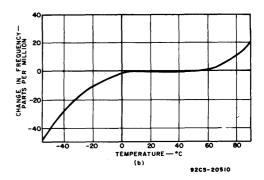

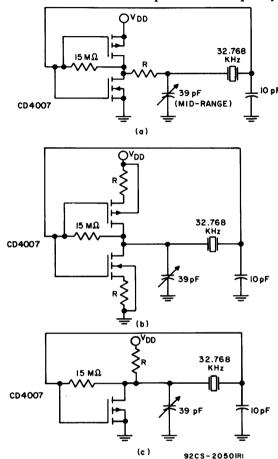

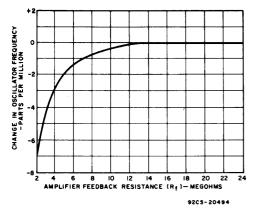

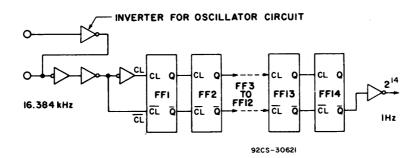

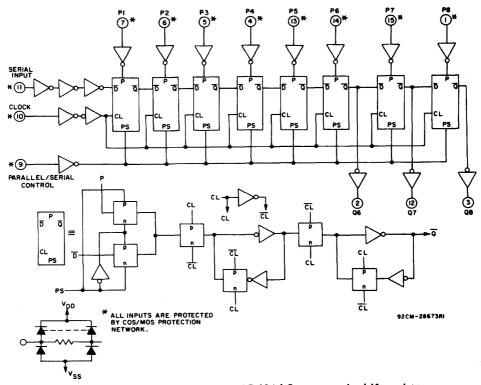

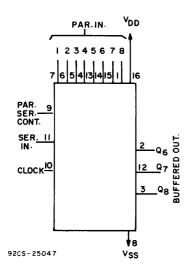

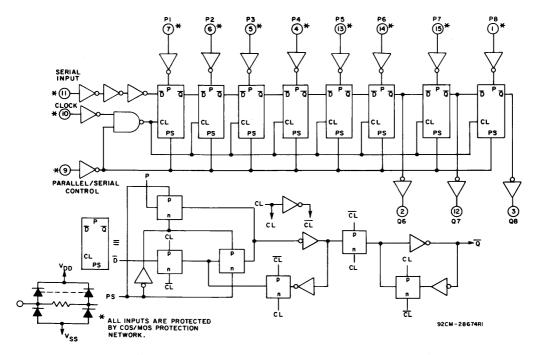

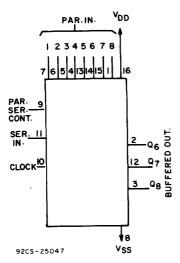

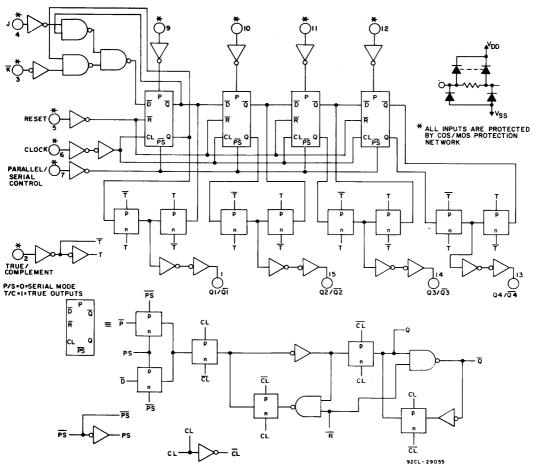

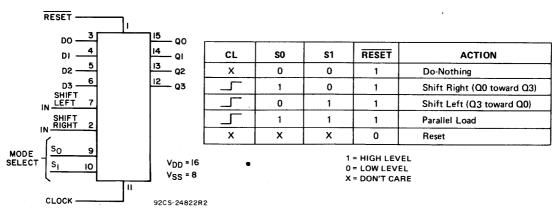

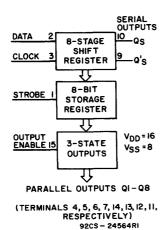

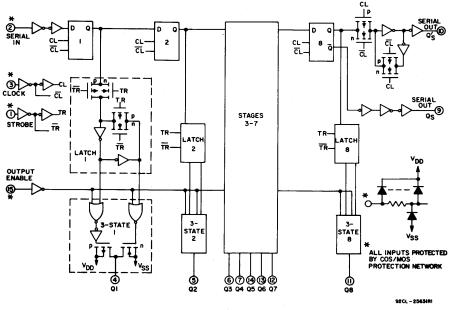

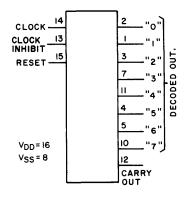

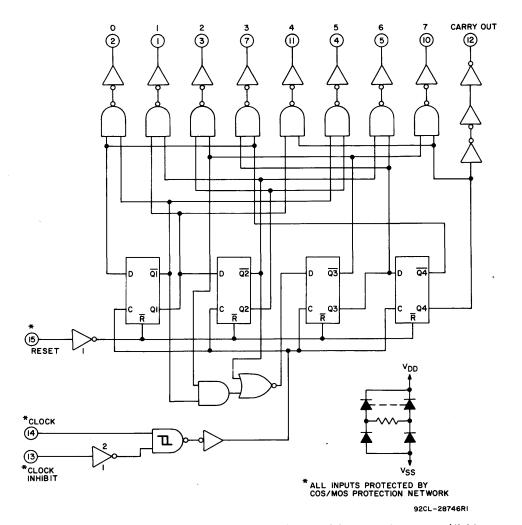

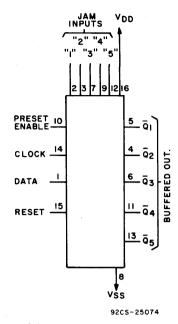

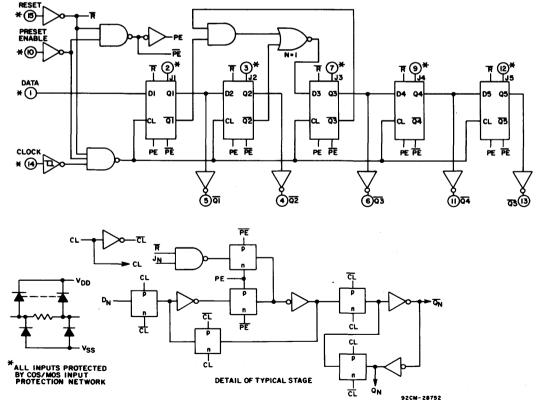

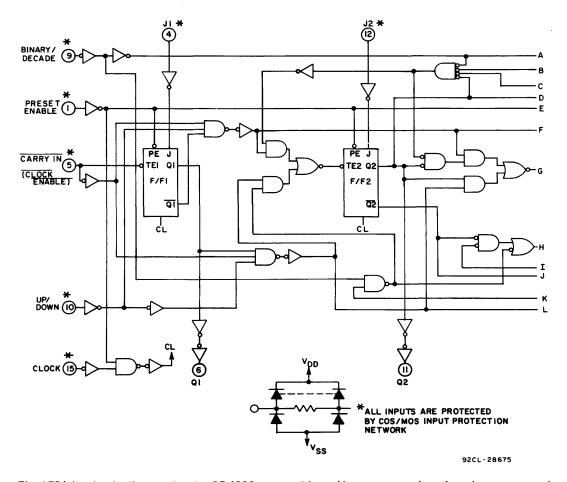

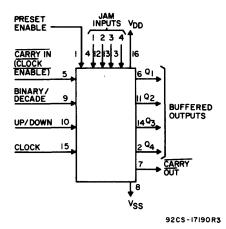

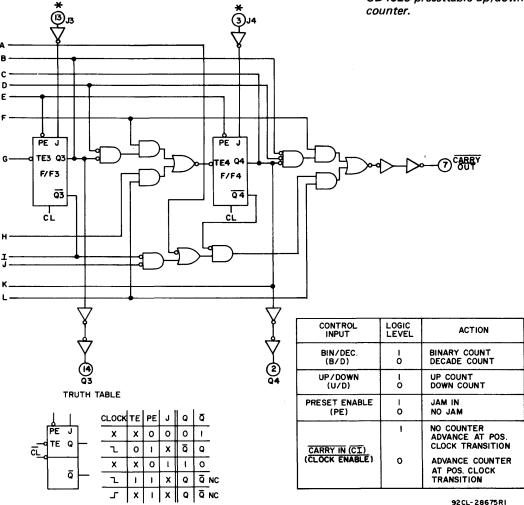

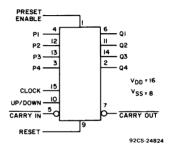

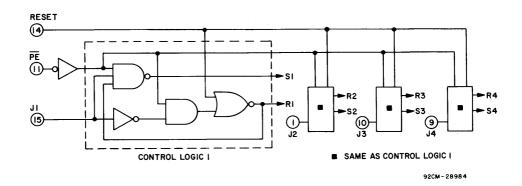

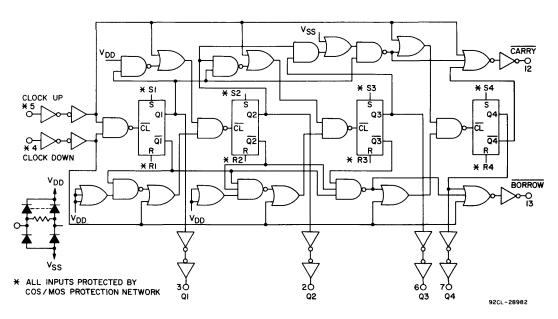

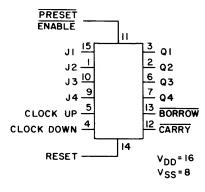

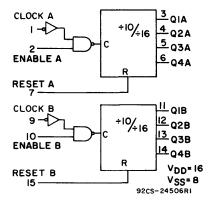

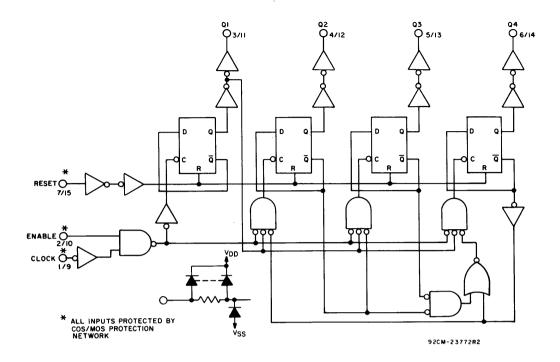

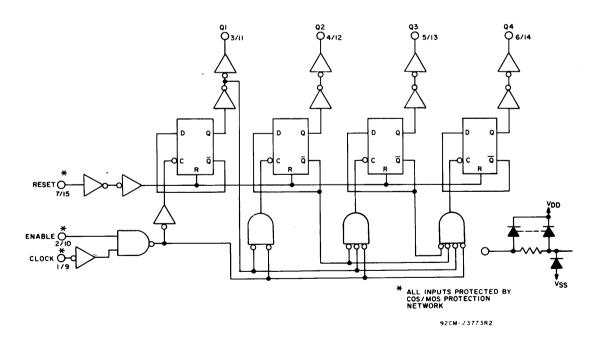

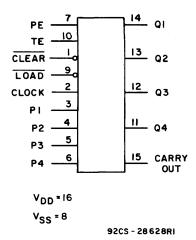

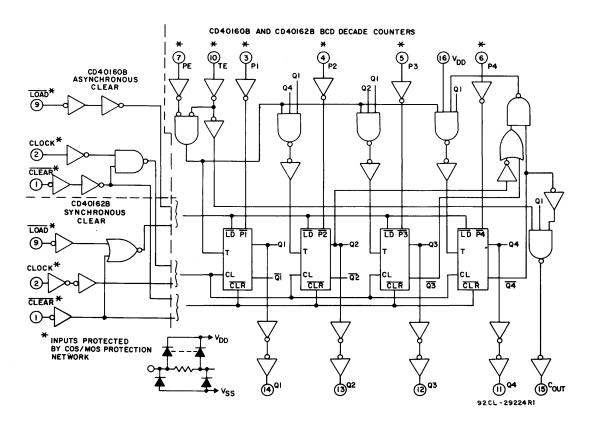

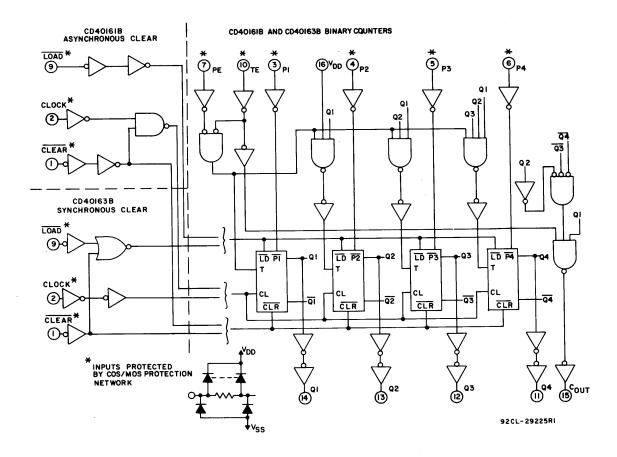

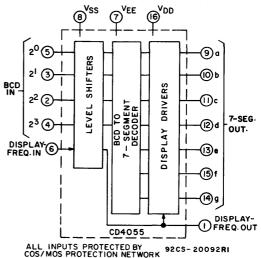

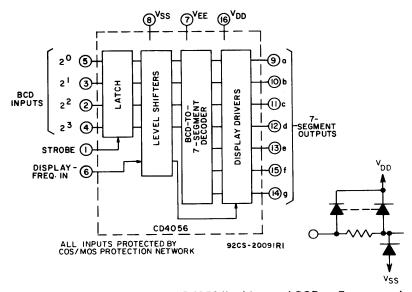

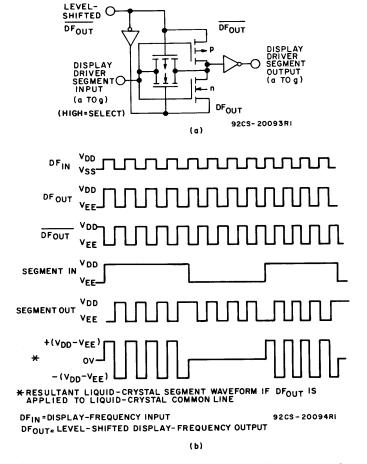

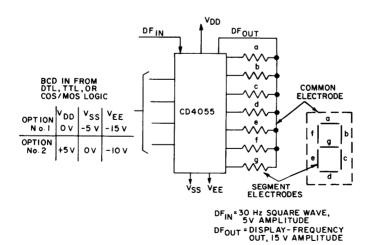

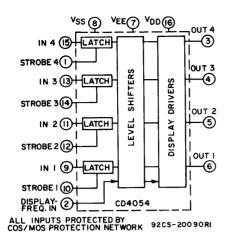

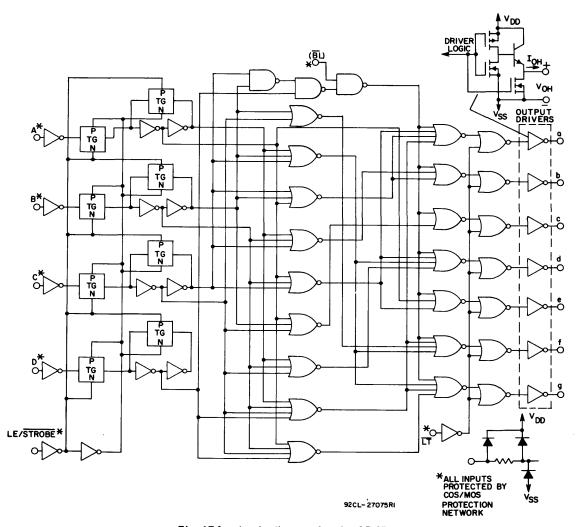

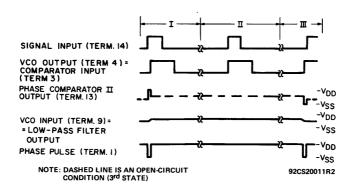

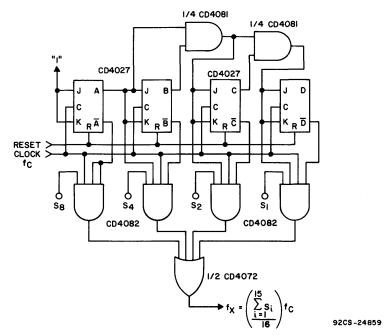

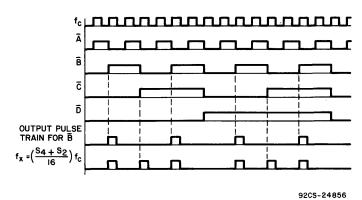

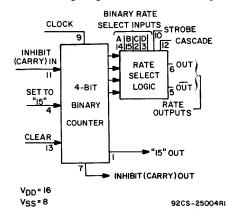

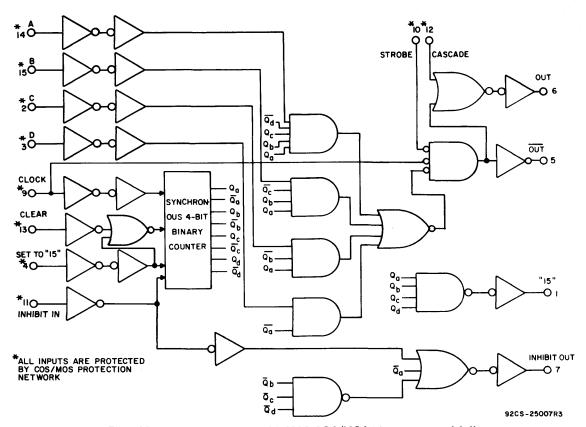

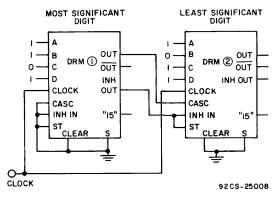

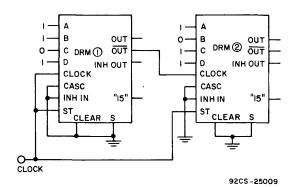

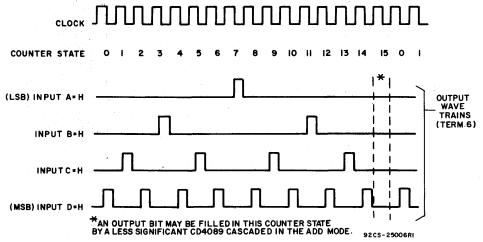

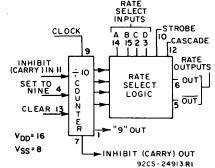

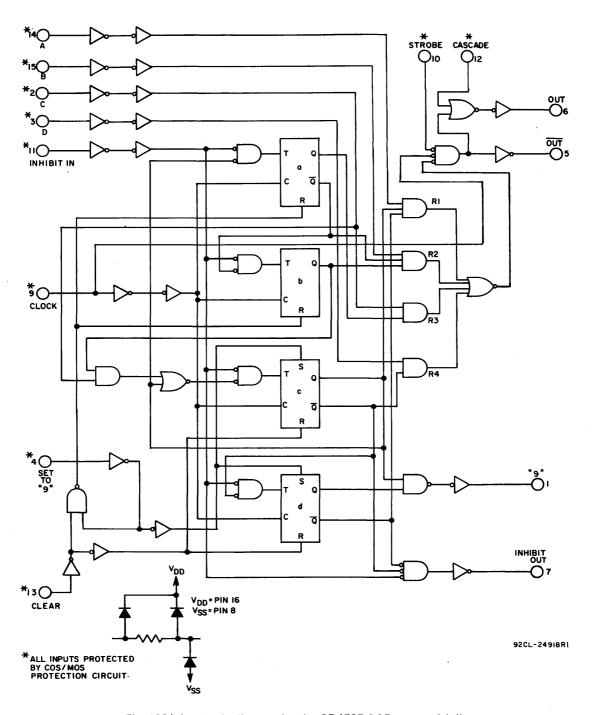

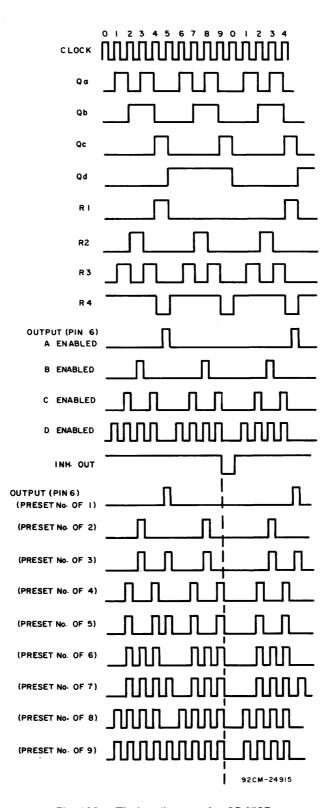

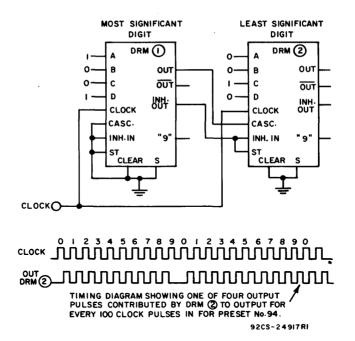

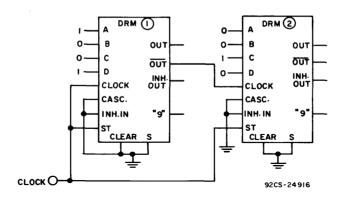

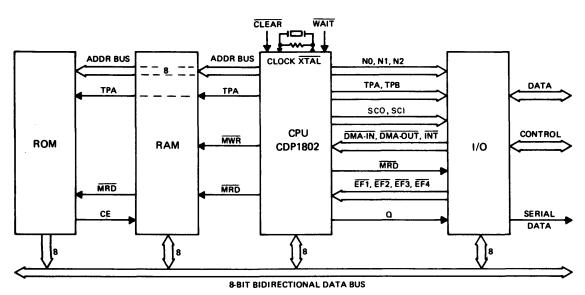

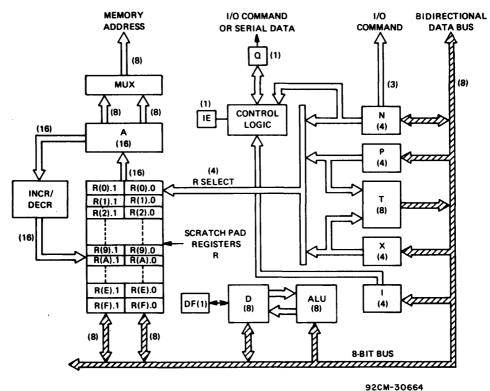

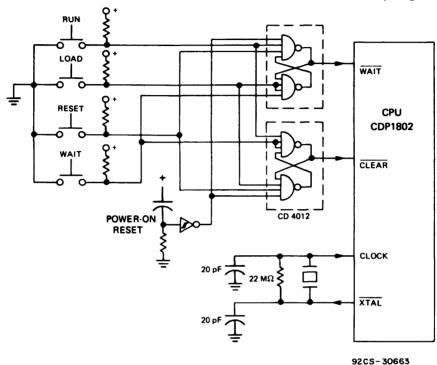

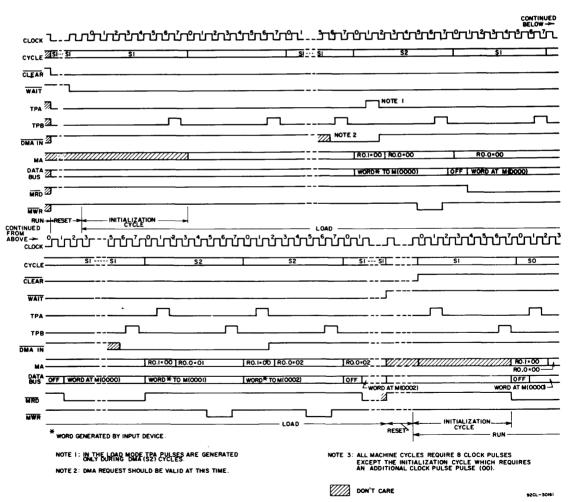

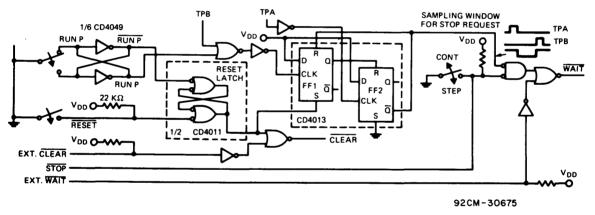

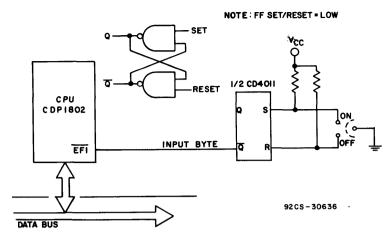

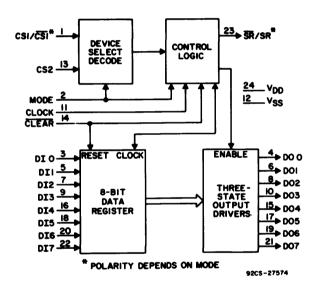

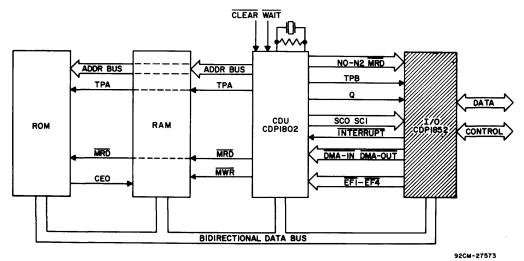

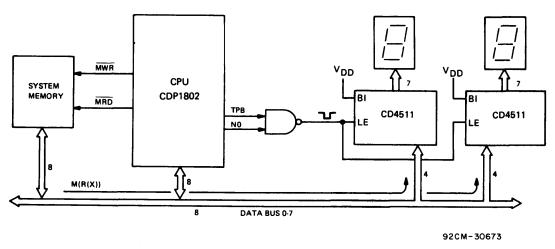

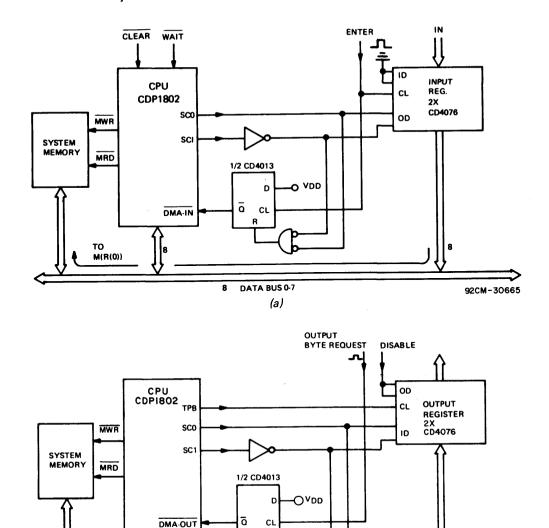

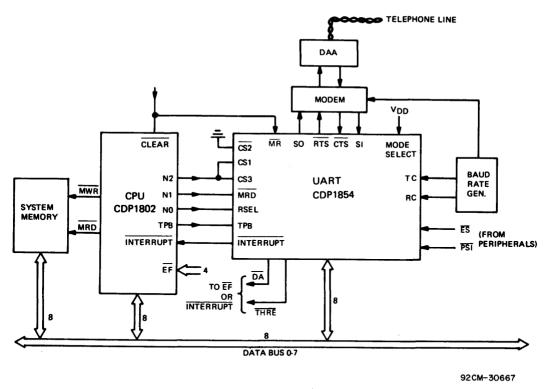

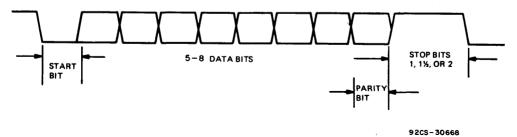

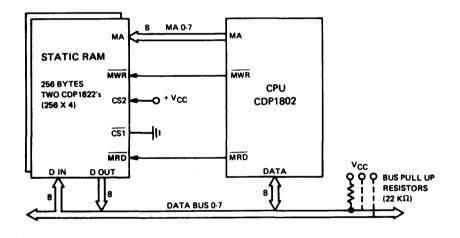

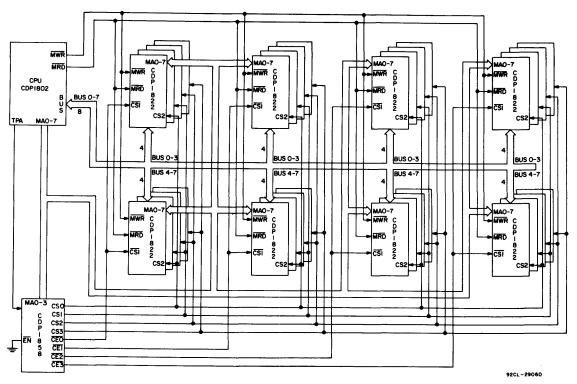

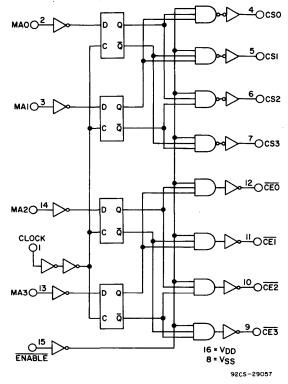

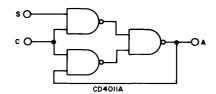

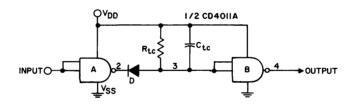

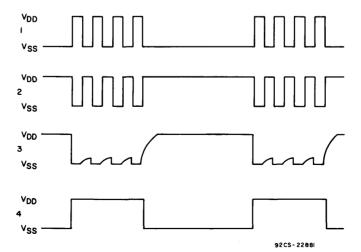

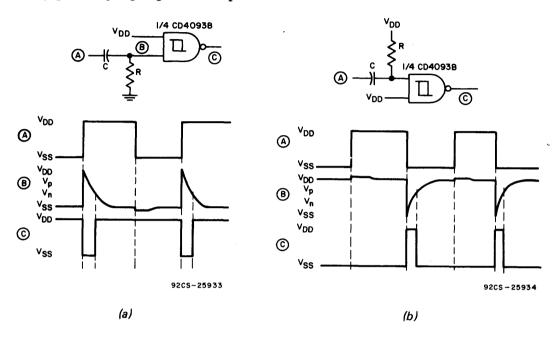

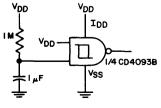

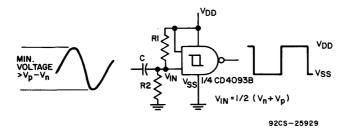

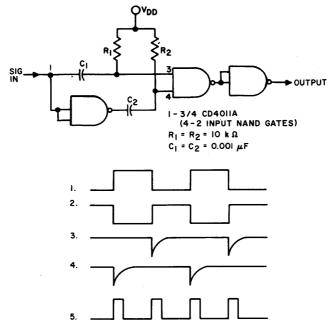

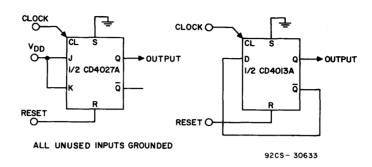

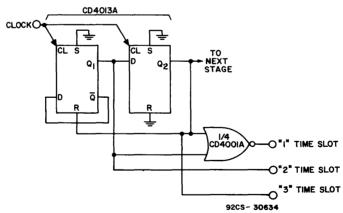

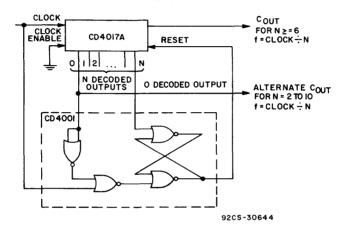

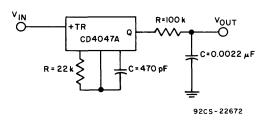

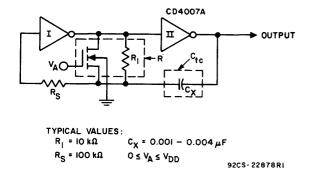

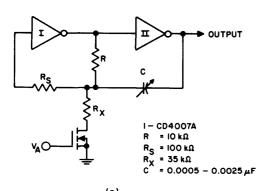

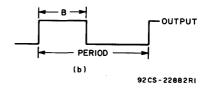

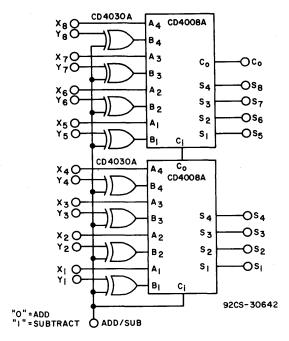

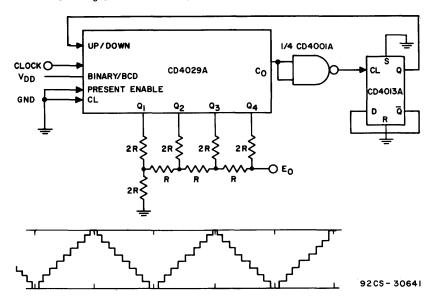

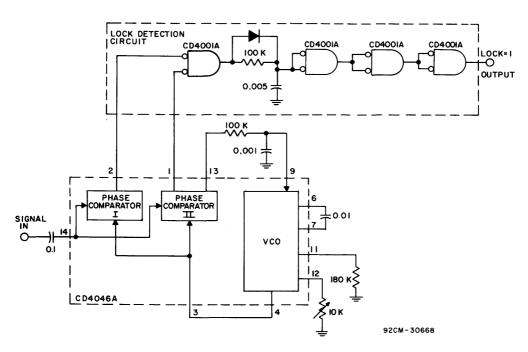

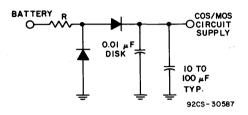

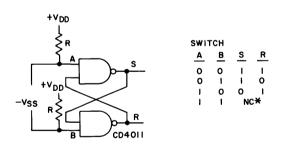

| CD40328                | 10201020              | 1                    | 1                   |                                      | 1                     | 1                   | 1                  | 1                 |