Edited by Bill Travis

## **Circuit provides cold-junction compensation**

Mark Maddox, Analog Devices, Wilmington, MA, and John Wynne, Analog Devices, Limerick, Ireland

HE ACCURACY OF ANY CIRCUIT OF SYStem that uses a thermocouple to determine the temperature of a process is limited by the accuracy of the method used to perform coldjunction compensation. In a thermocouple measurement, two wires of dissimilar metal join together at the "hot," or measurement, junction. The isothermal termination of the thermocouple wires provides a second "cold," or reference, junction. The potential across the thermocouple is proportional to the temperature difference between the two junctions. Thus, to determine the absolute temperature of the hot junction, you must also know the absolute temperature of the cold junction. Tables of thermocouple voltage versus temperature use the assumption that the cold junction is maintained at 0°C. A somewhat impractical way to use these tables is to place the cold junction into an ice bath. A more practical way is to measure the temperature of the cold junction and then add an equivalent voltage to the one developed by the hot junction. You then find the

| Circuit provides cold-junction compensation                  | 93  |

|--------------------------------------------------------------|-----|

| Solve low-frequency-cutoff problems<br>in capacitive sensors | 94  |

| Noninverting op-amp circuit<br>has simple gain formula       | 98  |

| Controller IC and one-shot<br>form resonant controller       | 100 |

| Circuit folds back current<br>during fault conditions        | 102 |

ideas

This circuit provides accurate cold-junction compensation in temperature-measurement systems.

temperature of the hot junction in the thermocouple tables.

A key issue to address is how to thermally bond the RTDs (resistance-temperature detectors) to the terminal block, which is the cold junction. If the temperature along the terminal block is constant, you could use a single sensor, thermally bonded to the block. If a linear temperature gradient exists along the terminal block, you could use a sensor at both ends of the block. This method allows for interpolation of the temperature at various points along the block. If the temperature gradient is nonlinear, you can add an electrically isolated copper strip along the length of the block to minimize the nonlinearity. In the extreme case, you could use a temperature sensor per thermocouple pair with each sensor, thermally bonded to its respective junction.

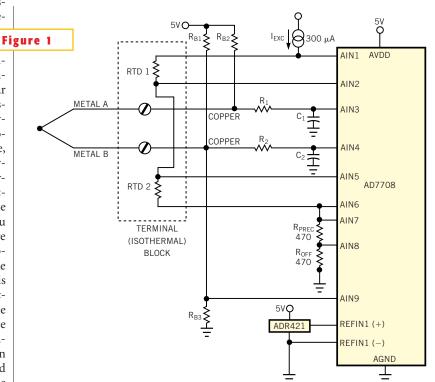

The design in **Figure 1** uses a multichannel, high-resolution ADC to measure the thermocouple voltage and the resistance of two RTDs at the cold junction. Using the data from the ADC, a microprocessor determines the temperature of

the cold junction, the amount of coldjunction compensation to apply, and, then, the temperature of the hot junction. Performing the cold-junction compensation in software allows users to use mixed thermocouple types and is both flexible and universal. The AD7708 digitizes the signals from the thermocouple and from two three-wire RTD sensors, which measure the cold-junction temperature at both ends of the terminal block. The terminal block is local, so you can ignore the wiring resistance between the ADC and the RTDs. It is easier to obtain precision resistors and voltage references than precision current sources, so the RTDs and the 470 $\Omega$  precision resistor, R<sub>PREC</sub>, connect in series, and all obtain excitation from the same current source,  $I_{EXC}$ . The voltage generated across  $R_{PREC}$ determines the exact value of the excitation current. Hence, the current source need not be particularly stable over temperature. R<sub>OFF</sub> offsets input pair AIN7/-AIN8 by more than 100 mV from ground.  $R_{OFF}$  is also a 470 $\Omega$  resistor but need not be a precision resistor. The ADR421's 2.5V precision voltage reference directly drives the REFIN1(+)/REF-IN1(-) inputs.

With  $I_{EXC}$  set to 300 µA and the internal programmable-gain amplifier set to the 40-mV full-scale range, the ADC produces usable resolution of 2.4 µV. With 100 $\Omega$  RTDs, it accurately resolves a 0.02°C temperature differential between the two ends of the terminal block and has an absolute accuracy of ±0.01°C for either measurement. The differential analog input pair, AIN1/AIN2, of the AD7708 reads an input voltage equal to I<sub>EXC</sub>(RTD 1), where RTD 1 represents the resistance of the first RTD element. A sec-

ond differential input pair, AIN5/AIN6, reads an input voltage equal to I<sub>EXC</sub>(RTD 2), where RTD 2 represents the resistance of the second RTD element. One source of error pertains to the RTDs themselves. The most common type is the  $100\Omega$  platinum RTD with a resistance-temperature coefficient of  $0.00385\Omega/\Omega/^{\circ}C$ . It is available in accuracy-tolerance classes A and B (or DIN A and DIN B), which specify both the initial accuracy at 0°C and the interchangeability over the operating range. The Class A specification is  $\pm (0.15 \pm 0.002 |t|)$ , where t is the specified interchangeability temperature; the Class B specification is  $\pm (0.3 \pm 0.005 |t|)$ .

It is possible to buy two Class A,  $100\Omega$ platinum RTDs from the same manufacturer and find that one is reading 0.2°C high at 25°C and the other is reading 0.2°C low at 25°C. Thus, you have an apparent 0.4°C difference before you even commission t. One way to combat this initial error is to request a matched pair of RTDs from the manufacturer. Leading RTD manufacturer Heraeus Sensor (www.4hcd.com) makes available PRTDs (platinum RTDs) that Heraeus sorts into tolerance groups with maximum  $\Delta t$  $=\pm 0.05^{\circ}$ C over 0 to 100°C. A lower cost solution and one that uses off-the-shelf RTDs is to use the offset and gain registers on the AD7708 ADC to calibrate each of the RTD errors. Noise pickup may be an issue if the hot junction of the thermocouple is a long distance from the measurement electronics. The very-highinput-impedance buffer inside the AD7708 allows the addition of lowpass filters R<sub>1</sub>-C<sub>1</sub> and R<sub>2</sub>-C<sub>2</sub> to the AIN3/AIN4 inputs to attenuate high-frequency-noise pickup in the wiring.

A single-ended analog-input channel,

AIN9, and three burnout resistors,  $R_{B1}$  through  $R_{B3}$ , provide both thermocouple open-circuit, or burnout, and short-circuit-detection functions by forcing the dc bias levels of AIN3/AIN4 away from their normal operating levels of approximately 2.5V. A thermocouple short-circuit fault condition from either Metal A or Metal B to ground pulls the voltage across  $R_{B3}$  to 0V. A thermocouple open-circuit fault condition on either Metal A or Metal B causes the voltage across  $R_{B3}$  to move to 1.66V. You can program either of these voltage levels (converted by AIN9) to raise an alarm signal.

A more difficult fault condition to detect is the condition in which the two thermocouple wires short only to each other. In this case, a new thermocouple junction forms at the location of the short circuit, and the junction behaves like a normal thermocouple. The only way to detect this fault condition is to implement a rate-of-change alarm in software. If the two wires short together at the exit of the thermo-well, the new thermocouple junction may well experience much the same temperature that the original thermocouple junction experienced. This fault condition is difficult to spot. However, if the short circuit occurs a long distance from the original thermocouple junction, then this new junction may be at a different temperature from that of the original junction and produces a rate of change that channel does not normally see. You can use this abnormal change to flag an alarm condition.

Is this the best Design Idea in this issue? Select at www.edn.com.

# Solve low-frequency-cutoff problems in capacitive sensors

Julius Foit, Czech Technical University, Prague, Czech Republic

**O** NE OF THE FIRST PROBLEMS a capacitive-sensor analog designer must face is the low-frequency cutoff. Theoretically, you must fulfill just one simple requirement: a sufficiently large input resistance of the preamplifier's first stage. In practice, however, many problems lurk behind the seemingly straightforward design rules. First, the preamplifier's active device must have a defined dc operating point. Using field-effect devices renders the dc input current of the first active device (a JFET or a MOSFET) so low that you can neglect it in most cases. On the other hand, the circuit must

have some dc-path-creating resistor to present the required dc potential to the input electrode. Assuming that a typical miniature capacitive sensor, such as a high-quality capacitive microphone, has a small capacitance of 20 to 50 pF, for example, the resistor value to obtain a cutoff frequency as high as 50 Hz would be on the order of 108 to  $10^{9}\Omega$ . Resistors with such high values are difficult to find in SMD formats, are expensive, have poor accuracy and stability, and are large and noisy. Moreover, further difficulties appear when the capacitive sensor requires an external polarization voltage. Such a polarization voltage may have a value of 100V or more. This voltage must connect to the sensor via a separate circuit, and it sometimes creates problems if the need to have at least one side of the sensor

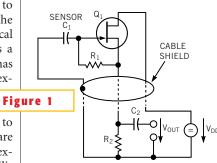

grounded emerges. And, as in all similar cases, the preamplifier should be as close to the sensor as possible. It should consume minimal space, need few connecting leads, and produce as little heat as possible. The circuit in **Figure 1** represents one possible approach to meeting these challenges.

The circuit uses electronic multiplication of the gate resistor,  $R_1$ , value via positive feedback through the source-follower action of JFET  $Q_1$ . The multiplication factor is  $\alpha = g_{fs}R_2$ . (Note:  $g_{fs}$  is the real part of the differential forward transfer admittance in common-source connection.) Assuming a typical value of  $C_1=33$  pF, reasonable values of  $R_1=10$  M $\Omega$  and  $R_2=10$  k $\Omega$  and assuming a conservative value of  $g_{fs}=5$ mA/V (typical in the JFET type BF245B at  $V_{GS}=0V$  and  $V_{DS}=15V$ ), you obtain the following low-frequency cutoff:

$$f_{\rm L} = \frac{1}{2\pi C_1 R_1 g_{\rm fs} R_2} = 9.6 \text{ Hz}.$$

With this method, notwithstanding the extremely small sensor capacitance and conservative values of all other components, you obtain a respectable cutoff frequency. At the same time, to get the required high polarizing voltage to the sensor while keeping one side connected directly to ground, you can use a supply voltage,  $V_{DD}=V_{DS}+V_{POLARIZING}=115V$ , where  $V_{POLARIZING}=I_DR_2$ , and  $I_D$  is the JFET's drain current at the selected  $V_{DS}$

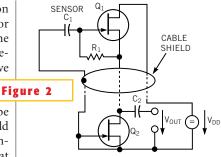

The second JFET,  $Q_{2'}$  in this circuit replaces  $R_{2}$  in the circuit of Figure 1.

An operational amplifier provides yet another means to achieve high impedance for capacitive sensors.

and  $V_{GS}$ =0. Thus, you provide a polarizing voltage of 100V to the sensor. Other advantages of the circuit are obvious at the first glance: Only two elements of the circuit, R<sub>1</sub> and Q<sub>1</sub>, must be connected directly at the sensor's location. Both these components are readily available, and they are physically small (usually considerably smaller than the sensor itself), so they pose no space problems. The heat the JFET produces—150 mW—is low enough to be negligible in most applications. The circuit needs only three wires for connection, and one of them can also serve as cable shielding. The connecting cable can be quite long; its maximum length is limited primarily by its capacitance, which determines the upper cutoff frequency. In most applications, the upper cutoff frequency of the sensor itself is low enough to permit a rather long cable. The only minor disadvantage of the circuit lies in its total power consumption, mostly dissipated in  $R_2$  (1W in this case).

In cases not requiring a high polarizing voltage, the value of R<sub>2</sub> might become too small to obtain a sufficiently large multiplication factor,  $\alpha$ . Then, another JFET,  $Q_2$ , can replace  $R_2$  (**Figure 2**). This JFET has its gate shorted to its source and operates as a constant-current source. You can calculate the R<sub>1</sub> multiplication factor  $\alpha$  from the same formula as for Figure 1, with the R<sub>2</sub> value replaced by the value of  $R_{OUTQ2} = 1/g_{DSQ2}$ . You must lower the overall supply voltage,  $V_{DD}$ , accordingly to provide the same operating point for Q<sub>1</sub>. The processing stage, the amplifying stage, or both immediately following the preamplifier should not have too small a differential input resistance; this resistance appears in parallel with  $R_2$  or  $Q_2$ , so it reduces the multiplication factor, a. A noninverting input of an operational amplifier easily satisfies this requirement.

Choosing a less common but still reasonable value of  $R_1 = 100 \text{ M}\Omega$  pushes the low-frequency cutoff below 1 Hz with no other changes in the circuit necessary. The dynamic range of the preamplifier is respectable. The maximum permissible positive swing of the input voltage is equal to the forward threshold voltage of Q<sub>1</sub>'s gate-insulating pn junction multiplied by the same multiplication factor,  $\alpha$ , as the input resistance. In the circuit of Figure 1, with the cited component values, at a 300K temperature and  $V_{cc} = 115$ V, the permissible swing exceeds 5V peak. The JFET alone determines the noise figure; hence, it is rather low. The maximum permissible negative swing of the input voltage is usually much larger. A second possible solution of the low-frequency-cutoff problem in capacitive-sensor analog preamplifiers appears in the case of electret-biased sensors. These sensors need no external polarizing voltage, thus simplifying the overall power-sup-

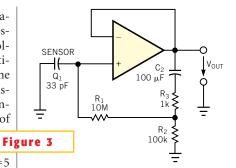

ply design. In these cases, you can achieve an even larger multiplication factor of the biasing resistance by applying unity positive voltage feedback in an operational amplifier (Figure 3).

To obtain a full unity positive voltage feedback in the circuit, the value of R, should be zero. A minor complication exists, however. To prevent dc instability (bistable flip-flop behavior), a dc path in the positive-feedback circuit must not exist. C<sub>2</sub> is the dc-blocking device. Unfortunately, C<sub>2</sub> introduces another pole in the transfer function of the circuit. To render its effects negligible, C<sub>2</sub> would need an uncomfortably large value. As long as you are prepared to sacrifice a bit of the otherwise extremely large R<sub>1</sub>-value multiplication factor,  $\alpha$  (theoretically equal to the open-loop voltage gain of the operational amplifier, or 105, typically), you can use a C<sub>2</sub> value several orders of magnitude smaller under the condition that doing so introduces some additional damping into the circuit by means of a nonzero value of R<sub>3</sub>. R<sub>2</sub> is necessary to provide a correct dc potential (quiescent operating-point conditions) for the noninverting input of the operational amplifier.

A detailed analysis of the circuit in terms of stability and its response to harmonic and step-signal drive is rather lengthy. You can base the analysis on the rules of general active-filter theory, or you can simulate the circuit behavior with any of the common simulation tools, such as Spice. By an intelligent choice of passive-component values, you can easily control the circuit's behavior in terms of low-frequency cutoff. Thus, you can obtain a maximally flat frequency response or a maximally flat transient response or set a predetermined amount of overshoot in the response to a step input, for example. The operational amplifier must have quiescent dc currents of both inputs as low as possible. CMOS op amps are best in this respect. The circuit of Figure 3 requires a somewhat larger space for components in the immediate vicinity of the sensor,

as well as four instead of three connecting leads. On the other hand, it is less sensitive to external loads than are the circuits in figures 1 or 2.

The op amp in **Figure 3** is a TS271, a CMOS op amp from STMicroelectronics (www.stmicroelectronics.com). The low-frequency cutoff is at 7 Hz, and the step-response overshoot is 0%. With larger values of C<sub>2</sub> and smaller values of R<sub>2</sub>, you can easily achieve a low-frequency cutoff of 0.1 Hz or lower. The circuit in Figure 3 is well-suited for micropower applications. Using a micropower CMOS operational amplifier, you can reliably obtain 10 years of unattended operation with standard passive components and just a single coin-sized lithium cell as the power source. The properties of the operational amplifier fully determine the high frequency cutoff and dynamic range of the circuit in Figure 3.

Is this the best Design Idea in this issue? Select at www.edn.com.

#### Noninverting op-amp circuit has simple gain formula

José Carrasco and Ausias Garrigós, Universidad Miguel Hernández, Elche, Spain

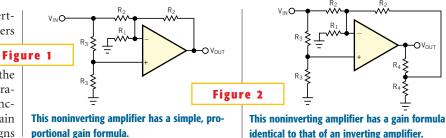

ASIC TEXTBOOKS DESCRIBE invert-ing and noninverting amplifiers D based on operational amplifiers. These amplifiers have different gain equations. Whereas in the inverting configuration, the gain is the ratio of the feedback and input resistances, in the noninverting amplifier, the gain ratio has an added term. In some designs and for the sake of simplicity, it would be desirable to have a simple, proportional gain ratio (for gains above and below unity) for both inverting and noninverting amplifiers. The noninverting amplifier in Figure 1 has a simple, proportional formula for the gain: V<sub>OUT</sub>=  $V_{IN}(R_2/2R_1)$ . This gain is proportional to a resistor ratio and can take any value. R<sub>3</sub> has no influence on the gain. If you need a noninverting amplifier with a gain ratio identical to that of an inverting am-

plifier, the circuit in Figure 2 fills the bill. Its close-approximation gain formula is  $V_{0UT} = V_{1N}(R_2/R_1).$

However, in the circuit of Figure 2, some restrictions in the choice of  $R_4$  arise. The accuracy of the gain formula of the circuit depends on R<sub>4</sub>'s being much lower in value than R<sub>1</sub> or R<sub>2</sub>. Nevertheless, comparing the exact expression for the gain and the above approximation proves that  $R_4$  is 10 times lower in value than  $R_1$

identical to that of an inverting amplifier.

or R<sub>2</sub>, whichever is smaller, and the gain error the approximation gives is less than 5%. For an exact computation, the error is equal to  $R_a/2 \times (1/R_1 - 1/R_2)$ . For the selection of R<sub>4</sub>, you should take into account the fact that most op-amp ICs have maximum output currents of approximately 20 mA.

Is this the best Design Idea in this issue? Select at www.edn.com.

## Controller IC and one-shot form resonant controller

C Rajan, Centre for Advanced Technology, Indore, India

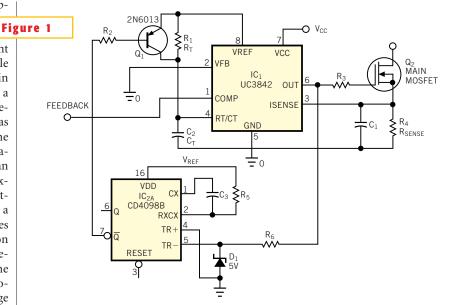

ESONANT POWER SUPPLIES are popular because of high efficiency, low noise, and compactness. You can implement a resonant buck or boost converter using a single switch. The regulation of the output in such a converter derives from using a constant on or off time and a variable frequency. The UC1864 controller IC (Texas Instruments, www.ti.com) meets all the requirements for a single-switch quasiresonant converter. But you also can achieve this performance with the inexpensive and popular UC3842 currentmode controller in conjunction with a one-shot multivibrator. This circuit gives the desired current-mode operation along with constant off-time, variablefrequency operation. Figure 1 shows the controller circuit, configured as a resonant flyback converter for high-voltage generation. For the implementation of this function, the current-mode controller should have 100% duty cycle; thus,

you can use the UC3842 or 3843. This circuit uses the 3842. The operation of the circuit is as follows.

The output of IC<sub>1</sub>, the UC3842, is in a high state until the internal current-sense comparator goes high, and then the output of the IC switches low. As the output voltage goes low, IC,, the negative-edgetriggered one-shot CD4098B, triggers, and it generates a pulse. The pulse duration is a function of the values of  $R_5$  and C<sub>3</sub>, and this time interval is the constant off-time of the UC3842. The  $\overline{Q}$  output of the one-shot sinks the base current of transistor Q<sub>1</sub> during this period, and so the transistor conducts. This action adds a 5V pulse to the ramp at the RT/CT pin (Pin 4). This voltage remains at 5V until the pulse ends and  $\overline{Q}$  goes high. As it goes high, Q, turns off, but the voltage across CT is 5V, which is higher than the upper threshold of the RT/CT pin, so the internal circuitry pulls the pin's voltage to zero, and a fresh ramp and a fresh cycle start.

You must select RT and CT in such a

This resonant flyback configuration uses only a controller IC and a one-shot multivibrator.

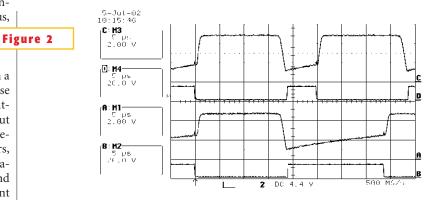

These waveforms typify operation at low (traces C and D) and high (traces A and B) duty cycles.

way that the output voltage goes low before the ramp voltage reaches its upperthreshold level. If not, a glitch can occur in the output, arising from the time constant consisting of the output resistance of  $Q_2$  and CT. **Figure 2** shows the voltage waveforms at low and high duty cycles. Traces D and C show the output and RT/CT-pin voltages, respectively, at a low duty cycle and, hence, high frequency. Traces B and A show the same voltages, but at a higher duty cycle (low frequency). You can see that the off-time is fixed in both conditions, and only the frequency changes to achieve the desired duty cycle. The voltage at the RT/CT pin gives a clear view of how the circuit modifies the ramp. This control circuit generates a 2-kV, 5-mA dc power supply using a resonant flyback scheme, and it performs well.

Is this the best Design Idea in this issue? Select at www.edn.com.

### **Circuit folds back current during fault conditions**

Martin Galinski, Micrel Semiconductor, San Jose, CA

OU CAN USE monolithic linear regulators at currents lower than 5A for most applications. Most manufacturers of these devices integrate currentlimiting and thermal shutdown to prevent damage during fault conditions. For currents greater than 5A, most linear supplies use controllers that allow the user to select the pass element to handle different current requirements. Although these linear controllers may offer current limiting, they generally don't support thermal shutdown. This limitation requires the design to handle the maximum power dissipation and maintain an acceptable junction temperature in the pass element. For example, assume that you use a 1.8V, 8A linear supply operating from a 2.5V rail. The power dissipation in the pass element equals  $(V_{IN} - V_{OUT}) \times I_{OUT} = (2.5V - 1.8V) \times 8A = 5.6W$ . Over the specified temperature range, the pass element must be able to dissipate this amount of power and have a junction temperature lower than the maximum allowable for that device. This approach probably requires three to four D-Pack-size MOSFETS. A big problem arises when you examine power dissipation in a sustained short circuit. Then, the pass element must accommodate 20W of dissipation. It would require 10 D-Pack-size MOSFETs to maintain an acceptable junction temperature. Thus, you must overdesign the supply, increasing cost and board size to

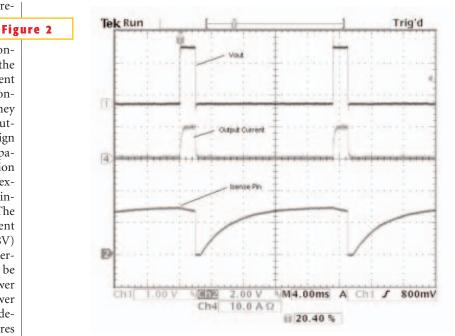

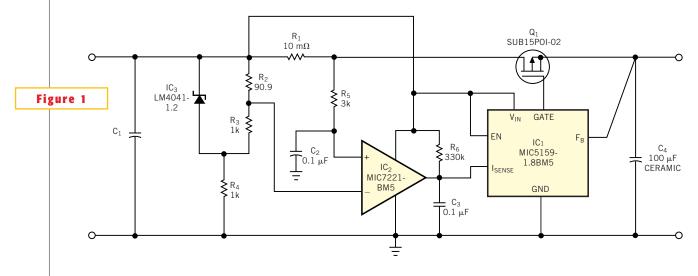

The circuit in Figure 1 cycles current in the event of a fault condition.

This circuit provides foldback current-limiting, thus reducing the power-handling requirements of the pass element.

survive a possible fault condition. The circuit in **Figure 1** solves the problem of current-limit power dissipation.

The circuit uses a separate control loop that "folds back" the currents during a fault condition without involving the problems of linear-foldback current limiting. Linear foldback can have problems tripping the current limit during start-up and returning to full load after a fault condition disappears. These problems tend to lock up the regulator in currentlimited state. IC, provides a high-side reference below the supply voltage and places this voltage on the inverting pin of comparator IC<sub>2</sub>. The comparator compares this reference signal with the MOS-FET side of R<sub>1</sub>. When the current exceeds the current-limit threshold, IC<sub>2</sub>'s inverting-input voltage is greater than that of the noninverting input. This state causes the comparator to pull the currentsense pin on IC, low. You can calculate

the current-limit threshold as follows:

CURRENT LIMIT =

$$\frac{V_{IN} - \left(V_{IC3} \times \frac{R_2}{R_2 + R_3}\right)}{R_1};$$

CURRENT LIMIT =

$$\frac{2.5 - \left(1.225 \times \frac{90.9}{90.9 + 1000}\right)}{10 \text{ m}\Omega};$$

#### CURRENT LIMIT=10.207A.

When the current-sense pin drops 50 mV below the input, the regulator turns the output off. This action then causes the current to go to zero, creating a high condition on the output of the comparator. The comparator has an open collector; therefore, the  $I_{SENSE}$  pin charges at the RC charge rate of  $R_6$  and  $C_3$ . The output of the regulator remains off, drawing no current, until the  $I_{SENSE}$  pin charges to 50 mV below  $V_{IN}$ . At this point, the output turns on.  $R_5$  and  $C_2$  provide a delay before re-engaging the current limit.

This delay prevents the current required for charging the output capacitors from prematurely tripping the current limit. It also gives the circuit time to stabilize and to determine whether it can deliver the output current that the load demands. If the load is still too heavy, the current limit re-engages. Figure 2 is an oscilloscope photo of this circuit in operation. This cycling of current, although periodically delivering maximum current, integrates over time into a lower average current. You can calculate average current as a ratio of on- to off-time:  $I_{AVG} = I_{PK} \times$  $(T_{ON}/T_{OFF}) = 10.2A \times (2msec/17msec) =$ 1.2A. This reduced average current equates to a reduction in power dissipation. At 1.2A, the power dissipation decreases to 3W.

Is this the best Design Idea in this issue? Select at www.edn.com.