# IC Op Amp Beats FETs on Input Current

National Semiconductor Application Note 29 Robert J. Widlar September 2002

**Note:** National Semiconductor recommends replacing 2N2920 and 2N3728 matched pairs with LM394 in all application circuits.

mance is often limited by leakages in capacitors, diodes, analog switches or printed circuit boards, rather than by the op amp itself.

#### **Abstract**

A monolithic operational amplifier having input error currents in the order of 100 pA over a -55°C to 125°C temperature range is described. Instead of FETs, the circuit used bipolar transistors with current gains of 5000 so that offset voltage and drift are not degraded. A power consumption of 1 mW at low voltage is also featured.

A number of novel circuits that make use of the low current characteristics of the amplifier are given. Further, special design techniques required to take advantage of these low currents are explored. Component selection and the treatment of printed circuit boards is also covered.

### Introduction

A year ago, one of the loudest complaints heard about IC op amps was that their input currents were too high. This is no longer the case. Today ICs can provide the ultimate in performance for many applications—even surpassing FET amplifiers.

FET input stages have long been considered the best way to get low input currents in an op amp. Low-picoamp input currents can in fact be obtained at room temperature. However, this current, which is the leakage current of the gate junction, doubles every  $10^{\circ}$ C, so performance is severely degraded at high temperatures. Another disadvantage is that it is difficult to match FETs closely. Unless expensive selection and trimming techniques are used, typical offset voltages of 50 mV and drifts of 50  $\mu$ V/°C must be tolerated.

Super gain transistors  $^2$  are now challenging FETs. These devices are standard bipolar transistors which have been diffused for extremely high current gains. Typically, current gains of 5000 can be obtained at 1  $\mu$ A collector currents. This makes it possible to get input currents which are competitive with FETs. It is also possible to operate these transistors at zero collector base voltage, eliminating the leakage currents that plague the FET. Hence they can provide lower error currents at elevated temperatures. As a bonus, super gain transistors match much better than FETs with typical offset voltages of 1 mV and drifts of 3  $\mu$ V/ $^{\circ}$ C.

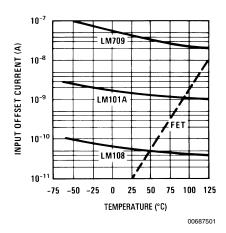

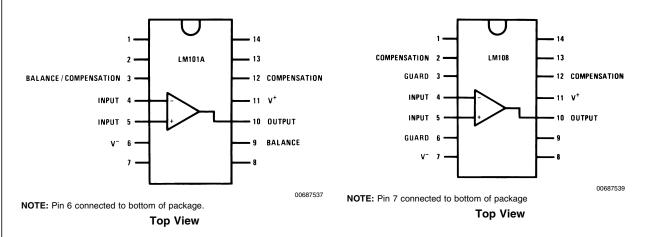

Figure 1 compares the typical input offset currents of IC op amps and FET amplifiers. Although FETs give superior performance at room temperature, their advantage is rapidly lost as temperature increases. Still, they are clearly better than early IC amplifiers like the LM709.<sup>3</sup> Improved devices, like the LM101A, <sup>4</sup> equal FET performance over a –55°C to 125°C temperature range. Yet they use standard transistors in the input stage. Super gain transistors can provide more than an order of magnitude improvement over the LM101A. The LM108 uses these to equal FET performance over a 0°C to 70°C temperature range.

In applications involving 125°C operation, the LM108 is about two orders of magnitude better than FETs. In fact, unless special precautions are taken, overall circuit perfor-

FIGURE 1. Comparing IC op Amps with FET-Input Amplifier

## **Effects of Error Current**

In an operational amplifier, the input current produces a voltage drop across the source resistance, causing a dc error. This effect can be minimized by operating the amplifier with equal resistances on the two inputs. The error is then proportional to the difference in the two input currents, or the offset current. Since the current gains of monolithic transistors tend to match well, the offset current is typically a factor of ten less than the input currents.

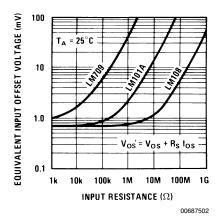

FIGURE 2. Illustrating the Effect of Source Resistance on Typical Input Error Voltage

Naturally, error current has the greatest effect in high impedance circuitry. Figure 2 illustrates this point. The offset voltage of the LM709 is degraded significantly with source resistances greater than 10 k $\Omega$ . With the LM101A this is

#### Effects of Error Current (Continued)

extended to source resistances high as 500 k $\Omega$ . The LM108, on the other hand, works well with source resistances above 10 M $\Omega$ .

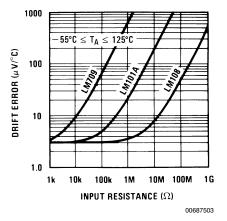

High source resistances have an even greater effect on the drift of an amplifier, as shown in *Figure 3*. The performance of the LM709 is worsened with sources greater than 3 k $\Omega$ . The LM101A holds out to 100 k $\Omega$  sources, while the LM108 still works well at 3 M $\Omega$ .

FIGURE 3. Degradation of Typical Drift Characteristics with High Source Resistances

It is difficult to include FET amplifiers in *Figure 3* because their drift is initially 50  $\mu\text{V/}^{\circ}\text{C}$ , unless they are selected and trimmed. Even though their drift may be well controlled (5  $\mu\text{V/}^{\circ}\text{C})$  over a limited temperature range, trimmed amplifiers generally exhibit a much higher drift over a –55°C to 125°C temperature range. At any rate, their average drift rate would, at best, be like that of the LM101A where 125°C operation is involved.

Applications that require low error currents include amplifiers for photodiodes or capacitive transducers, as these usually operate at megohm impedance levels. Sample and hold circuits, timers, integrators and analog memories also benefit from low error currents. For example, with the LM709, worst case drift rates for these kinds of circuits is in the order of 1.5 V/sec. The LM108 improves this to 3 mV/sec. - worst case over a -55°C to 125°C temperature range. Low input currents are also helpful in oscillators and active filters to get low frequency operation with reasonable capacitor values. The LM108 can be used at a frequency of 1 Hz with capacitors no larger than 0.01 µF. In logarithmic amplifiers, the dynamic range can be extended by nearly 60 dB by going from the LM709 to the LM108. In other applications, having low error currents often permits an entirely different design approach which can greatly simplify circuitry.

#### **The LM108**

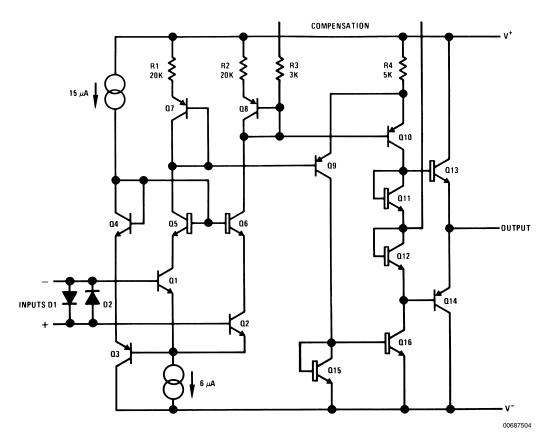

Figure 4 shows a simplified schematic of the LM108. Two kinds of NPN transistors are used on the IC chip: super gain (primary) transistors which have a current gain of 5000 with a breakdown voltage of 4V and conventional (secondary) transistors which have a current gain of 200 with an 80V breakdown. These are differentiated on the schematic by drawing the secondaries with a wider base.

Primary transistors ( $Q_1$  and  $Q_2$ ) are used for the input stage; and they are operated in a cascode connection with  $Q_5$  and  $Q_6$ . The bases of  $Q_5$  and  $Q_6$  are bootstrapped to the emitters of  $Q_1$  and  $Q_2$  through  $Q_3$  and  $Q_4$ , so that the input transistors are operated at zero collector-base voltage. Hence, circuit performance is not impaired by the low breakdown of the primaries, as the secondary transistors stand off the commom mode voltage. This configuration also improves the commom mode rejection since the input transistors do not see variations in the commom mode voltage. Further, because there is no voltage across their collector-base junctions, leakage currents in the input transistors are effectively eliminated

FIGURE 4. Simplified Schematic of the LM108

The second stage is a differential amplifier using high gain lateral PNPs  $(Q_9 \ \text{and} \ Q_{10}).^6$  These devices have current gains of 150 and a breakdown voltage of 80V.  $R_1$  and  $R_2$  are the collector load resistors for the input stage.  $Q_7$  and  $Q_8$  are diode connected laterals which compensate for the emitter-base voltage of the second stage so that its operating current is set at twice that of the input stage by  $R_4$ .

The second stage uses an active collector load ( $Q_{15}$  and  $Q_{16}$ ) to obtain high gain. It drives a complementary class-B output stage which gives a substantial load driving capability. The dead zone of the output stage is eliminated by biasing it on the verge of conduction with  $Q_{11}$  and  $Q_{12}$ .

Two methods of frequency compensation are available for the amplifier. In one a 30 pF capacitor is connected from the input to the output of the second stage (between the compensation terminals). This method is pin-compatible with the LM101 or LM101A. It can also be compensated by connecting a 100 pF capacitor from the output of the second stage to ground. This technique has the advantage of improving the high frequency power supply rejection by a factor of ten.

A complete schematic of the LM108 is given in the Appendix along with a description of the circuit. This includes such essential features as overload protection for the inputs and outputs.

### **Performance**

The primary design objective for the LM108 was to obtain very low input currents without sacrificing offset voltage or drift. A secondary objective was to reduce the power consumption. Speed was of little concern, as long as it was comparable with the LM709. This is logical as it is quite difficult to make high-impedance circuits fast; and low power circuits are very resistant to being made fast. In other respects, it was desirable to make the LM108 as much like the LM101A as possible.

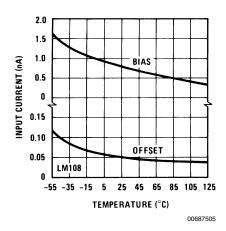

#### FIGURE 5. Input Currents

Figure 5 shows the input current characteristics of the LM108 over a -55°C to 125°C temperature range. Not only

#### Performance (Continued)

are the input currents low, but also they do not change radically over temperature. Hence, the device lends itself to relatively simple temperature compensation schemes, that will be described later.

There has been considerable discussion about using Darlington input stages rather than super gain transistors to obtain low input currents.<sup>6,7</sup> It is appropriate to make a few comments about that here.

Darlington inputs can give about the same input bias currents as super gain transistors—at room temperature. However, the bias current varies as the square of the transistor current gain. At low temperatures, super gain devices have a decided advantage. Additionally, the offset current of super gain transistors is considerably lower than Darlingtons, when measured as a percentage of bias current. Further, the offset voltage and offset voltage drift of Darlington transistors is both higher and more unpredictable.

Experience seems to tell the real truth about Darlingtons. Quite a few op amps with Darlington input stages have been introduced. However, none have become industry standards. The reason is that they are more sensitive to variations in the manufacturing process. Therefore, satisfactory performance specifications can only be obtained by sacrificing the manufacturing yield.

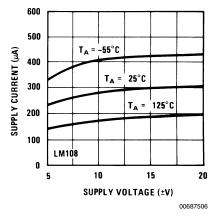

FIGURE 6. Supply Current

The supply current of the LM108 is plotted as a function of supply voltage in *Figure 6*. The operating current is about an order of magnitude lower than devices like the LM709. Furthermore, it does not vary radically with supply voltage which means that the device performance is maintained at low voltages and power consumption is held down at high voltages.

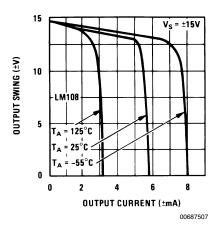

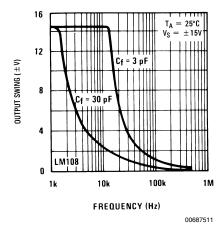

FIGURE 7. Output Swing

The output drive capability of the circuit is illustrated in Figure 7. The output swings to within a volt of the supplies, which is especially important when operating at low voltages. The output falls off rapidly as the current increases above a certain level and the short circuit protection goes into effect. The useful output drive is limited to about  $\pm 2$  mA. It could have been increased by the addition of Darlington transistors on the output, but this would have restricted the voltage swing at low supply voltages. The amplifier, incidentally, works with common mode signals to within a volt of the supplies so it can be used with supply voltages as low as  $\pm 2V$ .

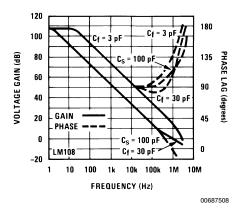

FIGURE 8. Open Loop Frequency Response

The open loop frequency response, plotted in Figure 8, indicates that the frequency response is about the same as

www.national.com

4

#### Performance (Continued)

that of the LM709 or the LM101A. Curves are given for the two compensation circuits shown in *Figure 9*. The standard compensation is identical to that of the LM101 or LM101A. The alternate compensation scheme gives much better rejection of high frequency power supply noise, as will be shown later.

$C_f \ge \frac{R1 C_o}{R1 + R}$   $C_o = 30 pF$

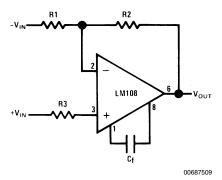

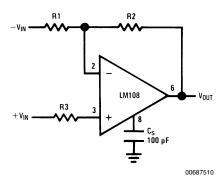

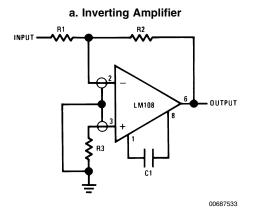

#### a. Standard Compensation Circuit

b. Alternate Compensation Circuit

#### FIGURE 9. Compensation Circuits

With unity gain compensation, both methods give a 75-degree stability margin. However, the shunt compensation has a 300 kHz small signal bandwidth as opposed to 1 MHz for the other scheme. Because the compensation capacitor is not included on the IC chip, it can be tailored to fit the application. When the amplifier is used only at low frequencies, the compensation capacitor can be increased to give a greater stability margin. This makes the circuit less sensitive to capacitive loading, stray capacitances or improper supply bypassing. Overcompensating also reduces the high frequency noise output of the amplifier.

With closed-loop gains greater than one, the high frequency performance can be optimized by making the compensation capacitor smaller. If unity-gain compensation is used for an amplifier with a gain of ten, the gain error will exceed 1-percent at frequencies above 400 Hz. This can be extended to 4 kHz by reducing the compensation capacitor to 3 pF. The formula for determining the minimum capacitor value is given in Figure 9a. It should be noted that the capacitor value does not really depend on the closed-loop gain. Instead, it depends on the high frequency attenuation in the feedback networks and, therefore, the values of  $\rm R_1$  and  $\rm R_2$ . When it is desirable to optimize performance at high frequencies, the standard compensation should be used. With small capacitor values, the stability margin obtained with shunt compensation is inadequate for conservative designs.

The frequency response of an operational amplifier is considerably different for large output signals than it is for small signals. This is indicated in *Figure 10*. With unity-gain compensation, the small signal bandwidth of the LM108 is 1 MHz. Yet full output swing cannot be obtained above 2 kHz. This corresponds to a slew rate of 0.3 V/µs. Both the full-output bandwidth and the slew rate can be increased by using smaller compensation capacitors, as is indicated in the figure. However, this is only applicable for higher closed loop gains. The results plotted in *Figure 10* are for standard compensations. With unity gain compensation, the same curves are obtained for the shunt compensation scheme.

Classical op amp theory establishes output resistance as an important design parameter. This is not true for IC op amps: The output resistance of most devices is low enough that it can be ignored, because they use class-B output stages. At low frequencies, thermal feedback between the output and input stages determines the effective output resistance, and this cannot be accounted for by conventional design theories. Semiconductor manufacturers take care of this by specifying the gain under full load conditions, which combines output resistance with gain as far as it affects overall circuit performance. This avoids the fictitious problem that can be created by an amplifier with infinite gain, which is good, that will cause the open loop output resistance to appear infinite, which is bad, although none of this affects overall performance significantly.

FIGURE 10. Large Signal Frequency Response

## Performance (Continued)

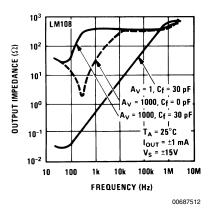

FIGURE 11. Closed Loop Output Impedance

The closed loop output impedance is, nonetheless, important in some applications. This is plotted for several operating conditions in Figure 11. It can be seen that the output impedance rises to about  $500\Omega$  at high frequencies. The increase occurs because the compensation capacitor rolls off the open loop gain. The output resistance can be reduced at the intermediate frequencies, for closed loop gains greater than one, by making the capacitor smaller. This is made apparent in the figure by comparing the output resistance with and without frequency compensation for a closed loop gain of 1000.

The output resistance also tends to increase at low frequencies. Thermal feedback is responsible for this phenomenon. The data for *Figure 11* was taken under large-signal conditions with  $\pm 15 \text{V}$  supplies, the output at zero and  $\pm 1$  mA current swing. Hence, the thermal feedback is accentuated more than would be the case for most applications.

In an op amp, it is desirable that performance be unaffected by variations in supply voltage. IC amplifiers are generally better than discretes in this respect because it is necessary for one single design to cover a wide range of uses. The LM108 has a power supply rejection which is typically in excess of 100 dB, and it will operate with supply voltages from ±2V to ±20V. Therefore, well-regulated supplies are unnecessary, for most applications, because a 20-percent variation has little effect on performance.

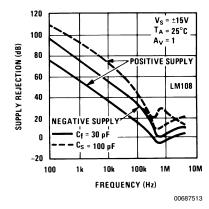

The story is different for high-frequency noise on the supplies, as is evident from *Figure 12*. Above 1 MHz, practically all the noise is fed through to the output. The figure also demonstrates that shunt compensation is about ten times better at rejecting high frequency noise than is standard compensation. This difference is even more pronounced

with larger capacitor values. The shunt compensation has the added advantage that it makes the circuit virtually unaffected by the lack of supply bypassing.

FIGURE 12. Power Supply Rejection

Power supply rejection is defined as the ratio of the change in offset voltage to the change in the supply voltage producing it. Using this definition, the rejection at low frequencies is unaffected by the closed loop gain. However, at high frequencies, the opposite is true. The high frequency rejection is increased by the closed loop gain. Hence, an amplifier with a gain of ten will have an order of magnitude better rejection than that shown in *Figure 12* in the vicinity of 100 kHz to 1 MHz.

The overall performance of the LM108 is summarized in Table 1\*. It is apparent from the table and the previous discussion that the device is ideally suited for applications that require low input currents or reduced power consumption. The speed of the amplifier is not spectacular, but this is not usually a problem in high-impedance circuitry. Further, the reduced high frequency performance makes the amplifier easier to use in that less attention need be paid to capacitive loading, stray capacitances and supply bypassing

Note: \*See Appendix Heading in This Application Note.

## **Applications**

Because of its low input current the LM108 opens up many new design possibilities. However, extra care must be taken in component selection and the assembly of printed circuit boards to take full advantage of its performance. Further, unusual design techniques must often be applied to get around the limitations of some components.

## Sample and Hold Circuits

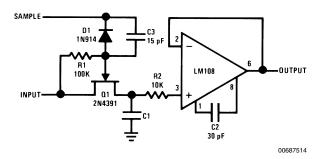

The holding accuracy of a sample and hold is directly related to the error currents in the components used. Therefore, it is a good circuit to start off with in explaining the problems involved. Figure 13 shows one configuration for a sample and hold. During the sample interval,  $Q_1$  is turned on, charging the hold capacitor,  $C_1$ , up to the value of the input signal.

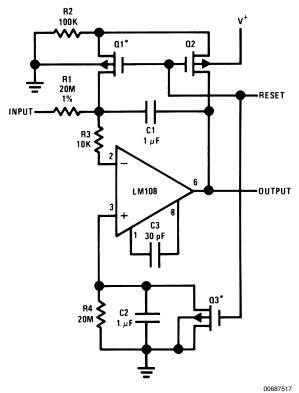

FIGURE 13. Sample and Hold Circuit

When  $Q_1$  is turned off,  $C_1$  retains this voltage. The output is obtained from an op amp that buffers the capacitor so that it is not discharged by any loading. In the holding mode, an error is generated as the capacitor looses charge to supply circuit leakages. The accumulation rate for error is given by

$$\frac{dV}{dt} = \frac{I_E}{C_1},$$

where dV/dt is the time rate of change in output voltage and  $I_{\rm E}$  is the sum of the input current to the op amp, the leakage current of the holding capacitor, board leakages and the "off" current of the FET switch.

When high-temperature operation is involved, the FET leakage can limit circuit performance. This can be minimized by using a junction FET, as indicated, because commercial junction FETs have lower leakage than their MOS counterparts. However, at 125°C even junction devices are a problem. Mechanical switches, such as read relays, are quite satisfactory from the standpoint of leakage. However, they are often undesirable because they are sensitive to vibration, they are too slow or they require excessive drive power. If this is the case, the circuit in *Figure 14* can be used to eliminate the FET leakage.

†Teflon, polyethylene or polycarbonate dielectric capacitor Worst case drift less than 3 mV/sec

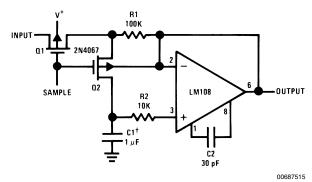

## FIGURE 14. Sample and Hold that Eliminates Leakage in FET Switches

When using P-channel MOS switches, the substrate must be connected to a voltage which is always more positive than the input signal. The source-to-substrate junction becomes forward biased if this is not done. The troublesome leakage current of a MOS device occurs across the substrate-to-drain junction. In *Figure 14*, this current is routed to the output of the buffer amplifier through  $R_1$  so that it does not contribute to the error current.

The main sample switch is  $Q_1$ , while  $Q_2$  isolates the hold capacitor from the leakage of  $Q_1$ . When the sample pulse is applied, both FETs turn on charging  $C_1$  to the input voltage. Removing the pulse shuts off both FETs, and the output leakage of  $Q_1$  goes through  $R_1$  to the output. The voltage drop across  $R_1$  is less than 10 mV, so the substrate of  $Q_2$  can be bootstrapped to the output of the LM108. Therefore, the voltage across the substrate-drain junction is equal to the offset voltage of the amplifier. At this low voltage, the leakage of the FET is reduced by about two orders of magnitude.

It is necessary to use MOS switches when bootstrapping the leakages in this fashion. The gate leakage of a MOS device is still negligible at high temperatures; this is not the case with junction FETs. If the MOS transistors have protective diodes on the gates, special arrangements must be made to drive  $\mathbf{Q}_2$  so the diode does not become forward biased.

In selecting the hold capacitor, low leakage is not the only requirement. The capacitor must also be free of dielectric

## Sample and Hold Circuits (Continued)

polarization phenomena.<sup>8</sup> This rules out such types as paper, mylar, electrolytic, tantalum or high-K ceramic. For small capacitor values, glass or silvered-mica capacitors are recommended. For the larger values, ones with teflon, polyethylene or polycarbonate dielectrics should be used.

The low input current of the LM108 gives a drift rate, in hold, of only 3 mV/sec when a 1  $\mu F$  hold capacitor is used. And this number is worst case over the military temperature range. Even if this kind of performance is not needed, it may still be beneficial to use the LM108 to reduce the size of the hold capacitor. High quality capacitors in the larger sizes are bulky and expensive. Further, the switches must have a low "on" resistance and be driven from a low impedance source to charge large capacitors in a short period of time.

If the sample interval is less than about 100  $\mu$ s, the LM108 may not be fast enough to work properly. If this is the case, it is advisable to substitute the LM102A, which is a voltage follower designed for both low input current and high speed. It has a 30 V/ $\mu$ s slew rate and will operate with sample intervals as short as 1  $\mu$ s.

When the hold capacitor is larger than 0.05  $\mu$ F, an isolation resistor should be included between the capacitor and the input of the amplifier (R<sub>2</sub> in *Figure 14*). This resistor insures that the IC will not be damaged by shorting the output or abruptly shutting down the supplies when the capacitor is charged. This precaution is not peculiar to the LM108 and should be observed on any IC op amp.

## Integrators

Integrators are a lot like sample-and-hold circuits and have essentially the same design problems. In an integrator, a capacitor is used as a storage element; and the error accumulation rate is again proportional to the input current of the op amp.

Figure 15 shows a circuit that can compensate for the bias current of the amplifier. A current is fed into the summing node through  $R_1$  to supply the bias current. The potentiometer,  $R_2$ , is adjusted so that this current exactly equals the bias current, reducing the drift rate to zero.

FIGURE 15. Integrator with Bias Current Compensation

The diode is used for two reasons. First, it acts as a regulator, making the compensation relatively insensitive to variations in supply voltage. Secondly, the temperature drift of diode voltage is approximately the same as the temperature drift of bias current. Therefore, the compensation is more effective if the temperature changes. Over a 0°C to 70°C temperature range, the compensation will give a factor of ten reduction in input current. Even better results are achieved if the temperature change is less.

Normally, it is necessary to reset an integrator to establish the initial conditions for integration. Resetting to zero is readily accomplished by shorting the integrating capacitor with a suitable switch. However, as with the sample and hold circuits, semiconductor switches can cause problems because of high-temperature leakage.

A connection that gets rid of switch leakages is shown in Figure 16. A negative-going reset pulse turns on  $Q_1$  and  $Q_2$ , shorting the integrating capacitor. When the switches turn off, the leakage current of  $Q_2$  is absorbed by  $R_2$  while  $Q_1$  isolates the output of  $Q_2$  from the summing node.  $Q_1$  has practically no voltage across its junctions because the substrate is grounded; hence, leakage currents are negligible.

\*Q1 and Q3 should not have internal gate-protection diodes.

### FIGURE 16. Low Drift Integrator with Reset

The additional circuitry shown in *Figure 16* makes the error accumulation rate proportional to the offset current, rather than the bias current. Hence, the drift is reduced by roughly a factor of 10. During the integration interval, the bias current of the non-inverting input accumulates an error across  $R_4$  and  $C_2$  just as the bias current on the inverting input does across  $R_1$  and  $C_1$ . Therefore, if  $R_4$  is matched with  $R_1$  and  $C_2$  is matched with  $C_1$  (within about 5 percent) the output will

#### Integrators (Continued)

drift at a rate proportional to the difference in these currents. At the end of the integration interval,  $Q_3$  removes the compensating error accumulated on  $C_2$  as the circuit is reset.

In applications involving large temperature changes, the circuit in  $\it Figure~16$  gives better results than the compensation scheme in  $\it Figure~15$ —especially under worst case conditions. Over a –55°C to 125°C temperature range, the worst case drift is reduced from 3 mV/sec to 0.5 mV/sec when a 1  $\mu F$  integrating capacitor is used. If this reduction in drift is not needed, the circuit can be simplified by eliminating  $R_4,~C_2$  and  $Q_3$  and returning the non-inverting input of the amplifier directly to ground.

In fabricating low drift integrators, it is again necessary to use high quality components and minimize leakage currents in the wiring. The comments made on capacitors in connection with the sample-and-hold circuits also apply here. As an additional precaution, a resistor should be used to isolate the inverting input from the integrating capacitor if it is larger than 0.05 µF. This resistor prevents damage that might occur when the supplies are abruptly shut down while the integrating capacitor is charged.

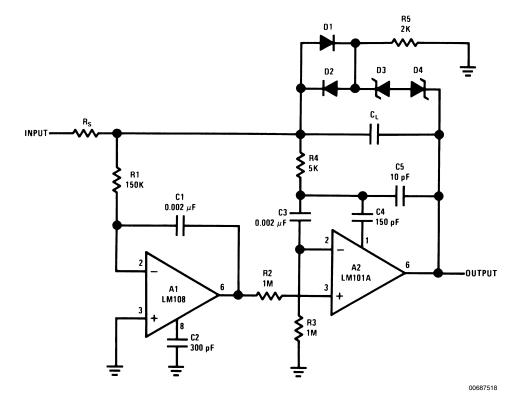

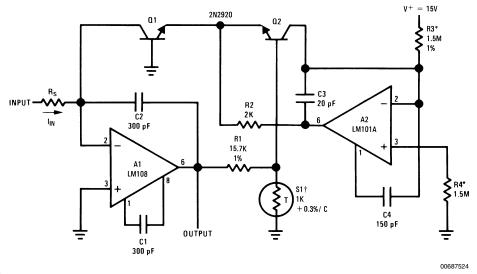

Some integrator applications require both speed and low error current. The output amplifiers for photomultiplier tubes or solid-state radiation dectectors are examples of this. Although the LM108 is relatively slow, there is a way to speed it up when it is used as an inverting amplifier. This is shown in *Figure 17*.

The circuit is arranged so that the high-frequency gain characteristics are determined by  $A_2$ , while  $A_1$  determines the dc and low-frequency characteristics. The non-inverting input of  $A_1$  is connected to the summing node through  $R_1$ .  $A_1$  is

operated as an integrator, going through unity gain at 500 Hz. Its output drives the non-inverting input of  $A_2$ . The inverting input of  $A_2$  is also connected to the summing node through  $C_3$ .  $C_3$  and  $R_3$  are chosen to roll off below 750 Hz. Hence, at frequencies above 750 Hz, the feedback path is directly around  $A_2$ , with  $A_1$  contributing little. Below 500 Hz, however, the direct feedback path to  $A_2$  rolls off; and the gain of  $A_1$  is added to that of  $A_2$ .

The high gain frequency amplifier,  $A_2$ , is an LM101A connected with feed-forward compensation. <sup>10</sup> It has a 10 MHz equivalent small-signal bandwidth, a 10V/µs slew rate and a 250 kHz large-signal bandwidth, so these are the high-frequency characteristics of the complete amplifier. The bias current of  $A_2$  is isolated from the summing node by  $C_3$ . Hence, it does not contribute to the dc drift of the integrator. The inverting input of  $A_1$  is the only dc connection to the summing junction. Therefore, the error current of the composite amplifier is equal to the bias current of  $A_1$ .

If  $A_2$  is allowed to saturate,  $A_1$  will then start towards saturation. If the output of  $A_1$  gets far off zero, recovery from saturation will be slowed drastically. This can be prevented by putting zener clamp diodes across the integrating capacitor. A suitable clamping arrangement is shown in *Figure 17*.  $D_1$  and  $D_2$  are included in the clamp circuit along with  $R_5$  to keep the leakage currents of the zeners from introducing errors.

In addition to increasing speed, this circuit has other advantages. For one, it has the increased output drive capability of the LM101A. Further, thermal feedback is virtually eliminated because the LM108 does not see load variations. Lastly, the open loop gain is nearly infinite at low frequencies as it is the product of the gains of the two amplifiers.

FIGURE 17. Fast Integrator

## Integrators (Continued)

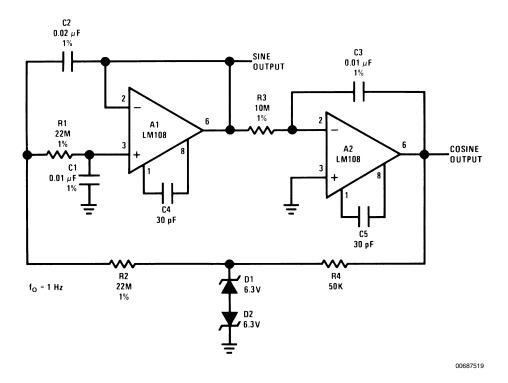

FIGURE 18. Sine Wave Oscillator

#### Sine Wave Oscillator

Although it is comparatively easy to build an oscillator that approximates a sine wave, making one that delivers a high-purity sinusoid with a stable frequency and amplitude is another story. Most satisfactory designs are relatively complicated and require individual trimming and temperature compensation to make them work. In addition, they generally take a long time to stabilize to the final output amplitude.

A unique solution to most of these problems is shown in Figure 18.  $A_1$  is connected as a two-pole low-pass active filter, and  $A_2$  is connected as an integrator. Since the ultimate phase lag introduced by the amplifiers is 270 degrees, the circuit can be made to oscillate if the loop gain is high enough at the frequency where the lag is 180 degrees. The gain is actually made somewhat higher than is required for oscillation to insure starting. Therefore, the amplitude builds up until it is limited by some nonlinearity in the system.

Amplitude stabilization is accomplished with zener clamp diodes,  $\mathsf{D}_1$  and  $\mathsf{D}_2.$  This does introduce distortion, but it is reduced by the subsequent low pass filters. If  $\mathsf{D}_1$  and  $\mathsf{D}_2$  have equal breakdown voltages, the resulting symmetrical clipping will virtually eliminate the even-order harmonics. The dominant harmonic is then the third, and this is about 40 dB down at the output of  $\mathsf{A}_1$  and about 50 dB down on the output of  $\mathsf{A}_2.$  This means that the total harmonic distortion on the two outputs is 1 percent and 0.3 percent, respectively.

The frequency of oscillation and the oscillation threshold are determined by  $R_1$ ,  $R_2$ ,  $R_3$ ,  $C_1$ ,  $C_2$  and  $C_3$ . Therefore precision components with low temperature coefficients should be used. If  $R_3$  is made lower than shown, the circuit will accept looser component tolerances before dropping out of oscillation. The start up will also be quicker. However, the price paid is that distortion is increased. The value of  $R_4$  is

not critical, but it should be made much smaller than  $\rm R_2$  so that the effective resistance at  $\rm R_2$  does not drop when the clamp diodes conduct.

The output amplitude is determined by the breakdown voltages of  $D_1$  and  $D_2$ . Therefore, the clamp level should be temperature compensated for stable operation. Diode-connected (collector shorted to base) NPN transistors with an emitter-base breakdown of about 6.3V work well, as the positive temperature coefficient of the diode in reverse breakdown nearly cancels the negative temperature coefficient of the forward-biased diode. Added advantages of using transistors are that they have less shunt capacitance and sharper breakdowns than conventional zeners.

The LM108 is particularly useful in this circuit at low frequencies, since it permits the use of small capacitors. The circuit shown oscillates at 1 Hz, but uses capacitors in the order of 0.01 µF. This makes it much easier to find temperature-stable precision capacitors. However, some judgment must be used as large value resistors with low temperature coefficients are not exactly easy to come by.\*

The LM108s are useful in this circuit for output frequencies up to 1 kHz. Beyond that, better performance can be realized by substituting and LM102A for  $A_1$  and an LM101A with feed-forward compensation for  $A_2$ . The improved high-frequency response of these devices extend the operating frequency out to 100 kHz.

Note: \*Large-value resistors are available from Victoreen Instrument, Cleveland, Ohio and Pyrofilm Resistor Co., Whippany, New Jersey.

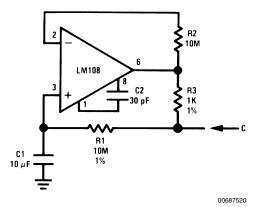

## **Capacitance Multiplier**

Large capacitor values can be eliminated from most systems just by raising the impedance levels, if suitable op amps are available. However, sometimes it is not possible because the

## Capacitance Multiplier (Continued)

impedance levels are already fixed by some element of the system like a low impedance transducer. If this is the case, a capacitance multiplier can be used to increase the effective capacitance of a small capacitor and couple it into a low impedance system.

Previously, IC op amps could not be used effectively as capacitance multipliers because the equivalent leakages generated due to offset current were significantly greater than the leakages of large tantalum capacitors. With the LM108, this has changed. The circuit shown in *Figure 19* generates an equivalent capacitance of 100,000  $\mu F$  with a worst case leakage of 8  $\mu A$ —over a –55°C to 125°C temperature range.

$$C = \frac{R1}{R3}C1$$

$$I_L = \frac{V_{OS} + I_{OS}R1}{R3}$$

$$R_s = R3$$

FIGURE 19. Capacitance Multiplier

The performance of the circuit is described by the equations given in Figure 19, where C is the effective output capacitance,  $\rm I_L$  is the leakage current of this capacitance and  $\rm R_s$  is the series resistance of the multiplied capacitance. The series resistance is relatively high, so high-Q capacitors cannot be realized. Hence, such applications as tuned circuits and filters are ruled out. However, the multiplier can still be used in timing circuits or servo compensation networks where some resistance is usually connected in series with the capacitor or the effect of the resistance can be compensated for.

One final point is that the leakage current of the multiplied capacitance is not a function of the applied voltage. It persists even with no voltage on the output. Therefore, it can generate offset errors in a circuit, rather than the scaling errors caused by conventional capacitors.

## Instrumentation Amplifier

In many instrumentation applications there is frequently a need for an amplifier with a high-impedance differential input and a single ended output. Obvious uses for this are amplifiers for bridge-type signal sources such as strain gages, temperature sensors or pressure transducers. General pur-

pose op amps have satisfactory input characteristics, but feedback must be added to determine the effective gain. And the addition of feedback can drastically reduce the input resistance and degrade common mode rejection.

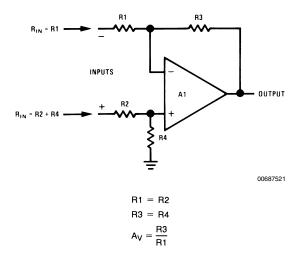

Figure 20 shows the classical op amp circuit for a differential amplifier. This circuit has three main disadvantages. First, the input resistance on the inverting input is relatively low, being equal to R<sub>1</sub>. Second, there usually is a large difference in the input resistance of the two inputs, as is indicated by the equations on the schematic. Third, the common mode rejection is greatly affected by resistor matching and by balancing of the source resistances. A 1-percent deviation in any one of the resistor values reduces the common mode rejection to 46 dB for a closed loop gain of 1, to 60 dB for a gain of 10 and to 80 dB for a gain of 100.

Clearly, the only way to get high input impedance is to use very large resistors in the feedback network. The op amp must operate from a source resistance which is orders of magnitude larger than the resistance of the signal source. Older IC op amps introduced excessive offset and drift when operating from higher resistances and could not be used successfully. The LM108, however, is relatively unaffected by the large resistors, so this approach can sometimes be employed.

With large input resistors, the feedback resistors,  $R_3$  and  $R_4$ , can get quite large for higher closed loop gains. For example, if  $R_1$  and  $R_2$  are 1  $M\Omega,\,R_3$  and  $R_4$  must be 100  $M\Omega$  for a gain of 100. It is difficult to accurately match resistors that are this high in value, so common mode rejection may suffer. Nonetheless, any one of the resistors can be trimmed to take out common mode feedthrough caused either by resistors mismatches or the amplifier itself.

FIGURE 20. Feedback Connection for a Differential Amplifier

Another problem caused by large feedback resistors is that stray capacitance can seriously affect the high frequency common mode rejection. With 1  $\mathrm{M}\Omega$  input resistors, a 1 pF mismatch in stray capacitance from either input to ground can drop the common mode rejection to 40 dB at 1500 Hz. The high frequency rejection can be improved at the expense of frequency response by shunting  $\mathrm{R}_3$  and  $\mathrm{R}_4$  with matched capacitors.

## **Instrumentation Amplifier** (Continued)

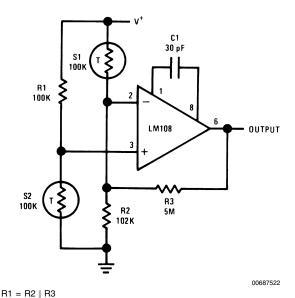

With high impedance bridges, the feedback resistances become prohibitively large even for the LM108, so the circuit in Figure 20 cannot be used. One possible alternative is shown in Figure 21.  $\rm R_2$  and  $\rm R_3$  are chosen so that their equivalent parallel resistance is equal to  $\rm R_1$ . Hence, the output of the amplifier will be zero when the bridge is balanced.

FIGURE 21. Amplifier for Bridge Transducers

When the bridge goes off balance, the op amp maintains the voltage between its input terminals at zero with current fed back from the output through  $\rm R_3$ . This circuit does not act like a true differential amplifier for large imbalances in the bridge. The voltage drops across the two sensor resistors,  $\rm S_1$  and  $\rm S_2$ , become unequal as the bridge goes off balance, causing some non-linearity in the transfer function. However, this is not usually objectionable for small signal swings.

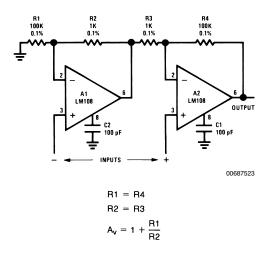

FIGURE 22. Differential Input Instrumentation Amplifier

Figure 22 shows a true differential connection that has few of the problems mentioned previously. It has an input resistance greater than  $10^{10}\Omega$ , yet it does not need large resistors in the feedback circuitry. With the component values shown,  $A_1$  is connected as a non-inverting amplifier with a gain of 1.01; and it feeds into  $A_2$  which has an inverting gain of 100. Hence, the total gain from the input of  $A_1$  to the output of  $A_2$  is 101, which is equal to the non-inverting gain of  $A_2$ . If all the resistors are matched, the circuit responds only to the differential input signal — not the common mode voltage.

This circuit has the same sensitivity to resistor matching as the previous circuits, with a 1 percent mismatch between two resistors lowering the common mode rejection to 80 dB. However, matching is more easily accomplished because of the lower resistor values. Further, the high frequency common mode rejection is less affected by stray capacitances. The high frequency rejection is limited, though, by the response of  $A_1$

## **Logarithmic Converter**

A logarithmic amplifier is another circuit that can take advantage of the low input current of an op amp to increase dynamic range. Most practical log converters make use of the logarithmic relationship between the emitter-base voltage of standard double-diffused transistors and their collector current. This logarithmic characteristic has been proven true for over 9 decades of collector current. The only problem involved in using transistors as logging elements is that the scale factor has a temperature sensitivity of 0.3 percent/°C. However, temperature compensating resistors have been developed to compensate for this characteristic, making possible log converters that are accurate over a wide temperature range.

## Logarithmic Converter (Continued)

$10 \text{ nA} < I_{\text{IN}} < 1 \text{ mA}$

Sensitivity is 1V per decade.

†1 k $\Omega$  (±1%) at 25°C, +3500 ppm/°C.

Available from Vishay Ultronix, Grand Junction, CO, Q81 Series.

\*Determines current for zero crossing on output: 10 µA as shown.

FIGURE 23. Temperature Compensated One-Quadrant Logarithmic Converter

Figure 23 gives a circuit that uses these techniques.  $Q_1$  is the logging transistor, while  $Q_2$  provides a fixed offset to temperature compensate the emitter-base turn on voltage of  $Q_1$ .  $Q_2$  is operated at a fixed collector current of 10  $\mu$ A by  $A_2$ , and its emitter-base voltage is subtracted from that of  $Q_1$  in determining the output voltage of the circuit. The collector current of  $Q_2$  is established by  $P_3$  and  $V^+$  through  $P_3$ .

The collector current of  $Q_1$  is proportional to the input current through  $R_s$  and, therefore, proportional to the input voltage. The emitter-base voltage of  $Q_1$  varies as the log of the input voltage. The fixed emitter-base voltage of  $Q_2$  subtracts from the voltage on the emitter of  $Q_1$  in determining the voltage on the top end of the temperature-compensating resistor,  $S_1$ .

The signal on the top of  $S_1$  will be zero when the input current is equal to the current through  $R_3$  at any temperature. Further, this voltage will vary logarithmically for changes in input current, although the scale factor will have a temperature coefficient of -0.3%°C. The output of the converter is essentially multiplied by the ratio of  $R_1$  to  $S_1$ . Since  $S_1$  has a positive temperature coefficient of 0.3%°C, it compensates for the change in scale factor with temperature.

In this circuit, an LM101A with feedforward compensation is used for  $A_2$  since it is much faster than the LM108 used for  $A_1$ . Since both amplifiers are cascaded in the overall feedback loop, the reduced phase shift through  $A_2$  insures stability.

Certain things must be considered in designing this circuit. For one, the sensitivity can be changed by varying  $\mathsf{R}_1.$  But  $\mathsf{R}_1$  must be made considerably larger than the resistance of  $\mathsf{S}_1$  for effective temperature compensation of the scale factor.  $\mathsf{Q}_1$  and  $\mathsf{Q}_2$  should also be matched devices in the same package, and  $\mathsf{S}_1$  should be at the same temperature as these transistors. Accuracy for low input currents is determined by the error caused by the bias current of  $\mathsf{A}_1.$  At high currents, the behavior of  $\mathsf{Q}_1$  and  $\mathsf{Q}_2$  limits accuracy. For input currents approaching 1 mA, the 2N2920 develops logging errors in excess of 1 percent. If larger input currents are anticipated, bigger transistors must be used; and  $\mathsf{R}_2$  should be reduced to insure that  $\mathsf{A}_2$  does not saturate.

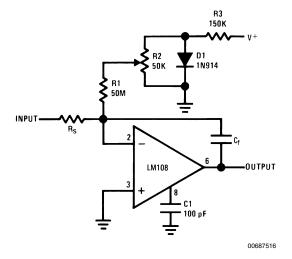

## Transducer Amplifiers

With certain transducers, accuracy depends on the choice of the circuit configuration as much as it does on the quality of the components. The amplifier for photodiode sensors, shown in *Figure 24*, illustrates this point. Normally, photodiodes are operated with reverse voltage across the junction. At high temperatures, the leakage currents can approach the signal current. However, photodiodes deliver a short-circuit output current, unaffected by leakage currents, which is not significantly lower than the output current with reverse bias.

## Transducer Amplifiers (Continued)

FIGURE 24. Amplifier for Photodiode Sensor

FIGURE 25. Amplifier for Piezoelectric Transducers

The circuit shown in *Figure 24* responds to the short-circuit output current of the photodiode. Since the voltage across the diode is only the offset voltage of the amplifier, inherent leakage is reduced by at least two orders of magnitude. Neglecting the offset current of the amplifier, the output current of the sensor is multiplied by  $R_1$  plus  $R_2$  in determining the output voltage.

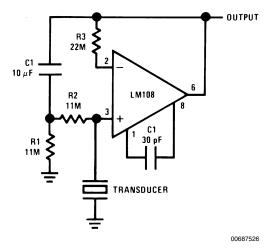

Figure 25 shows an amplifier for high-impedance ac transducers like a piezoelectric accelerometer. These sensors normally require a high-input-resistance amplifier. The LM108 can provide input resistances in the range of 10 to 100  $M\Omega,$  using conventional circuitry. However, conventional designs are sometimes ruled out either because large resistors cannot be used or because prohibitively large input resistances are needed.

Using the circuit in *Figure 25*, input resistances that are orders of magnitude greater than the values of the dc return resistors can be obtained. This is accomplished by bootstrapping the resistors to the output. With this arrangement, the lower cutoff frequency of a capacitive transducer is de-

termined more by the RC product of  $R_1$  and  $C_1$  than it is by resistor values and the equivalent capacitance of the transducer.

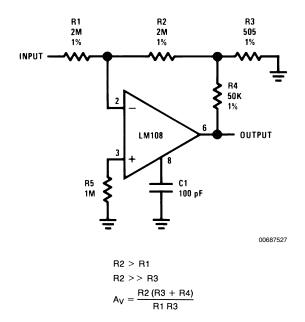

## **Resistance Multiplication**

When an inverting operational amplifier must have high input resistance, the resistor values required can get out of hand. For example, if a 2 M $\Omega$  input resistance is needed for an amplifier with a gain of 100, a 200 M $\Omega$  feedback resistor is called for. This resistance can, however, be reduced using the circuit in *Figure 26*. A divider with a ratio of 100 to 1 (R $_3$  and R $_4$ ) is added to the output of the amplifier: Unity-gain feedback is applied from the output of the divider, giving an overall gain of 100 using only 2 M $\Omega$  resistors.

This circuit does increase the offset voltage somewhat. The output offset voltage is given by

$$V_{OUT} = \left(\frac{R_1 + R_2}{R_2}\right) A_V V_{os}.$$

The offset voltage is only multiplied by A<sub>V</sub> +1 in a conventional inverter. Therefore, the circuit in *Figure 26* multiplies the offset by 200, instead of 101. This multiplication factor can be reduced to 110 by increasing R<sub>2</sub> to 20  $\mathrm{M}\Omega$  and R<sub>3</sub> to 5.55k.

FIGURE 26. Inverting Amplifier with High Input Resistance

Another disadvantage of the circuit is that four resistors determine the gain, instead of two. Hence, for a given resistor tolerance, the worst-case gain deviation is greater, although this is probably more than offset by the ease of getting better tolerances in the low resistor values.

#### **Current Sources**

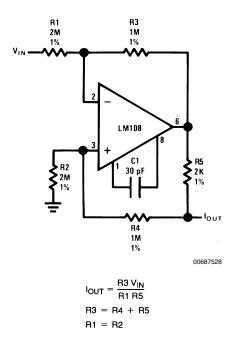

Although there are numerous ways to make current sources with op amps, most have limitations as far as their application is concerned. *Figure 27*, however, shows a current source which is fairly flexible and has few restrictions as far as its use is concerned. It supplies a current that is proportional to the input voltage and drives a load referred to ground or any voltage within the output-swing capability of the amplifier.

FIGURE 27. Bilateral Current Source

With the output grounded, it is relatively obvious that the output current will be determined by  $R_5$  and the gain setting of the op amp, yielding

$$I_{OUT} = -\frac{R_3 V_{IN}}{R_1 R_5}.$$

When the output is not at zero, it would seem that the current through  $R_2$  and  $R_4$  would reduce accuracy. Nonetheless, if  $R_1=R_2$  and  $R_3=R_4+R_5$ , the output current will be independent of the output voltage. For  $R_1+R_3 \geqslant R_5$ , the output resistance of the circuit is given by

$$R_{OUT} \cong R_5 \left(\frac{R}{\Delta R}\right)$$

where R is any one of the feedback resistors (R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> or R<sub>4</sub>) and  $\Delta$ R is the incremental change in the resistor value from design center. Hence, for the circuit in *Figure 27*, a 1 percent deviation in one of the resistor values will drop the output resistance to 200 k $\Omega$ . Such errors can be trimmed out by adjusting one of the feedback resistors. In design, it is

advisable to make the feedback resistors as large as possible. Otherwise, resistor tolerances become even more critical.

The circuit must be driven from a source resistance which is low by comparison to  $R_1$ , since this resistance will imbalance the circuit and affect both gain and output resistance. As shown, the circuit gives a negative output current for a positive input voltage. This can be reversed by grounding the input and driving the ground end of  $R_2$ . The magnitude of the scale factor will be unchanged as long as  $R_4 \gg R_5$ .

## **Voltage Comparators**

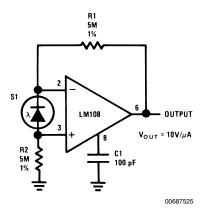

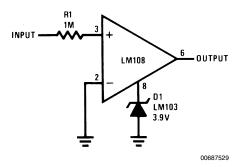

Like most op amps, it is possible to use the LM108 as a voltage comparator. Figure 28 shows the device used as a simple zero-crossing detector. The inputs of the IC are protected internally by back-to-back diodes connected between them, therefore, voltages in excess of 1V cannot be impressed directly across the inputs. This problem is taken care of by  $\rm R_1$  which limits the current so that input voltages in excess of 1 kV can be tolerated. If absolute accuracy is required or if  $\rm R_1$  is made much larger than 1  $\rm M\Omega$ , a compensating resistor of equal value should be inserted in series with the other input.

FIGURE 28. Zero Crossing Detector

In Figure 28, the output of the op amp is clamped so that it can drive DTL or TTL directly. This is accomplished with a clamp diode on pin 8. When the output swings positive, it is clamped at the breakdown voltage of the zener. When it swings negative, it is clamped at a diode drop below ground. If the 5V logic supply is used as a positive supply for the amplifier, the zener can be replaced with an ordinary silicon diode. The maximum fan out that can be handled by the device is one for standard DTL or TTL under worst case conditions.

As might be expected, the LM108 is not very fast when used as a comparator. The response time is up in the tens of microseconds. An LM103 $^{11}$  is recommended for D $_{1}$ , rather than a conventional alloy zener, because it has lower capacitance and will not slow the circuit further. The sharp breakdown of the LM103 at low currents is also an advantage as the current through the diode in clamp is only 10  $\mu\text{A}$ .

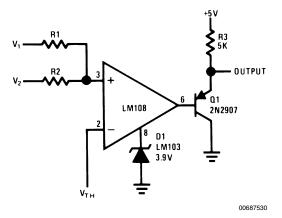

Figure 29 shows a comparator for voltages of opposite polarity. The output changes state when the voltage on the junction of  $\rm R_1$  and  $\rm R_2$  is equal to  $\rm V_{TH}$ . Mathematically, this is expressed by

$$V_{TH} = V_2 + \frac{R_2 (V_1 - V_2)}{R_1 + R_2}$$

## **Voltage Comparators** (Continued)

FIGURE 29. Voltage Comparator with Output Buffer

The LM108 can also be used as a differential comparator, going through a transition when two input voltages are equal. However, resistors must be inserted in series with the inputs to limit current and minimize loading on the signal sources when the input-protection diodes conduct. *Figure 29* also shows how a PNP transistor can be added on the output to increase the fan out to about 20 with standard DTL or TTL.

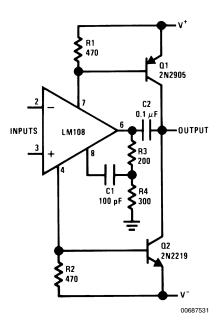

simple booster can be added to the output to increase the output current to ±50 mA. This circuit, shown in *Figure 30*, has the added advantage that it swings the output up to the supplies, within a fraction of a volt. The increased voltage swing is particularly helpful in low voltage circuits.

#### **Power Booster**

The LM108, which was designed for low power consumption, is not able to drive heavy loads. However, a relatively

FIGURE 30. Power Booster

In *Figure 30*, the output transistors are driven from the supply leads of the op amp. It is important that  $R_1$  and  $R_2$  be made low enough so  $Q_1$  and  $Q_2$  are not turned on by the *worst case* quiescent current of the amplifier. The output of the op amp is loaded heavily to ground with  $R_3$  and  $R_4$ .

When the output swings about 0.5V positive, the increasing positive supply current will turn on  $Q_1$  which pulls up the load. A similar situation occurs with  $Q_2$  for negative output swings.

## Power Booster (Continued)

The bootstrapped shunt compensation shown in the figure is the only one that seems to work for all loading conditions. This capacitor,  $C_1$ , can be made inversely proportional to the closed loop gain to optimize frequency response. The value given is for a unity-gain follower connection.  $C_2$  is also required for loop stability.

The circuit does have a dead zone in the open loop transfer characteristic. However, the low frequency gain is high enough so that it can be neglected. Around 1 kHz, though, the dead zone becomes quite noticeable.

Current limiting can be incorporated into the circuit by adding resistors in series with the emitters of  $Q_1$  and  $Q_2$  because the short circuit protection of the LM108 limits the maximum voltage drop across  $R_1$  and  $R_2$ .

#### **Board Construction**

As indicated previously, certain precautions must be observed when building circuits that are sensitive to very low currents. If proper care is not taken, board leakage currents can easily become much larger than the error currents of the op amp. To prevent this, it is necessary to thoroughly clean printed circuit boards. Even experimental breadboards must be cleaned with trichloroethlene or alcohol to remove solder fluxes, and blown dry with compressed air. These fluxes may be insulators at low impedance levels—like in electric motors—but they certainly are not in high impedance circuits. In addition to causing gross errors, their presence can make the circuit behave erratically, especially as the temperature is changed.

FIGURE 31. Printed Circuit Layout for Input Guarding with TO-5 Package

At elevated temperatures, even the leakage of clean boards can be a headache. At  $125^{\circ}\text{C}$  the leakage resistance between adjacent runs on a printed circuit board is about  $10^{11}\Omega$  (0.05-inch separation parallel for 1 inch) for high quality epoxy-glass boards that have been properly cleaned. Therefore, the boards can easily produce error currents in the order of 200 pA and much more if they become contaminated. Conservative practice dictates that the boards be coated with epoxy or silicone rubber after cleaning to prevent contamination. Silicone rubber is the easiest to use. How-

ever, if the better durability of epoxy is needed, care must be taken to make sure that it gets thoroughly cured. Otherwise, the epoxy will make high temperature leakage much worse. Care must also be exercised to insure that the circuit board is protected from condensed water vapor when operating in the vicinity of 0°C. This can usually be accomplished by coating the board as mentioned above.

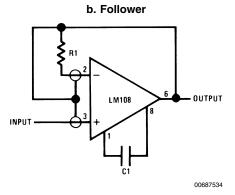

#### c. Non-Inverting Amplifier

FIGURE 32. Connection of Input Guards

## Guarding

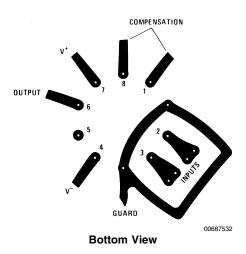

Even with properly cleaned and coated boards, leakage currents are on the verge of causing trouble at 125°C. The standard pin configuration of most IC op amps has the input pins adjacent to pins which are at the supply potentials.

## Guarding (Continued)

Therefore, it is advisable to employ guarding to reduce the voltage difference between the inputs and adjacent metal runs.

A board layout that includes input guarding is shown in *Figure 31* for the eight lead TO-5 package. A ten-lead pin circle is used, and the leads of the IC are formed so that the holes adjacent to the inputs are vacant when it is inserted in the board. The guard, which is a conductive ring surrounding the inputs, is then connected to a low impedance point that is at the same potential as the inputs. The leakage currents from the pins at the supply potentials are absorbed by the guard. The voltage difference between the guard and the inputs can be made approximately equal to the offset voltage, reducing the effective leakage by more than three orders of magnitude. If the leads of the integrated circuit, or other components connected to the input, go through the board, it may be necessary to guard both sides.

Figure 32 shows how the guard is committed on the more-common op amp circuits. With an integrator or inverting amplifier, where the inputs are close to ground potential, the guard is simply grounded. With the voltage follower, the guard is bootstrapped to the output. If it is desirable to put a resistor in the inverting input to compensate for the source resistance, it is connected as shown in Figure 32b.

Guarding a non-inverting amplifier is a little more complicated. A low impedance point must be created by using relatively low value feedback resistors to determine the gain

$(R_1$  and  $R_2$  in *Figure 32c*). The guard is then connected to the junction of the feedback resistors. A resistor,  $R_3$ , can be connected as shown in the figure to compensate for large source resistances.

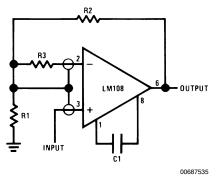

With the dual-in-line and flat packages, it is far more difficult to guard the inputs, if the standard pin configuration of the LM709 or LM101A is used, because the pin spacings on these packages are fixed. Therefore, the pin configuration of the LM108 was changed, as shown in *Figure 33*.

## **Conclusions**

IC op amps are now available that equal the input current specifications of FET amplifiers in all but the most restricted temperature range applications. At operating temperatures above 85°C, the IC is clearly superior as it uses bipolar transistors that make it possible to eliminate the leakage currents that plague FETs. Additionally, bipolar transistors match better than FETs, so low offset voltage and drifts can be obtained without expensive adjustments or selection. Further, the bipolar devices lend themselves more readily to low-cost monolithic construction.

These amplifiers open up new application areas and vastly improve performance in others. For example, in analog memories, holding intervals can be extended to minutes, even where -55°C to 125°C operation is involved. Instrumentation amplifiers and low frequency waveform generators also benefit from the low error currents.

FIGURE 33. Comparing Connection Diagrams of the LM101A and LM108, Showing Addition of Guarding

When operating above 85°C, overall performance is frequently limited by components other than the op amp, unless certain precautions are observed. It is generally necessary to redesign circuits using semiconductor switches to reduce the effect of their leakage currents. Further, high quality capacitors must be used, and care must be exercised in selecting large value resistors. Printed circuit board leakages can also be troublesome unless the boards are properly treated. And above 100°C, it is almost mandatory to employ guarding on the boards to protect the inputs, if the full potential of the amplifier is to be realized.

## **Appendix**

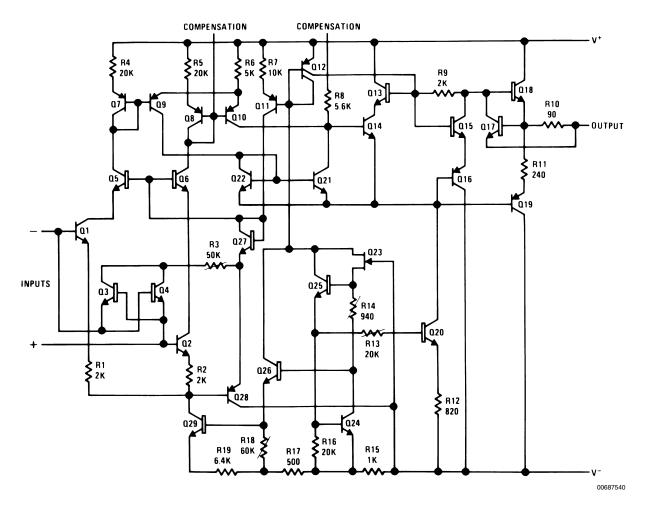

A complete schematic of the LM108 is given in Figure 34. A description of the basic circuit is presented along with a

simplified schematic earlier in the text. The purpose of this Appendix is to explain some of the more subtle features of the design.

The current source supplying the input transistors is  $Q_{29}$ . It is designed to supply a total input stage current of 6  $\mu$ A at 25°C. This current drops to 3  $\mu$ A at -55°C but increases to only 7.5  $\mu$ A at 125°C. This temperature characteristic tends to compensate for the current gain falloff of the input transistors at low temperatures without creating stability problems at high temperatures.

The biasing circuitry for the input current source is nearly identical to that in the LM101A, and a complete description is given in Reference 4. However, a brief explanation follows.

## Appendix (Continued)

A collector FET,  $^6$   $Q_{23}$ , which has a saturation current of about 30  $\mu$ A, establishes the collector current of  $Q_{24}$ . This FET provides the initial turn-on current for the circuit and insures starting under all conditions. The purpose of  $R_{14}$  is to compensate for production and temperature variations in the FET current. It is a collector resistor (indicated by the T through it) made of the same semiconductor material as the FET channel. As the FET current varies, the drop across  $R_{14}$  tends to compensate for changes in the emitter base voltage of  $Q_{24}$ .

The collector-emitter voltage of  $Q_{24}$  is equal to the emitter base voltage of  $Q_{24}$  plus that of  $Q_{25}$ . This voltage is delivered to  $Q_{26}$  and  $Q_{29}$ .  $Q_{25}$  and  $Q_{24}$  are operated at substantially higher currents than  $Q_{26}$  and  $Q_{29}$ . Hence, there is a differential in their emitter base voltages that is dropped across  $R_{19}$  to determine the input stage current.  $R_{18}$  is a pinched base resistor, as is indicated by the slash bar through it. This resistor, which has a large positive temperature coefficient, operates in conjunction with  $R_{17}$  to help shape the temperature characteristics of the input stage current source.

FIGURE 34. Complete Schematic of the LM108

The output currents of  $Q_{26}$ ,  $Q_{25}$ , and  $Q_{23}$  are fed to  $Q_{12}$ , which is a controlled-gain lateral PNP.<sup>6</sup> It delivers one-half of the combined currents to the output stage.  $Q_{11}$  is also connected to  $Q_{12}$ , with its output current set at approximately 15  $\mu$ A by  $R_7$ . Since this type of current source makes use of the emitter-base voltage differential between similar transistors operating at different collector currents, the output of  $Q_{11}$  is relatively independent of the current delivered to  $Q_{12}$ . <sup>12</sup> This current is used for the input stage bootstrapping circuitry.

$\rm Q_{20}$  also supplies current to the class-B output stage. Its output current is determined by the ratio of  $\rm R_{15}$  to  $\rm R_{12}$  and the current through  $\rm R_{12}$ .  $\rm R_{13}$  is included so that the biasing circuit is not upset when  $\rm Q_{20}$  saturates.

One major departure from the simplified schematic is the bootstrapping of the second stage active loads,  $Q_{21}$  and  $Q_{22}$ , to the output. This makes the second stage gain dependent only on how well  $Q_9$  and  $Q_{10}$  match with variations in output voltage. Hence, the second stage gain is quite high. In fact, the overall gain of the amplifier is typically in excess of  $10^6$  at dc.

The second stage active loads drive  $Q_{14}$ . A high-gain primary transistor is used to prevent loading of the second stage. Its collector is bootstrapped by  $Q_{13}$  to operate it at zero collector-base voltage. The class-B output stage is actually driven by the emitter of  $Q_{14}$ .

## Appendix (Continued)

A dead zone in the output stage is prevented by biasing Q<sub>18</sub> and Q<sub>19</sub> on the verge of conduction with Q<sub>15</sub> and Q<sub>16</sub>. R<sub>9</sub> is used to compensate for the transconductance of Q15 and Q<sub>16</sub>, making the output stage quiescent current relatively independent of the output current of Q<sub>12</sub>. The drop across this resistor also reduces quiescent current.

For positive-going outputs, short circuit protection is provided by  $R_{10}$  and  $Q_{17}$ . When the voltage drop across  $R_{10}$ turns on Q<sub>17</sub>, it removes base drive from Q<sub>18</sub>. For negative-going outputs, current limiting is initiated when the voltage drop across R<sub>11</sub> becomes large enough for the collector base junction of Q<sub>17</sub> to become forward biased. When this happens, the base of Q<sub>19</sub> is clamped so the output current cannot increase further.

Input protection is provided by Q<sub>3</sub> and Q<sub>4</sub> which act as clamp diodes between the inputs. The collectors of these transistors are bootstrapped to the emitter of Q28 through R3. This keeps the collector-isolation leakage of the transistors from showing up on the inputs. R<sub>3</sub> is included so that the bootstrapping is not disrupted when Q3 or Q4 saturate with an input overload. Current-limiting resistors were not connected in series with the inputs, since diffused resistors cannot be employed such that they work effectively, without causing high temperature leakages.

TABLE 1. Typical Performance of the LM108 Operational Amplifier ( $T_A = 25^{\circ}C$  and  $V_S = \pm 15V$ )

|                         | ,         |

|-------------------------|-----------|

| Input Offset Voltage    | 0.7 mV    |

| Input Offset Current    | 50 pA     |

| Input Bias Current      | 0.8 nA    |

| Input Resistance        | 70 MΩ     |

| Input Common Mode Range | ±14V      |

| Common Mode Rejection   | 100 dB    |

| Offset Voltage Drift    | 3 μV/°C   |

| Offset Current Drift    | 0.5 pA/°C |

| Voltage Gain            | 300V/mW   |

| Small Signal Bandwidth  | 1.0 MHz   |

| Slew Rate               | 0.3V/µs   |

| Output Swing            | ±14V      |

|                         |           |

Supply Current 300 μΑ 100 dB Power Supply Rejection Operating Voltage Range ±2V to ±20V

#### References

- 1. R. J. Widlar, "Future Trends in Intregrated Operational Amplifiers," EDN, Vol. 13, No 6, pp 24-29, June 1968.

- 2. R. J. Widlar, "Super Gain Transistors for IC," IEEE Journal of Solid-State Circuits, Vol. SC-4, No. 4, August, 1969.

- 3. R. J. Widlar, "A Unique Circuit Design for a High Performance Operational Amplifier Especially Suited to Monolithic Construction," Proc. of NEC, Vol.XXI, pp. 85-89, October, 1965.

- R. J. Widlar, "I.C. Op Amp with Improved Input-Current Characteristics," EEE, pp. 38-41, December, 1968.

- R. J. Widlar, "Linear IC's: part 6; Compensating for Drift," Electronics, Vol. 41, No. 3, pp. 90-93, February, 1968.

- 6. R. J. Widlar, "Design Techniques for Monolithic Operational Amplifiers," IEEE Journal of Solid-State Circuits, Fol. SC-4, No. 4, August 1969.

- 7. D. R. Sulllivan and M. A. Maidique, "Characterization and Application of a New High Input Impedance Monolithic Amplifier," Transitron Electronic Corporation Appli-

- 8. Paul C. Dow, Jr., "An Analysis of Certain Errors in Electronic Differential Analyzers, II-Capacitor Dielectric Absorption," IRE Trans. on Electronic Computers, pp. 17-22, March, 1958.

- 9. R. J. Widlar, "A Fast Integrated Voltage Follower with Low Input Current," Microelectrics, Vol. 1, No. 7, June, 1968.

- 10. R. C. Dobkin, "Feedforward Compensation Speeds Op Amp," National Semiconductor LB-2, March, 1969.

- 11. R. J. Wildlar, "A New Low Voltage Breakdown Diode," National Semiconductor TP-5, April, 1968.

- 12. R. J. Widlar, "Some Circuit Design Techniques for Linear Integrated Circuits," IEEE Transactions on Circuit Theory, Vol. CT-12, No. 4, pp. 586-590, December,

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation

Email: support@nsc.com

www.national.com

**National Semiconductor**

Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor**

Tel: 81-3-5639-7560 Fax: 81-3-5639-7507