# Professional Radio Applications

## Professional Radio Applications

This application note describes the use of integrated circuits manufactured by Plessey Semiconductors in Professional Radio applications.

Development of new circuits for this field of application continues. The Customer Services Manager, Plessey Semiconductors Ltd. should be contacted to obtain details of new products.

## Contents

| Radio Linear Circuits                | 5  |

|--------------------------------------|----|

| Product Range — SL600, 1600 Series   | 6  |

| SL610/11/12                          | 7  |

| SL640/41                             | 12 |

| SL621                                | 16 |

| SL623                                | 20 |

| SL630                                | 23 |

| Applications — SL600, 1600 Series    | 25 |

| Product Range SL6000 Series          | 33 |

| SL6600                               | 33 |

| SL6640/50                            | 38 |

| SL6690                               | 43 |

| Applications — SL6000 Series         | 44 |

| High Speed Dividers                  | 49 |

| Product Range — SP8000 Series        | 50 |

| Input Characterisation               | 55 |

| Preamplifiers                        | 61 |

| Synthesiser Circuits                 | 65 |

| Product Range — Synthesiser Circuits | 71 |

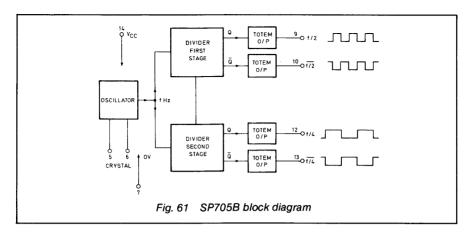

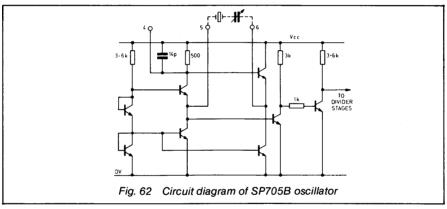

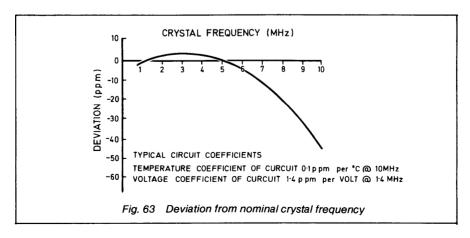

| SP705B                               | 71 |

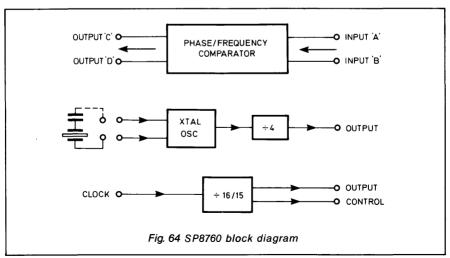

| SP8760                               | 73 |

| SP8921/2                             | 76 |

© The Plessey Company Limited August 1979 Publication No P.S.1701

This publication is issued to provide outline information only and (unless specifically agreed to the contrary by the Company in writing) is not to form part of any order or contract or be regarded as a representation relating to the products or services concerned. We reserve the right to alter without notice the specification, design, price or conditions of supply of any product or service.

# Section 1 Radio Linear Circuits

## Radio Linear Circuits

#### INTRODUCTION TO SL600 AND SL1600 SERIES

Plessey Semiconductors originally developed the SL600 series for use in military SSB systems. For such applications, hermetic packages and full-temperature operation are necessary: the SL600 series devices meet such specifications. As the range expanded, requirements arose for less expensive versions of SL600 devices and the SL1600 series was introduced. The SL1600 series consists of the same chips as are used in the SL600 series but packaged in plastic DIL packages (mostly 8-lead minidips) tested to less stringent specifications, and supplied with a  $-30^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$  temperature specification. In a few cases some of the pins present in the SL600 devices are omitted in the SL1600 devices in order to allow a chip previously supplied in a 10-lead TO-5 to be encapsulated in an 8-lead minidip.

SL600 and SL1600 type numbers are used in section headings but to avoid tedious repetition, only the SL600 type numbers will be used in the text unless there are significant differences between the SL600 and SL1600 devices. Pin numbers generally refer to both types; in cases where pin numbers differ, the pin numbers for the SL1600 device is given in brackets, e.g. Pin 6(7).

| SL600/1600 PRODUCT RANGE              |                         |                            |                                     |

|---------------------------------------|-------------------------|----------------------------|-------------------------------------|

| AMPLIFIERS                            | SL610<br>SL611<br>SL612 | SL1610<br>SL1611<br>SL1612 | ·                                   |

| MIXERS                                | SL640<br>SL 641         | SL1640<br>SL1641           |                                     |

| DETECTORS<br>AND<br>AGC<br>GENERATORS | SL621<br>SL623          | SL1621<br>SL1623<br>SL1625 | AMSSB detector and AGC from carrier |

| AUDIO                                 | SL630                   |                            | 200mW headphone amplifier           |

## SL610C, SL611C, SL612C, SL1610C, SL1611C & SL1612C

#### RF/IF amplifiers

The SL610C, SL611C and SL612C integrated RF amplifiers are similar circuits, having typical voltage gains of 10, 20 and 50 and upper 3dB gain points at 140MHz, 100MHz and 15MHz respectively. The first two draw a supply current of about 15mA at 6V and have some 50dB AGC range while the SL612C draws 3.5mA and has 70dB of AGC. All three are intended to use with  $+6\mathrm{V}$  supplies and have internal decoupling. They will drive an output signal of about 1V rms.

The cross-modulation of the circuits is 40dB down on signal at 1V rms output with no AGC, and at 250mV rms input with full AGC. The input and output admittances of the circuits are not greatly affected by AGC level.

#### **CIRCUIT APPLICATIONS**

There are seven connections to each circuit: an input, an input bias point, an AGC input, the output, the positive supply pin and two earths — for input and output respectively.

The positive supply should be 6V, but the devices will function at supplies of up to 9V. Since internal HF supply decoupling is incorporated a certain amount of HF ripple can be tolerated in the supply. LF ripple should be kept down as it can cause intermodulation — especially at large HF signal levels — and 10mV rms of LF ripple should be considered a maximum.

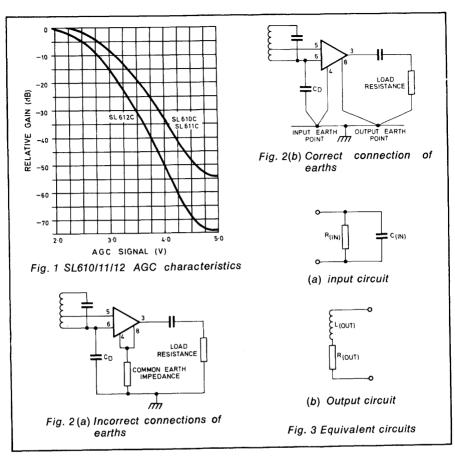

The AGC characteristic is shown in Fig. 1. It is temperature dependent, so that while a potentiometer may be used to provide a gain control voltage the gain so defined will not be temperature stable to better than  $\pm$  2dB. The AGC terminal will normally draw about 200 microamps at 5V — in some SL610C and SL611C devices this may be as high as 600 microamps.

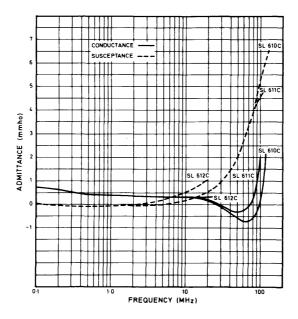

There are two earth connections: pin 4 is the input earth and pin 8 the output earth. When several devices are cascaded pin 8 of one stage and pin 4 of the next should have a common earth point — also high common earth impedances to pin 4 and pin 8 of the same device should be avoided. Fig. 2a shows a circuit where common earth impedance could cause instability and Fig. 2b shows one where the input and output signals have correct point earthing. If extra supply decoupling is used the capacitor should ground to the output earth point. The can should be separately earthed in applications at VHF or in the presence of a large RF field.

The input bias point (pin 6) is normally connected directly to the input (pin 5) and the signal applied through a capacitor but occasionally, when the signal is obtained from a tap on a coil, the arrangement in Fig. 2b may be used to give slightly improved noise performance.  $C_D$  is a decoupling capacitor. The SL610/611 noise figure is approximately 4dB at 300 ohms source impedance and 6dB at 50 ohms and at 2.5 kilohms the noise figure for the SL612 is 3dB at 800 ohms source impedance.

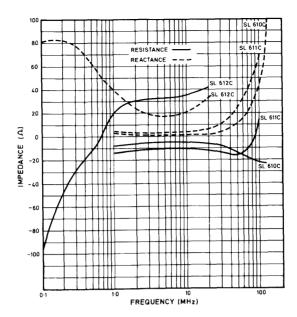

Both the input admittance  $G_{11}$  and the output impedance  $G_{22}$  have negative real parts at certain frequencies. The equivalent circuits of input and output respectively are shown in Figs. 3a and 3b and the values of  $R_{\rm in}$ ,  $R_{\rm out}$ ,  $C_{\rm in}$  and  $L_{\rm out}$  may be determined for any particular frequency from the graphs Figs. 4 and 5. It will be seen that for the SL610C and the SL611C,  $R_{\rm in}$  is negative between 30 and 100MHz, and  $R_{\rm out}$  is negative over the whole operating frequency range. For the SL612C,  $R_{\rm in}$  is not negative and  $R_{\rm out}$  is negative only below 700kHz.

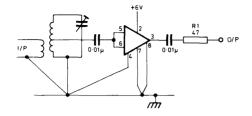

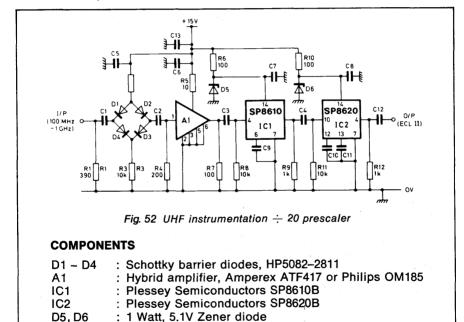

If an inductive element having inductance L1 and parallel resistance R1 is connected across the input, oscillation will occur if  $R_{\rm in}$  is negative at the resonant frequency of  $C_{\rm in}$  and L1, and if R1 is higher than  $R_{\rm in}$ . Similarly, if a capacitor C1 in series with a resistance R2 is connected across the output oscillation will occur if, at the resonant frequency of  $L_{\rm out}$  and C1,  $R_{\rm out}$  has a negative resistance greater than the positive resistance R2. Where the input is inductive, therefore, it may be shunted by a 1k resistor; where the load is capacitive, 47 ohms should be placed in series with the output.

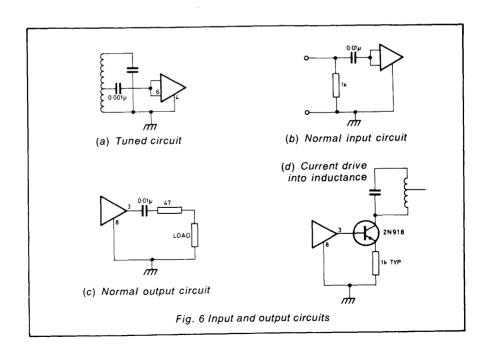

Suitable input arrangements for the amplifiers are shown in Fig. 2b and Fig. 6. The method shown in Fig. 6a is representative of all inputs — the input and bias points are directly-connected and the signal is coupled via a capacitor. If the input is inductive the 1k resistor shown in Fig. 6b may be required, although usually it can be omitted. If a crystal filter is used it should be correctly terminated, allowing for the impedance of the IC, and coupling made via a capacitor.

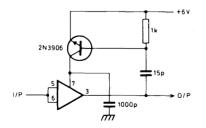

Fig. 4 Input admittance with olc output (G11)

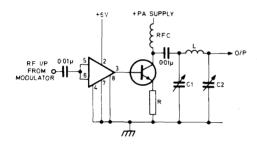

The output is a voltage source, with the impedance characteristics mentioned above. Output coupling is via a capacitor, with a series resistor if necessary to preserve stability (Fig. 6c). If a current output to a tuned circuit is required the arrangement in Fig. 6d is suitable, using almost any small signal NPN transistor with an  $f_T$  of over 300MHz and low  $C_{OB}$ . To drive particularly low impedances, e.g. a 50 ohm coaxial cable, this impedance should be increased somewhat by a series output resistor (say, 100 ohms) as, if the output is loaded directly by low impedance, most of the negative feedback will be removed — with consequently poor linearity and constancy of gain. Examples of the use of these amplifiers are shown in Fig. 7.

Fig. 5 Output impedance with s/c input (G22)

(a) RF preamplifier. Use SL610C up to 140MHz, SL611C up to 70MHz, SL612C up to 12MHz. R1 may be omitted if the load is neither capacitive nor very low impedance.

(b) Linear power amplifier for low power SSB transceivers. L, C1 and C2 form the output π tank circuit. The values of PA supply and R should be chosen to suit the transistor used. Cob should be as low as possible.

(c) Constant level RF amplifier stabilising at approximately 500mV rms output over a range of inputs greater than 20dB. SL610C, 611C or 612C may be used. With tuned feedback, this circuit makes an excellent constant level oscillator.

Fig. 7 SL610/11/12

## SL640C, SL641C, SL1640C & SL1641C

#### **Double balanced modulators**

#### PRINCIPLES OF OPERATION

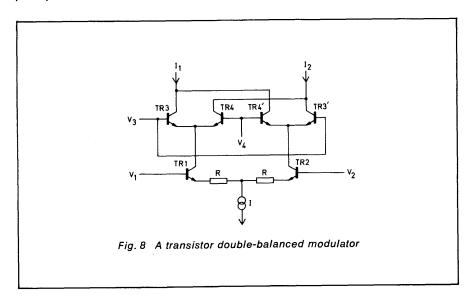

A simple double-balanced modulator is shown in Fig. 8 . It is evident that the sum of the two output currents equals the tail current and that, from considerations of symmetry, if either V1=V2 or V3=V4 then I1=I2. Also if R is much greater than  $R_{\rm e}$  the collector currents of TR1 and TR2 will differ by an amount proportional to the difference between V1 and V2. If, therefore, a small input at frequency f1 is applied between V1 and V2 and a large signal at f2 is applied between V3 and V4, sufficient to turn the transistors TR3, TR3, and TR4, and TR4, fully on and off, it is evident that switching modulation, similar to that of a diode ring will occur and frequencies If1  $\pm$ 12 I will occur at the output as will sums and differences of f1 and the odd harmonics of f2 i.e. If1  $\pm$ 3f2 I,1f1  $\pm$ 5f2 I, etc.

#### CIRCUIT DESCRIPTION AND APPLICATIONS

The circuits of the SL640C and SL641C are very similar but have different signal input and output configurations — these are fully discussed below.

The circuits require a single, well-decoupled positive supply of between 6 and 9 volts and consume about 12mA. Pin 2, an internal bias point, must also be decoupled by a low-leakage (less than 100nA) capacitor having a low reactance at the lowest signal or carrier input frequency.

Pin 1, which is connected to the can, should be earthed to prevent HF pickup.

The input and carrier signals, which should not exceed 200mV rms, are applied to pins 7 and 3 respectively. Both the SL640C and the SL641C have a carrier input impedance of 1 kilohm and 4pF and the SL641C has a similar signal input impedance. The signal input impedance of the SL640C is 500 ohms and 5pF. The input coupling capacitors should have a leakage of less than 100nA and an impedance of less than 100 ohms at the lowest frequency they will carry. This should be reduced to less than 10 ohms above 10MHz.

The output of the SL641C is intended as a current drive to a tuned circuit. If both sidebands are developed across this load its dynamic impedance must be less than 800 ohms. If only one sideband is significant this may be raised to 1600 ohms and it may be further raised if the maximum input swing of 200mV rms is not used. The DC resistance of the load should not exceed 800 ohms. If the circuit is connected to a +6V supply and the load impedance to +9V, the load may be increased to 1.8 kilohms at AC or DC. This, of course, increases the gain of the circuit.

There are two outputs from the SL640C; one is a voltage source of output impedance 350 ohms and 8pF and the other is the emitter of an emitter follower connected to the first output, which requires a discrete load resistor of not less than 560 ohms. The emitter follower output should not be used to drive capacitive loads as emitter followers act as detectors under such circumstances with resultant distortion and harmonic generation. Frequency-shaping components may be connected to the voltage output and the shaped signal taken from the emitter follower.

The circuits will operate with input frequencies between 1Hz and 70MHz with the specified performance; the SL641C will operate at up to about

150MHz with reduced performance. To use them at frequencies below 100Hz precautions must be taken to prevent leakage in the input coupling capacitor from altering the device bias.

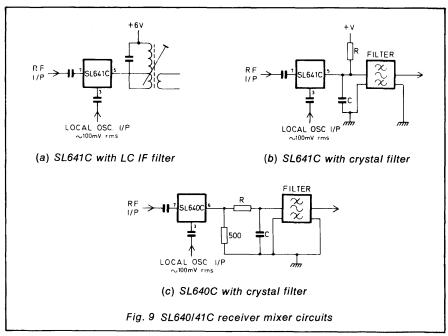

Some applications of the SL640C and SL641C are shown in Figs. 9 and

10 Power, decoupling, and earth connections are not shown.

Fig. 9a shows the SL641C used as a receiver mixer driving a wound IF coil. Fig. 9b shows it driving a crystal filter. R and C must be selected to match the filter. If R is less than 800 ohms it may be connected to the +6V line supplying power to the SL641C; if it is between 800 ohms and 1.8 kilohms it should be connected to +9V (while the SL641C supply must remain at +6V). If R is greater than 1.8 kilohms the circuit in Fig. 9 b is unsuitable and the SL640C circuit illustrated in Fig. 9 c should be used.

The SL640C and SL641C have a noise figure of about 10dB at 100 ohms source impedance. When used as receiver mixers they have better than —40dB intermodulation products so long as unwanted signals do not exceed 30mV rms. Thus, either can be used as a receiver mixer at HF without an RF amplifier since atmospheric noise will far exceed device noise at these frequencies if the antenna is reasonably good. If an SL610C RF amplifier is used the intermodulation threshold will be reduced to 3mV rms (since the SL610C has a gain of 10). The SL640/41 is then less attractive as a mixer and a diode ring mixer should be used.

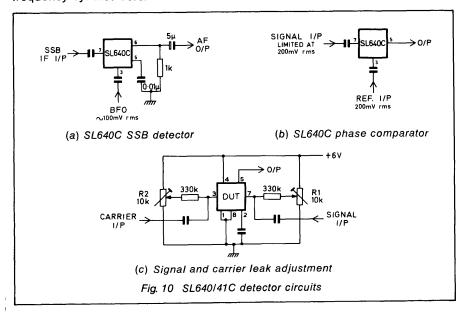

Fig. 10 a shows the SL640C used as an SSB detector. The capacitor connected to output pin 5 decouples the sum frequency If1  $\vdash$  f2l, while the audio difference frequency If1  $\vdash$  f2l is taken from pin 6. The phase comparator shown in Fig. 10b is more useful  $\vdash$  it may be used as a detector for phase modulated signals or as a comparator in phase-locking systems such as frequency synthesisers.

Signal and carrier leak may be reduced by altering the bias on the carrier and signal input pins, as shown in Fig. 10c. With carrier but no signal R1 is adjusted for minimum carrier leak. A similar network is connected to the carrier input and with signal and carrier present, signal leak is minimised by means of R2.

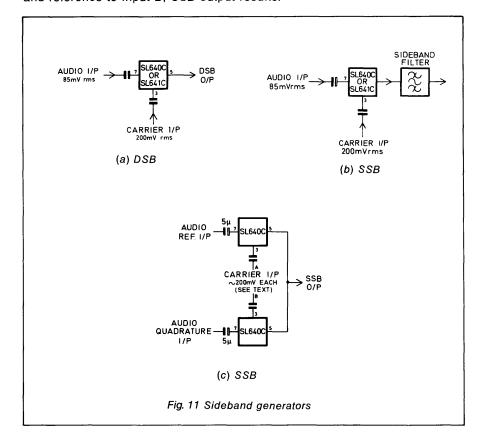

Fig. 11a shows the SL640C or SL641C used as a sideband generator. Both sidebands are produced so that if a single sideband is required it must be obtained by subsequent filtering (Fig. 11b). If pin 2 is earthed by a resistor of about 15 kilohms (its actual value may need to be selected) the device's carrier leak is increased to a point where the DSB signal becomes AM. This is useful where it is desired to select sideband or AM. In the circuit shown in Fig. 11c a single sideband only is produced. It is important that both the audio and carrier reference and quadrature signals should be accurately 90 degrees out of phase. The amplitude of one phase of audio should be adjusted to obtain maximum second sideband rejection.

If the carrier reference is connected to input A, and the carrier quadrature to input B, LSB output results. If the carrier quadrature is connected to input A, and reference to input B. USB output results.

## SL621C & SL1621C

#### AGC generators

The SL621C is an audio-operated AGC generator designed for use with the SL610/11/12 RF amplifiers in SSB receivers.

An ideal single sideband AGC generator must set the AGC rapidly when a new signal appears and follow a rising or fading signal but, if the signal disappears altogether (as in pauses in speech), retain the AGC level until the signal recommences. If the signal remains absent for more than a preset time, however, the system should rapidly revert to full gain. The SL621C will perform these functions and will also produce short-lived pulses of AGC to suppress noise bursts.

#### CIRCUIT DESCRIPTION

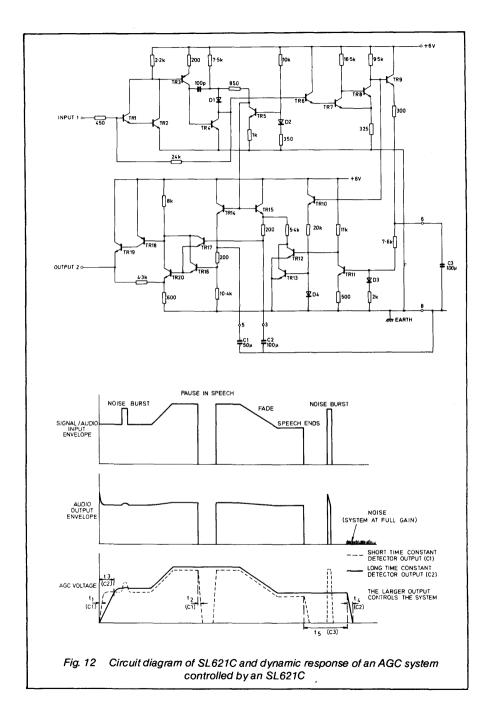

The operation of the circuit is described with reference to Fig. 12, which also illustrates the dynamic response of a system controlled by an SL621C AGC generator.

The SL621C consists of an input AF amplifier, TR1-TR4, coupled to a DC output amplifier, TR16-TR19, by means of a voltage back-off circuit, TR5, and two detectors, TR14 and TR15, having short and long rise and fall time constants respectively.

An audio signal applied to the input rapidly establishes an AGC level, via TR14, in time t<sub>1</sub>. Meanwhile the long time constant detector output (TR15) will rise and after t<sub>3</sub> will control the output because this detector is the more sensitive. If the signals at the SL621C input are greater than approximately 4mV rms they will actuated the trigger circuits TR6-TR8 whose output pulses will provide a discharge current for C2 via TR10, TR13.

By this means the voltage on C2 can decay at a maximum rate which corresponds to a rise in receiver gain of 20dB/sec. Therefore the AGC system will smoothly follow signals which are fading at this rate or slower. However, should the receiver input signals fade faster than this, or disappear completely as in pauses in speech, then the input to the AGC generator will drop below the 4mV rms threshold and the trigger will cease to operate. As C2 then has no discharge path, it will hold its charge (and hence the output AGC level) at the last attained value. The output of the short time constant detector (TR14) falls to zero in time  $t_2$  after the disappearance of the signal.

The trigger pulses also charge C3 via TR9, thus holding off TR12 via TR11. When the pulses cease, C3 discharges and after  $t_5$  turns on TR12, rapidly discharging C2 (in time  $t_4$ ) thus restoring full receiver gain. The hold time,  $t_5$ , is approximately one second with C3=100 microfarads. If signals reappear during  $t_5$ , then C3 will re-charge and normal operation will continue. The C3 re-charge time is made long enough to prevent prolongation of the hold time by noise pulses. Fig. 12 also shows how a noise burst superimposed on speech will initiate rapid AGC action via the short time constant detector while the long time constant detector effectively remembers the pre-noise AGC level.

The various time constants quoted are for C1=50 microfarads and C2=C3=100 microfarads. These time constants may be altered by varying the appropriate capacitors.

#### **CIRCUIT APPLICATIONS**

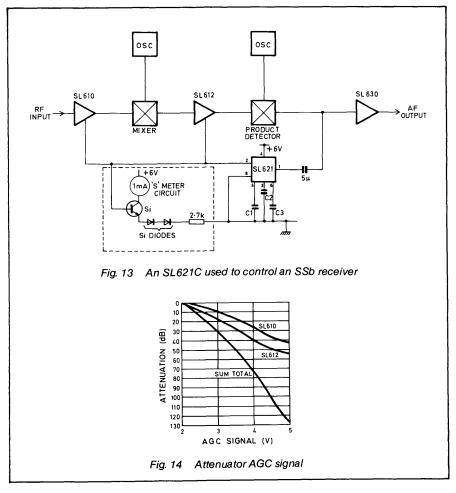

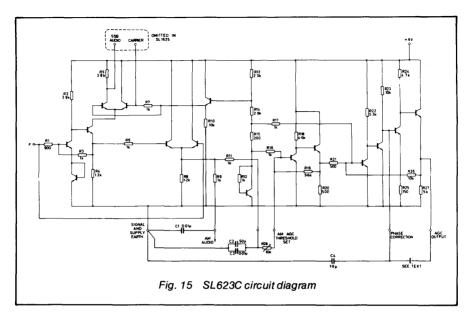

The SL621 is used in an SSB receiver as shown in Fig. 13. AGC need only be applied to two of the gain stages even if there are more than two such stages in the receiver since AGC applied to two stages only will result in over 120dB AGC range. It is usual to apply AGC to the first RF stage and the first IF stage and it will be seen from Fig. 14 that an SL612 IF amplifier reacts earlier to an increasing AGC voltage than an SL610C RF amplifier. This has the effect of delaying the AGC to the input stage, thus improving the receiver signal to noise ratio at low AGC levels.

Fig. 14 also shows the total attenuation to be expected at any AGC voltage when AGC is applied to one SL610C and one SL612C in a system; from this one can calculate the calibration of an 'S' meter for use with the SL621C. Such a meter, as shown in Fig. 13, should have a sensitivity of 2.6V FSD and be calibrated linearly from 0 to 120dB.

The output current capability of the SL621 is not high and it should not be expected to drive more than three SL610/11/12 devices in addition to an 'S' meter circuit similar to that shown in Fig. 13.

There are two other important points to observe when using the SL621C: supply de-coupling and input coupling. Since capacitors C1 and C3 may need to charge very quickly, the source impedance of the 6V supply line at low frequencies should be very low, if necessary being decoupled by a low impedance 1000 microfarad capacitor placed near the SL621C.

The input should be applied to pin 1 via a capacitor of not more than 470 ohms reactance at the lowest input frequency encountered, and should never exceed 1Vrms. Input voltages in excess of this level may cause the internal amplifier to block, with consequent failure of the AGC voltage. The condition can be avoided, if necessary, by using a diode limiter at the input.

In the presence of RF fields the AGC line may need to be decoupled: a 5000pF capacitor from pin 7 of each RF amplifier to earth and a 100 ohm resistor from each pin 7 to the AGC line should be adequate. It is, however, important not to use a capacitance greater than 15000pF, otherwise the impulse suppression characteristic of the circuit will be degraded.

The SL621 may be used with supply voltages between +6V and +9V.

## SL623C, SL1623C & SL1625C

#### AM detector, AGC amplifier and SSB demodulators

The SL623C consists of an AM detector, an SSB detector and an AGC generator designed for use with AM. The SL623C was introduced to enable the small-signal sections of an HF AM/SSB transceiver to be completely integrated — all functions with the exception of the power amplifier can be realised with SL600 series integrated circuits. The outputs of the SL623C will drive most audio output stages with input impedances over 10 kilohms, and are particularly suitable for driving the SL630C.

In addition to its audio outputs, the SL623C AGC generator is designed to control SL610/11/12 RF/IF amplifier strips, but, unlike the SL621C AGC generator, which operates from an audio signal, the SL623C control voltage is carrier-derived. It is therefore less suitable for use with SSB or CW. However, the AGC output pins of an SL621C and an SL623C may be connected together for an SSB/AM receiver, the gain then being controlled by the device with the higher output voltage.

The SL1625C is an SL1623C without its SSB detector.

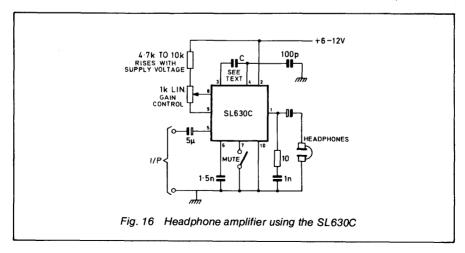

#### **CIRCUIT DESCRIPTION (Fig. 15)**

The IF input is applied directly to one input of a full-wave detector and, via a unity-gain inverting amplifier, to the other input of the full-wave detector and to the signal input of a balanced demodulator. Two outputs from the full-wave detector are brought out of the package: audio and AGC. The AGC signal is used as the input to the AGC amplifier of the device. The AGC amplifier consists of two amplifiers in series. The first has a gain which may be varied between —0.25 and —5 by an external resistor and the second has a fixed gain of —20 and a frequency compensation point. The SSB detector, which requires a carrier input of 100mV rms, consists of a simple balanced demodulator.

A single positive supply of between  $+6\mathrm{V}$  and  $+9\mathrm{V}$  is required. The supply should be decoupled close to the can by a 0.1 microfarad capacitor. Current consumption is approximately 10mA at 6V supply and zero AGC voltage, but rises with both supply voltage and AGC output level.

#### CIRCUIT APPLICATIONS

#### **AM Detector**

The detected AM output has an output impedance of about 1 kilohm and should be decoupled at RF with a 0.01 microfarad capacitor (C1). It should be connected to the audio stage via a dc blocking capacitor. The other detector output is similar but should be decoupled with a 50 microfarad capacitor (C2) to remove AF, and connected via a preset potentiometer R28 to the AGC amplifier input to provide rectified carrier for amplification as AGC. C1 and C2 should be connected directly to the earth pin via the shortest possible leads, which should not be common to any other components. C2 should have an AF series resistance of under 1 ohm and, if it does not also have a low RF impedance, should be shunted by a 0.01 microfarad RF bypass capacitor (C3). These measures prevent instability due to possible RF current loops.

#### **AGC** Generator

Pin 3, the AGC amplifier phase correction point, should be decoupled to ground by a 1 microfarad capacitor (C4) ,keeping leads as short as possible. The value of C4 is quite critical, and should not be altered: if it is increased the increased phase shift in the AGC loop may cause the receiver to become unstable at LF and if it is reduced the modulation level of the incoming signal will be reduced by fast-acting AGC.

A capacitor connected to the phase correction point and the output of the AGC amplifier helps to reduce the ripple on the AGC output. Its value varies from system to system and with intermediate varying frequencies. Normally-used values vary between 0.1 and 10 microfarads. As there is no easy way to predict suitable values for particular systems, this component must be 'selected on test'.

The AGC output (pin 4) will drive at least two SL610/11/12 amplifiers and the 'S' meter circuit shown in Fig. 13. The SL623 AGC output is an emitter follower similar to that of the SL621C. Hence the outputs of the two devices may be connected in parallel when constructing AM/SSB systems.

Less signal is needed to drive the SSB demodulator than the AM detector. In a combined AM/SSB system, therefore, the signal will automatically produce an SSB AGC voltage via the SL621C as long as a carrier (BFO) is present at the input to the SSB demodulator of the SL623C. The AGC generator of the SL623C will not contribute in such a configuration.

For AM operation the BFO must be disconnected from the carrier input of the SSB demodulator. In the absence of an input signal, the SL621C will then return to its quiescent state. To switch over a receiver using the SL623C from SSB to AM operation it is therefore necessary to turn off the BFO and transfer the audio pick-off from the SSB to the AM detector.

Neglecting to disconnect the SSB carrier input during AM operation can result in heterodyning due to pick-up of carrier on the input signal. In some sets different filters are used for AM and SSB; these will also need to be switched.

The 10 kilohm gain-setting preset potentiometer R28 is adjusted so that a DC output of 2 volts is achieved for an input of 125mV rms. There will then be full AGC output from the SL623C for a 4dB increase in input. A fixed resistor of 1.5 kilohms can often be used instead of the potentiometer.

#### SSB Demodulator

The carrier input is applied to pin 6, via a low-leakage capacitor. It should have an amplitude of about 100mV rms and low second harmonic content to avoid disturbing the DC level at the detector output.

Pin 8 is the SSB output and should be decoupled at RF by a 0.01 microfarad capacitor. The output impedance of the detector is 3 kilohm and the terminal is at a potential of about +2V which may be used to bias an emitter follower if a lower output impedance is required. The input to the audio stage of a receiver using an SL623C should be switched between the AM and the SSB outputs — no attempt should be made to mix them. Since the SL621C is normally used in circumstances where low-level audio is obtained from the detector, the relatively high SSB audio output of the SL623C must be attenuated before being applied to the SL621C. This is most easily done by connecting the SL623C to the SL621C via a 2 kilohm resistor in series with a 0.5 microfarad capacitor.

#### **Input Conditions**

The input impedance is about 800 ohms in parallel with 5pF. Connection must be made to the input via a capacitor to preserve the DC bias. An input of about 125mV rms is required for satisfactory carrier AGC performance and 20mV rms for SSB detection. Normally, the AGC will cope with this variation but in an extreme case a receiver using an SL623C and having the same gain to the detector in both AM and SSB modes will be some 10dB less sensitive to AM.

## **SL630C**

#### Microphone/headphone amplifier

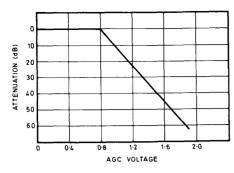

The SL630C is an audio amplifier having 40dB gain and an internal gain control of approximately 60dB, and an output capability of 200mW into a 40 ohm load when used with a 12V supply.

#### CIRCUIT DESCRIPTION AND APPLICATIONS

To maintain HF stability — particularly on negative half-cycles — the output (pin 1) should be decoupled by a 1,000pF. low series inductance. capacitor placed directly between pins 1 and 10 (8) with leads cut as short as possible. This component must be on the integrated circuit side of the output coupling capacitor. At high supply voltages and/or low temperatures 10 ohms must be placed in series with this capacitor and 100pF connected from pin 4 to earth. The output is coupled to its load with a capacitor of a low impedance relative to the load at the lowest frequency to be used. The load may be resistive or reactive and, for maximum power output, should lie on the load/supply voltage line. Any higher value of load impedance is quite safe but the device will over-dissipate and eventually destroy itself by overheating if the output is short-circuited. The optimum load therefore, at any rate with supplies of over 9V, can be regarded as a safe minimum. The circuit shown in Fig. 16 which shows the SL630C used as a headphone amplifier, may also be used with loudspeakers having suitable impedances. The distortion is about 0.5 per cent at full output.

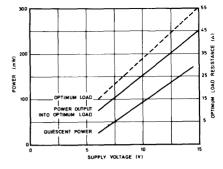

The power supply, to pin 2, should be between +6V and +12V and adequately decoupled both at HF and LF. The quiescent power consumption at various supply voltages is shown in the Power characteristics, as is the relation of the supply voltage to the optimum load and the maximum power available.

Fig. 17 AGC characteristics

Fig. 18 Power characteristics

A capacitor connected to pins 3 and 4 defines the high frequency response of the amplifier. The upper 3dB frequency, f, is given by the formula:

$$f = \frac{16000}{C + 20}$$

kHz. (C is in picofarads)

Pins 5 and 6 are input terminals. They may be used together as a differential input, in which mode they present an impedance of approximately 2 kilohms and result in a voltage gain (without gain control) of 100 (40dB). When the input is obtained from a magnetic transducer or a transformer it is desirable to use the differential input mode since the signal winding may be connected directly between pins 5 and 6 and no other components are required.

An input may also be applied between pin 5 and earth. In this case the gain is 200 (46dB) and the input impedance 1 kilohm. Pin 6 should be earthed by 1500pF. A coupling capacitor is required between the input and pin 5.

The circuit is muted by earthing pin 7. A muted circuit attenuates an input by about 100dB.

Gain control is applied to pin 8, which has an input impedance of 3.6 kilohms. It must be appreciated that even with full gain control the input cannot exceed 50mV rms without clipping so that at high control levels the output level is limited. The AGC characteristics will vary with temperature but, as shown in Fig. 16 a potentiometer to give manual gain control can be connected to the internal bias point at pin 9 which provides a temperature-compensated reference at the voltage at which gain control commences. Pin 10 is the signal earth and negative power supply connection.

## Application—SL600 Series

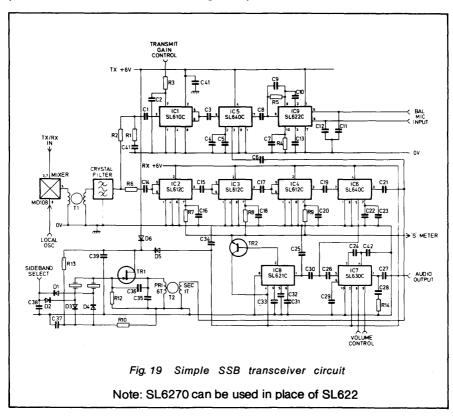

#### SSB TRANSCEIVER USING SL600 SERIES

This transceiver, shown in Fig.19, consists of a single conversion superhet receiver with a 9MHz IF and a very efficient audio-derived AGC system, and a filter type SSB generator, also working at 9MHz. Audio AGC in the modulator path gives constant level output. The transmitter and receiver are arranged so that no signal switching is required between transmit and receive, and the RF components are common to both.

The RF input is direct to an Anzac MD-108 (or similar) hot carrier diode ring mixer. This has 50 ohm ports and is also driven by the local oscillator, at about +7dBm (500mV). The output is connected via a 3: 1 step-up transformer to a 9MHz crystal filter. This filter has the 2.4kHz bandwidth required for SSB and a 90dB stopband. Filters with 60dB stopband can be used, but additional filters may be required at low local oscillator frequencies to keep the local oscillator signal out of the IF amplifier (and the overall receiver performance will, of course, be degraded).

The filter used, an SEI QC1246AX or a KVG XF9-B, has a terminating impedance of 500 ohms, but only within the passband of the filter. At frequencies outside the passband it may be very different, which means that the impedance that the filter presents to the diode ring mixer via the transformer will vary from 50 ohms. Such a mismatch will degrade the cross-modulation and carrier leak performance of the diode ring. However, it was decided on balance, that it was better to tolerate such degradation — which is not excessive — than to complicate the design by incorporating a broadband impedance match (which would probably not be bidirectional and hence would have to be switched between transmit and receive).

The present design allows the same arrangement to operate in opposite directions during receive and transmit without any switching. On the other side of the crystal filter the transmit and receive signal paths diverge but are still not switched.

#### The Receiver

The incoming RF signal is mixed with the local oscillator in the mixer described above and then passes through an SSB bandwidth 9MHz crystal filter. It is then amplified by three cascaded SL612CIF amplifiers, IC2, 3 and 4. These amplifiers are untuned and since the strip has a maximum gain of 102dB careful attention must be paid both to noise and to stability. The SL612C has a 3dB noise figure which means that the broadband noise at the output of the three-stage strip is about 10mV RMS. This is not sufficient to affect a product detector, which is only concerned with the component within a few kHz of the BFO frequency, but would cause trouble if a diode detector were to be used.

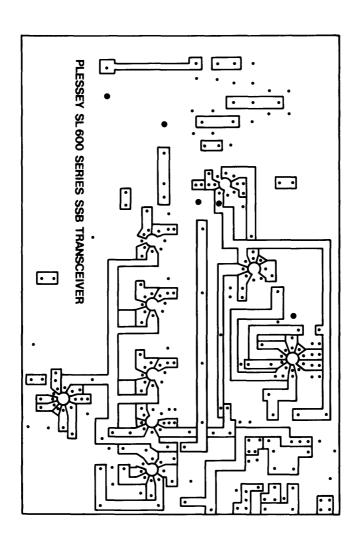

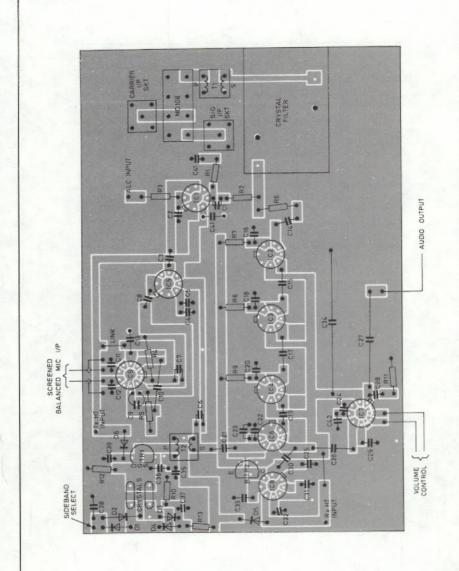

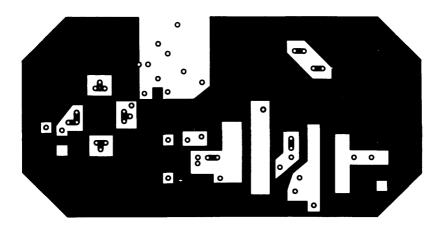

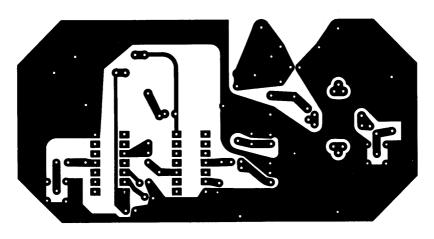

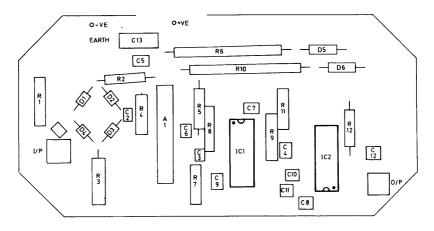

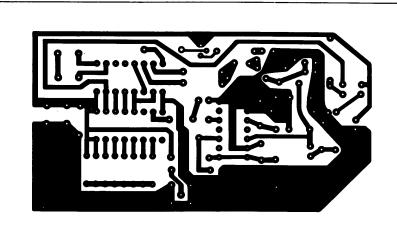

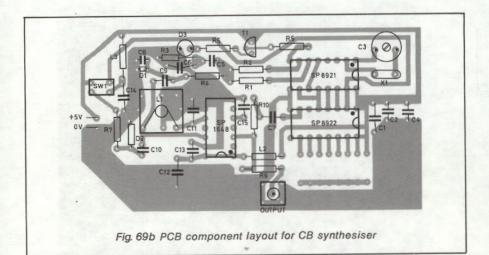

A broadband amplifier with 102dB gain is a likely candidate for stability problems. The three-stage strip used in this receiver is less liable to power supply feedback than most since the SL612C has internal supply decoupling. Nevertheless it must be carefully laid out to minimise earth loops and input/output feedback. The simplest way to do this is to use a double-sided printed circuit board with the components side a continuous ground plane to which all earth connections are made. If this is done the layout on the conductor side of the board is not very critical but if single-sided board is used with the earth conductors on the same side as the other conductors then it does become so. The design of board in Fig. 20 is the most stable layout yet developed for such strips on single-sided board, and it is strongly recommended that it be copied exactly.

There are two other possible causes of instability in this transceiver: inadequate supply switching and inadequate supply decoupling. Since the only onboard transmit/receive switching is by means of power switching it is essential that the transmit supply be not only isolated but earthed during receive, and vice versa. Both supplies should also be well decoupled at RF.

The IF strip has AGC applied to it by an SL621C audio AGC circuit, IC8.AGC is applied via an emitter follower, which has the effect of reducing the AGC range of each SL612C by 0.7V. The overall AGC range could be reduced to less than 90dB were only two SL612Cs to have AGC applied to them. AGC is therefore applied to all three to give 130dB, of which the usable AGC range is about 115dB.

The IF output is applied to an SL640C double-balanced modulator (IC6), used here as a product detector. When AGC is operating, the audio output of

the detector is about 10mV RMS. The audio is fed to IC7, an SL630C audio amplifier which has a voltage gain control. The SL630C can supply up to about 60mW to headphones, to a small loudspeaker or to an external amplifier.

The detected audio also goes to the SL621C audio AGC system (IC8). This has an ideal characteristic for SSB reception. It operates from the receiver audio, not from RF, and it has fast attack and fast decay unless a signal disappears altogether — as in speech pauses — when it does not decay at all for a second and then, if the signal has not reappeared, decays quickly. This enables it to track rising or fading signals but prevents it overloading after each brief speech pause. The circuit also incorporates very fast AGC action to suppress brief noise bursts.

An FET oscillator is used to supply carrier to the product detector and to the double-balanced modulator in the transmitter. The voltage applied to the 'sideband select' terminal determines which crystal is used — upper or lower sideband — but the terminal must not be left unconnected: it must either be connected to +6V or to earth. The oscillator is supplied via diodes from both the transmit and receive lines so that it continues to operate on transmit or receive.

The most basic receiver does not have an 'S' meter but if one is required it may be connected to the emitter of the AGC buffer transistor. It should consist of a moving coil meter connected in series with a resistor such that FSD corresponds to 2.5V and three forwardbiased silicon diodes. This 'S' Meter circuit has a rather compressed scale for signals more than 40dB above the AGC threshold.

This receiver has a sensitivity of 1.0 microvolts for 10dB S/N. This means that at HF with adequate antennas no RF amplifier is required since atmospheric noise will limit system performance. At higher frequencies, or in systems where small antennas are used, RF gain may be necessary to prevent the performance being gain-limited rather than noise limited. Such amplifiers increase gain but degrade intermodulation performance. In general, without the RF amplifier, the receiver will tolerate about 200mV of adjacent channel signal on the mixer without significant intermodulation. This is, of course, a property of the mixer rather than of the rest of the circuit, although the filter characteristics are also involved.

#### The Transmitter

The transmitter uses the standard filter method of generating SSB. Audio from the microphone is fed to an SL622C microphone amplifier (IC9), which has AGC giving a constant 100mV output over 60dB of input. The AGC ensures an almost constant output from the transmitter, but can be inconvenient in noisy environments when the transmitter will give full modulation on noise in the absence of a speech input. Such noise modulation is avoided by the addition of a single extra resistor (R5, between pins 8 and 9 of the SL622C) which reduces the dynamic range of the AGC.

The constant-level audio from IC9 is applied to the signal input of an SL640C double-balanced modulator (IC5). The output of the FET carrier oscillator is applied to the carrier input of IC5 and a double sideband suppressed carrier signal appears at its output. Carrier suppression is of the order of 40dB.

This DSB signal is amplified in an SL610C (ICI). The AGC pin of ICI is brought out from the board and may be used either to preset the system gain or as an ALC connection. The amplified DSB from IC1 is then passed through

the crystal filter, which removes one sideband, leaving SSB. The SSB is mixed to the final transmitter frequency in the diode ring mixer and then goes to a linear amplifier which raises it to the transmitter output level. The output from the diode ring is, of course. lower than the input to the filter and is about 100mV or less into 50 ohms.

The output of IC5 and the input of the first SL612C (IC2) are connected to the same point on the filter via resistors. R6 is merely a buffer resistor but R2 and R1 set the impedance which the filter sees in operation. This varies from 480 ohms on transmit to about 530 ohms on receive, but this small variation does not affect filter performance. The loading effects of a turned-off SL612C during transmission and a turned-off SL610C during reception are similarly insignificant.

The transmitter output (at the diode ring) consists of an SSB signal with carrier below — 55dB and opposite sideband below — 60dB, provided that the carrier oscillator is at the correct frequency. The degree of off-channel spurious signals depends on the crystal filter used: 90dB stopband type gives excellent performance but a cheaper one can sometimes cause trouble.

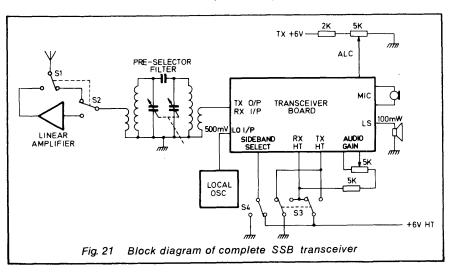

#### The Transceiver

The transceiver board needs few extra sub-systems to make a complete transceiver. They are: a power supply, microphone, volume control and loud-speaker and also a filter, local oscillator and linear amplifier. These are connected as shown in Fig. 21.

Much of the performance of the final system will depend upon the standard of design of the local oscillator, pre-selector, RF amplifier (if used) and linear amplifier, but the performance of the transceiver board itself is excellent. The Anzac MD-108 mixer used is capable of the required performance between 10kHz and 500MHz. If other diode rings were used the transceiver might be used over an even wider range. Its power consumption is about 400mW on either transmit or receive.

The most attractive feature of this transceiver, despite its high performance, is its simplicity. It uses only 80 components and contains no tuned circuits or other components requiring adjustment. It was designed for two purposes: (a) to demonstrate the usefulness and versatility of the SL600 Series in SSB applications and (b) as a ready-engineered SSB transceiver suitable for those inexperienced in SSB design. It is capable of giving good performance but can be constructed and commissioned by relatively inexperienced personnel.

#### **Physical Construction**

The board and component layouts are shown in Fig. 20. The board is single-sided and there are two jumper links on it carrying power supplies. As mentioned above the layout on a single-sided board carrying such a high gain broadband IF strip is critical and it should not be changed. All passive component leads should be as short as possible and integrated circuits should not be mounted more than 6mm above the board.

The two transformers T1 and T2 are both wound on small toroids of high frequency ferrite. The exact size and material are not important but the material must be low loss up to at least 45MHz and it is essential that it has a linear B/H characteristic, otherwise it will cause intermodulation at the receiver

Fig. 20a Copper side of PCB for simple SSB transceiver

Fig. 20b PCB for simple SSB transceiver

input. T2 is a simple transformer with a six-turn primary and a single turn secondary but T1 is more complex. T1 is made from four 5cm lengths of 26 SWG (0.46mm dia.) enamelled copper wire twisted together. The length of twist is used to wind two turns on the toroid and the ends are separated. Three lengths are then connected in series in the same sense to form the filter winding and the last length is used as the diode ring winding.

There are few other constructional details that need mentioning, but if a receiver without a transmitter is required one may be built by omitting the three transmitting integrated circuits (SL610C, SL622C and the SL640C) between them), R1 to R5 inclusive and C1 to C13 and C40. To preserve the filter impedance match a 500 ohm resistor should be connected from the filter side of R6 to earth.

| Component | Value         | Rating             | Туре                           |

|-----------|---------------|--------------------|--------------------------------|

| R1        | 100           | 1/8 W              | Hi-Stab.                       |

| R2        | 430           | 1/8 W              | Hi-Stab.                       |

| R3        | 100           | 1/8 W              | Hi-Stab.                       |

| R4        | 680K          | 1/8 W              | Hi-Stab.                       |

| R5        | 1K            | 1/8 W              | Hi-Stab.                       |

| R6        | 50            | 1/8 W              | Hi-Stab.                       |

| R7-R9     | 100           | 1/8 W              | Hi-Stab.                       |

| R10       | 330           | 1/8 W              | Hi-Stab.                       |

| R11       | 10            | 1/8 W              | Hi-Stab.                       |

| R12       | 100K          | 1/8 W              | Hi-Stab.                       |

| R13       | 330           | 1/8 W              | Hi-Stab.                       |

| D1-D6     |               |                    | <sup>1N4148</sup> ) Or similar |

| TR1       | }             |                    | 2N3819 devices                 |

| TR2       |               |                    | 2N706 ) devices                |

| T1, T2    | See text.     |                    |                                |

| Mixer     | Anzac         | !                  |                                |

| [         | MD-108        |                    |                                |

| Crystals  | 9.0015 MHz &  | ,                  | Parallel (30p) resonant        |

|           | 8.9985 MHz    | Ì                  | ` ' '                          |

| IC1       | SL610C        | 1                  |                                |

| IC2-IC4   | SL612C        |                    |                                |

| IC5-IC6   | SL640C        |                    |                                |

| IC7       | SL630C        |                    |                                |

| IC8       | SL621C        | ļ                  |                                |

| IC9       | SL622C, SL627 | oc l               |                                |

| C1-C4     | 1nF           | 「 <sup>1</sup> 50∨ | Weecon (Min Ceramic)           |

| C5        | 10µF          | 6.3V               | Min. Tantalum                  |

| C6        | 100pF         | 50                 | Ceramic                        |

| C7        | 47µF          | 6.3V               | Min. Tantalum                  |

| C8        | 10µF          | 6.3V               | Min. Tantalum                  |

| C9        | 4.7nF         | 50V                | Weecon                         |

| C10       | 2µF           | 6.3V               | Min. Tantalum                  |

| C11-C12   | 1nF           | 50V                | Weecon                         |

| C13       | 100nF         | 50V                | Weecon                         |

| C14-C15   | 100pF         | 50V                | Ceramic                        |

| C16       | 4.7nF         | 50V                | Weecon                         |

|           | 7.7111        | 1 30 4             | 11360011                       |

Table 1 Components list for the Simple SSB Transceiver (Fig. 19)

| Component | Value | Rating | Туре            |

|-----------|-------|--------|-----------------|

| C17       | 100pF | 50V    | Ceramic         |

| C18       | 4.7nF | 50V    | Weecon          |

| C19       | 100pF | 50V    | Ceramic         |

| C20       | 4.7nF | 50V    | Weecon          |

| C21       | 100pF | 50V    | Ceramic         |

| C22       | 1nF   | 50V    | Weecon          |

| C23       | 10µF  | 6.3V   | Min. Tantalum   |

| C24       | 4.7nF | 50V    | Weecon          |

| C25       | 100nF | 50V    | Weecon          |

| C26       | 10μF  | 6.3V   | Min. Tantalum   |

| C27       | 100µF | 6.3V   | Min. Tantalum   |

| C28       | 10nF  | 50V    | Weecon          |

| C29       | 1nF   | 50V    | Weecon          |

| C30       | 1µF   | 6.3V   | Min. Tantalum   |

| C31       | 100μF | 6.3V   | Min. Tantalum   |

| C32       | 47µF  | 6.3V   | Min. Tantalum   |

| C33       | 100µF | 6.3V   | Min. Tantalum   |

| C34       | 400µF | 16V    | Min. Al. Elect. |

| C35-C36   | 68pF  | 50V    | Ceramic         |

| C37-C38   | 10nF  | 50V    | Weecon          |

| C39-C41   | 100nF | 50V    | Weecon          |

| C42       | 100pF | 50V    | Ceramic         |

Table 1 (continued)

#### Introduction to SL6000 Series

The Plessey Semiconductors SL6000 series of radio linear circuits extends the concept of the 'building block' approach to wider systems. Each device features advanced circuit techniques which result in higher levels of integration, lower power consumption or exceptional performance. All products are available in plastic and metal can or ceramic packages.

| SL6000 PRODUCT RANGE (AS AT 1st AUGUST 1979)   |                                                                                                                                                                                                        |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| IF AMPLI                                       | FIERS/DETECTORS                                                                                                                                                                                        |  |  |  |

| SL6600<br>SL6640<br>SL6650<br>SL6690<br>SL6700 | FM Double Conversion with PLL Detector<br>FM Single Conversion, audio stage (10.7MHz)<br>FM Single Conversion (10.7MHz)<br>FM Single Conversion, low power for pagers (455kHz)<br>AM Double Conversion |  |  |  |

| AUDIO<br>SL6270<br>SL6290<br>SL6310            | Microphone Amplifier with AGC to give 'constant' output SL6270 plus speech clipper, buffer and relay driver Switchable audio amplifier (400mW/9V/8ohms)                                                |  |  |  |

### SI 6600C

#### LOW POWER IF/AF PLL CIRCUIT FOR NARROW BAND FM

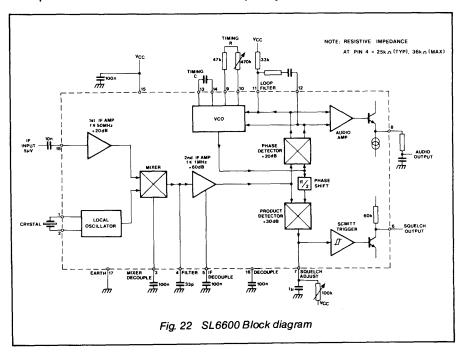

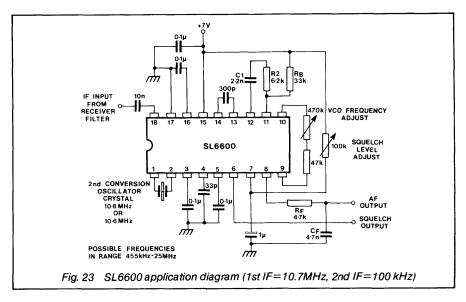

The SL6600 is a single or double conversion IF amplifier and detector for FM radio applications. Its minimal power consumption makes it ideal for hand held and remote applications where battery conservation is important. Unlike many FM integrated circuits the SL6600 uses an advanced phase locked loop detector capable of giving superior signal-to-noise ratio with excellent co-channel interference rejection, and operates with a second IF frequency of less than 1MHz. Normally the SL6600 will be fed with a first IF signal of 10.7 or 21.4MHz; there is a crystal oscillator and mixer for conversion to the second IF amplifier, a PLL detector and squelch system.

#### IF Amplifiers and Mixer

The SL6600 can be operated either as a single conversion circuit with a maximum recommended input frequency of 800kHz or in a double conversion mode with a first IF of the input frequency (50MHz max.) and a second IF of 100kHz or ten times the peak deviation, whichever is the larger. The crystal oscillator frequency can be equal to either the sum or difference of the two IFs; the exact frequency is not critical.

The circuit is designed to use series resonant fundamental crystals between 1 and 25 MHz.

When a suitable crystal frequency is not available a fundamental crystal of one third of that frequency may be used.

When a single conversion circuit is required a 6.8k resistor should be connected in place of the crystal and a further 2.7k resistor connected between pin 1 and earth. The overall gain of the circuit will be reduced by 12dB with this technique.

A capacitor connected between pin 4 and ground will shunt the mixer output and limit the frequency response of the input signal to the second IF amplifier. A value of 33pF is advised when the second IF frequency is 100kHz.

#### Phase Locked Loop.

The Phase Locked Loop detector features a voltage controlled oscillator with nominal frequency set by an external capacitor according to the formula (30/f)pF where f is the VCO frequency in MHz. The nominal frequency may differ from the theoretical but there is provision for a fine +10% frequency adjustment by means of a variable resistor between the VCO output pins; a value of 470k has negligible effect while 47k (recommended minimum value) increases the frequency by approx. 10%.

The loop filter is connected between pins 11 and 12; a 33k resistor is also required between pin 11 and Vcc.

The values of the filter resistor R2 and capacitor C1 must be calculated so that the natural loop frequency fn and damping factor  $\xi$  are suitable for the FM deviation and modulation bandwidth required. Values of 6.2k and 2.2nF are recommended for  $\pm 5$ kHz maximum deviation and 3kHz audio bandwidth when the second IF frequency is 100kHz. These give fn = 20kHz  $\xi$  = 0.707.

#### Squelch Facility

When inputs to the product detector differ in phase a series of current pulses will flow out of pin 7. This feature can be used to adjust the VCO; when a 1mV unmodulated input signal is applied to pin 18 the VCO frequency should be trimmed to maximise the voltage on pin 7.

The squelch level is adjusted by means of a preset variable resistor between pin 7 and Vcc to set the output signal to noise ratio at which it is required to mute the output. The capacitor between pin 7 and ground determines the squelch attack time. A value between 10nF and 10µF can be chosen to give the required characteristics.

#### **Outputs**

High speed data outputs can be taken direct from pins 11 and 12 but normally for audio applications pin 8 is used. A filter network will be needed to restrict the audio bandwidth and an RC network consisting of 4.7k and 4.7nF may be used.

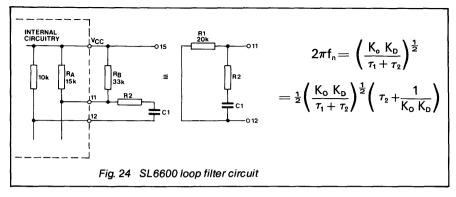

#### LOOP FILTER DESIGN

The design of the loop filter determines the allowable deviation of the received FM, the bandwidth of the modulating audio and the signal-to-noise ratio which may be achieved. With wide-deviation signals the filter may be omitted altogether and the system will work perfectly well, but with a somewhat reduced signal-to-noise ratio which is nevertheless quite acceptable in many applications. The filter (Fig.24) consists of a resistor and capacitor (R2 and C1) in series between pins 11 and 12. The external 30 k $\Omega$  resistor mentioned above produces a composite resistor, R1, of 20 k $\Omega$  formed by the series connection of the two resistors on the chip and the external resistor in parallel with one of them.

The loop constants of the SL6600 are:-

Ko = 2.4fo Radians/Volt second

K<sub>D</sub> = 2.8 Volts/Radian

$R1 = 20k\,\Omega$

$K_0K_D = 6.7$ fo sec<sup>-1</sup>

Other variables used in driving the loop filter are:-

fo The VCO centre frequency

$\Delta f$  The peak deviation

n The natural frequency of the loop

fm The maximum modulation frequency

Øe The maximum phase error in the loop

The damping Factor

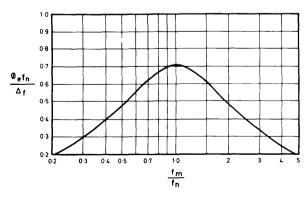

The values of  $f_m$  and  $\Delta f$  are part of the system specification and together with  $f_0$  specify  $\Phi e$ . The VCO centre frequency is generally chosen to be 100kHz or  $10\Delta f$ , whichever is the greater. Maximum frequency is 1MHz. The damping factor,  $\xi$ , is usually chosen to be 0.707. Fig.25 shows the relationship between  $\Phi e$ ,  $f_m$  and  $\Delta f$  for  $\xi = 0.707$ .

Fig. 25 Phase error for damping factor = 0.707

**EXAMPLE**

$$\Delta f = 5kHz$$

;  $f_m = 3kHz$ ,  $f_0 = 100kHz$

Therefore

$$\phi_e$$

max  $=$   $\frac{0.93\Delta f}{f_O}$   $=$   $\frac{0.93\times5\times10^3}{100\times10^3}$   $=$  0.046 radians

The problem now is to deduce the value of fn from Fig. 4; this is an iterative process.

(i) Put

$$f_n = 10$$

kHz. Therefore  $\frac{f_m}{f_n} = \frac{3}{10} = 0.3$

from Fig. 4

$$\phi_e = \frac{0.3 \times 5 \times 10^3}{10 \times 10^3} = 0.15$$

radians (too large)

(ii) Put

$$f_n = 20$$

kHz. Therefore  $\frac{f_m}{f_n} = \frac{3}{20} = 0.15$

from Fig. 4

$$\phi_e = \frac{0.17 \times 5 \times 10^3}{20 \times 10^3} = 0.043$$

radians,

which agrees closely with the required value. Knowing the natural frequency the loop time constants can now be evaluated:-

$$t_1 + t_2 = \frac{K_0 K_D}{(2\pi f_0)^2} = \frac{6.77 \times 10^3}{(2 \times \pi \times 20 \times 10^3)^2} = 42.9 \mu s$$

$$t_2 = \frac{2D}{2\pi f_0} = \frac{0.707}{\pi \times 20 \times 10^3} = 11.2 \mu s$$

$$t_1 = 31.7 \mu s C = \frac{t_1}{R_1} = 1.6 nF$$

$$R_2 = \frac{t_2}{C} = 7k\Omega$$

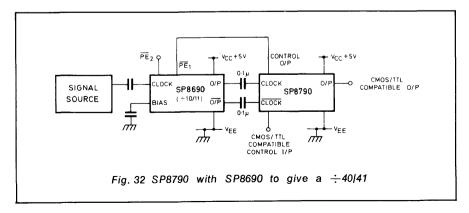

# SL6640 and SL6650

# for single conversion receivers with quadrature detectors

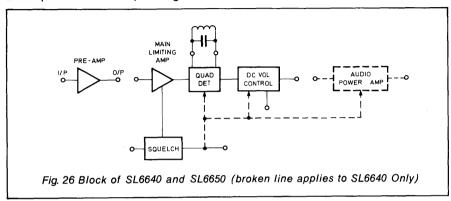

The SL6640 and SL6650 are illustrated in Fig.26. Each consists of an IF limiting preamplifier, a main limiting amplifier, a quadrature detector, a squelch system, and a DC audio gain control. In addition, the SL6640 contains a low-power audio output stage.

The IF preamplifier has a bandwidth of 25 MHz, a gain of about 46 dB (200 times), and an input impedance of 5 k $\Omega$  shunted by 2 pF. It consists of five cascaded long-tailed pairs and has excellent limiting characteristics.

The main IF amplifier also has a bandwidth of 25 MHz but its gain before limiting is about 60 dB (1000) and it consists of six long-tailed pairs. The third and sixth of these stages contain detectors, the outputs of which drive the squelch system. The output of the limiting amplifier feeds a double-balanced modulator and also an external phase-shift circuit which in turn feeds the other port of the double-balanced modulator. This double-balanced modulator thus acts as a quadrature detector. The quadrature detector in the SL6640 and SL6650 has very good performance when demodulating narrow band FM signals, even when working with intermediate frequencies of up to 21.4 MHz. This is because at over 50 k $\Omega$ , the impedance of the quadrature port is high and so the Q of the quadrature circuit is not impaired by being loaded, as is so often the case with integrated circuit quadrature detectors.

The external phase shift circuit is fed via internal capacitors of only 2 pF and so the quadrature circuit works well only at about 4.5MHz and above. The SL6640 and SL6650 cannot, therefore, be used at the common 455kHz IF. The SL6690 (see below) works very well at this frequency, however, and should be used when 455kHz operation is required.

The audio output from the quadrature circuit goes to an audio amplifier which is DC-controlled to allow the use of remote gain control. The output of the SL6650 is taken from this gain control, but the SL6640 has an extra audio amplifier capable of driving a small  $8\Omega$  loudspeaker.

The squelch system is driven by the detectors in the IF strip and contains a comparator which requires an input to set the squelch level. A resistor between

this programming input and the squelch output provides hysteresis to the system. In the SL6650 the squelch system merely provides a DC output to indicate the presence of a signal larger than the squelch threshold but in the SL6640 the squelch controls the power supply to both the detector and the audio stages. The standby power of the SL6640 is thus the lower even though it is the more complex circuit.

The SL6640 is manufactured in an 18 lead DIL package and the SL6650 in a 16 lead DIL. The devices are designed so that as many as possible of their pins are common i.e., pins 1 to 6 are identical and pins 13 to 18 of the SL6640 are equivalent to pins 11 to 16 of the SL6650 and only the pins around the audio stages differ. This allows similar board layout to be used in radios using the SL6640 or the SL6650. In the pin-by-pin description which follows, pin numbers are given for the SL6640, those of the SL6650, where they differ, are given in brackets e.g., pin 18 (16).

Pin 1 is the bias point for the main IF amplifier. It must be decoupled effectively by an RF capacitor to ground and connected by a coil or resistor to the IF input, pin 14 (12). If a resistor is used, it should provide the correct match for the interstage filter; if a coil is used it will probably be part of the filter and must not have any DC connection to ground. The decoupling capacitor must be at least  $0.01~\mu\text{F}$ .

Pin 2 is the squelch programming point and pin 3 the squelch output pin. The squelch level is set by a 470 k $\Omega$  variable resistor (which should be increased to 1 M $\Omega$  if supplies of over 6V are used) in series with a 47 k $\Omega$  resistor between pin 2 and ground. Squelch sensitivity increases with the value of the variable resistor. Pin 3 is at a high potential when no signal is present and drops to near ground potential when a signal is detected. The output current from pin 3 is less than 2 mA but it may, of course, be buffered if necessary.

The decoupling capacitor of 0.33 µF on pin 3 prevents brief breaks in signal (such as mobile flutter) from squelching the circuit. Hysteresis in the squelch is obtained by a resistor connected between pins 2 and 3. The amount of

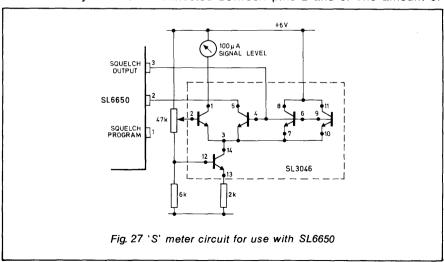

hysteresis depends on the squelch threshold, the resistor value and the supply voltage. At 6V supply a 390 k $\Omega$  resistor gives 3 to 4 dB hysteresis at 10 μV squelch level and about 10 dB at 100 μV squelch level. Larger resistors are necessary at higher supply voltages and the minimum possible hysteresis rises to about 7 dB with a 1.5  $M\Omega$  resistor and a 9 V supply. Despite its variation with supply voltage, the squelch is quite stable with temperature and alters by only 1 to 2 dB as the circuit is temperature cycled. If squelch is not required the SL6650 squelch pins may be used, with an SL3046 transistor array, to drive an S meter as shown in Fig.27. The system consists of a negative feedback amplifier and is not possible with an SL6640, where the internal squelch must always be used.

The quadrature circuit is connected between pins 4 and 5. This can consist of an LC tuned circuit resonant at the centre of the IF passband, or one of the commercial crystal quadrature circuits for NBFM, or even a ceramic interstage filter such as is made for broadcast receiver applications. Ceramic filters usually need to be tuned by a parallel trimmer capacitor and their efficiency as quadrature elements can vary widely from batch to batch. They are not, therefore, the best quadrature elements to choose although they are nonmicrophonic and smaller than most coils. The resistive element of the impedance between pins 4 and 5 is over 50  $k\Omega$  and so has little effect on the Q of a wound quadrature element. Narrow FM can thus be demodulated, even with an LC quadrature element, with an excellent signal-to-noise ratio - 50 dB or better. If a lower Q is required the resistance between the pins may be reduced by the use of an external resistor.

No DC path must exist between pins 4 and 5 and any other point, but they themselves may be connected together if required. It is better to have a DC path between them than not, so long as it is not at the expense of the Q of the

quadrature element.

The DC volume control consists of a fixed resistor of 47 k $\Omega$  in series with a variable resistor of 470  $k\Omega$  connected between pin 6 and ground. The gain range is typically 70 dB (3000:1) and gain is minimum when resistance is minimum.

Pins 12 and 13 of the SL6640 and pin 11 of the SL6650 are the supply pins. SL6640 pin 12 is the audio output stage supply while pin 13 supplies the remainder of the circuit. In the case of the SL6650 pin 11 is the supply connection for the entire circuit. The supply voltage is normally  $\,+6V$  but the circuits will work with supplies between +5V and +9V. Consumption of the SL6640 at 6V is 3.5mA (squelched) and 10mA (unsquelched), or more if audio power is being supplied, while the SL6650 draws 6mA in either case. Pin 12 of an SL6640 may be left unconnected if for any reason the audio stage is not required but it must not be used with more than 0.5V difference in potential between pins 12 and 13.

The power supplies must be well decoupled at RF with at least 0.1µF having low inductance and short leads. The supplies should also have low audio ripple and it is necessary to decouple the SL6640 supply very thoroughly at LF if the audio stage is to operate at its highest powers and retain its AM

rejection.

Pin 14 (12) is the input of the main IF amplifier and should be biased by being connected to pin 1 as described above. The input impedance is 5  $k\dot\Omega$ shunted by 2 pF.

Pins 15 (13) and 17 (15) are decoupling points within the circuit and should be decoupled to earth by good RF capacitors, preferably 0.1  $\mu$ F and at least 0.01  $\mu$ F. Inadequate decoupling of these pins causes poor AM rejection and can cause instability.

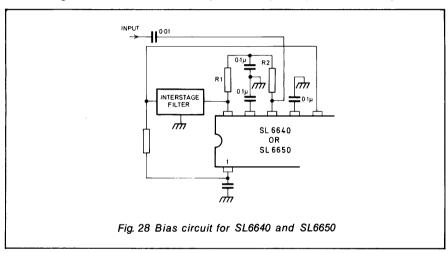

Bias circuitry for both the main amplifier and the preamplifier is shown in Fig.28. The preamplifier input is pin 16 (14). It is not self biased but is fed with bias from pin 18 (16) via a total of about 15 k $\Omega$ . The input impedance of the preamplifier is 5 k $\Omega$  shunted by 2 pF. If, as is common, the preamplifier is fed from a filter requiring a precise match, the value of resistor R2 should be chosen to provide this. The source impedance driving the preamplifier should be 750  $\Omega$  or less to prevent instability. The input signal should be fed to pin 16 (14) via a capacitor or other DC block. The sum of resistors R1 and R2 should be 15 k $\Omega$  and their junction well decoupled at HF. The noise figure of the preamplifier is 7 dB when driven by 350  $\Omega$ .

The preamplifier output is pin 18 (16) and it has an output impedance of 300  $\Omega$ . Signal is taken from the output of the preamplifier to the input of the

main amplifier via an interstage filter. This is a roofing filter to provide some limitation of noise bandwidth, not the primary selectivity of the receiver which must be provided by a high performance filter placed before the preamplifier. This filter, therefore, need have neither a good shape factor nor large stopband attenuation. Any simple filter is suitable but at 10.7 MHz, cheap ceramic filters are particularly useful since they are small and require no setting-up. Much work with the SL6640 and SL6650 has used Murata SFE 10.7 MA filters since they match the output impedance of the preamplifier.

The final part of this section deals with those pins whose functions differ between the SL6640 and the SL6650. First the SL6640. Pin 7 is the output of the DC controlled audio preamplifier and is an emitter follower with a low current tail. It will only drive high impedance loads and needs an HF rolloff

capacitor to earth of  $\frac{0.01 \ \mu F}{f}$  where f is the desired rolloff frequency in kHz.

In normal use pin 7 is connected to pin 8, the input to the output stage, by a 0.1  $\mu$ F capacitor. Pin 8 is biased by connecting it to the centre of two 220 k $\Omega$  resistors connected between the positive supply and ground} in series.

Pin 9 of the SL6640 is the inverting input to the output stage and is used to provide negative feedback to define both DC operating point and stage gain. The feedback resistor from the output pin 11 is 120 k $\Omega$  and the gain-defining resistor (which is connected from pin 9 to ground via an isolating capacitor of 1  $\mu F)$  can be any value greater than 1.2 k $\Omega$ . The gain is equal to the ratio of these two resistors, and hence when the smaller is 1.2 k $\Omega$  the gain is 40 dB (100). Attempts to achieve higher gain leads to instability and, more important, excessive distortion since the open loop gain of the output stage is only some 55 dB.

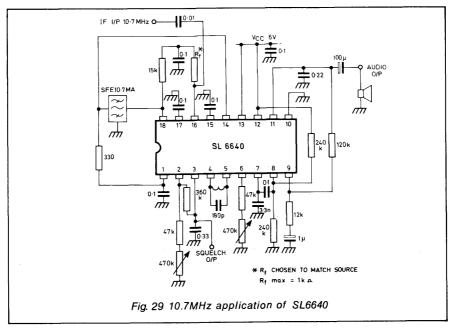

Pin 10 is earth and pin 11 is the audio power output. Pin 11 is decoupled to earth with 0.22  $\mu F$  to ensure HF stability and drives its load via a 100  $\mu F$  capacitor. With care, and a 9V supply, the SL6640 will drive an  $8\Omega$  loudspeaker at 250mW but a more practical figure is around 175mW. A complete circuit diagram of an SL6640 in use is shown in Fig.29.

Pins 7 and 9 of the SL6650 are unused. Pin 8 of the SL6650 is earth and pin 10 is the audio output. This output appears on the open collector of a transistor and so must be connected to the positive supply by a resistor – generally  $10k\Omega$ . Audio is taken through a capacitor and the pin is also decoupled at HF.

by a capacitor of  $\frac{0.015~\mu F}{f}$  where f is the cutoff frequency in kHz.

# SL6690

### ultra-low power consumption quadrature detector system

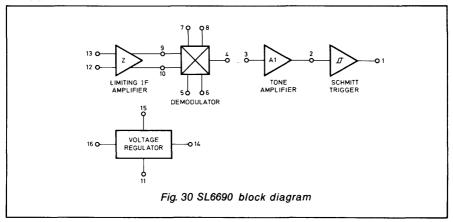

The SL6690 block diagram is shown in Fig. 30. The circuit consists of a limiting IF amplifier which drives a quadrature detector, an LF amplifier and Schmitt trigger (which can be used either as a signal-to-noise squelch system or as a squarer when the circuit is used in a pager), and a voltage regulator which uses an external PNP transistor.

The IF amplifier has a bandwidth of 1.5 MHz, making the circuit particularly useful at the popular communications and paging IF of 455 KHz. Its input impedance is 20 k $\Omega$  shunted by 2 pF and its output impedance is about 2 k $\Omega$ . Bias is obtained by DC feedback from the outputs to the inputs.

The quadrature detector is a conventional double-balanced modulator using transistor tree techniques. The quadrature circuit is an external LC tuned circuit and the capacitors driving the quadrature circuit are also external, which allows the detector to be used down to VLF as well as up to about 1.5 MHz.

The LF amplifier has a gain of 54 dB and is biased by a DC connection from its output to its input. It is an inverting amplifier so its gain and frequency characteristics may be defined by negative feedback. The Schmitt trigger is driven directly by the LF amplifier. Its output is a free collector which may be connected to either  $V_{CC}$  (the regulated supply) or the unregulated supply rail. In its ON state it will sink up to 150  $\mu$ A.

The regulator, which requires an external series PNP transistor, allows the SL6690 to work from supplies between +2.5 and +6V. The external transistor is necessary because monolithic PNP transistors have poor  $h_{\rm fe}$  at very low current levels.

Pin 1 is the Schmitt trigger output, a free collector which can sink up to  $150\,\mu\text{A}$  when the transistor is turned on and can rise to either  $V_{CC}$  or some other positive rail up to +6V when turned off. The input to the Schmitt trigger and the output of the LF amplifier are connected internally and the node brought out to pin 2. Bias must be taken from this pin to the LF amplifier input, pin 3.

via a resistance of 50 k $\Omega$  or less. The LF amplifier inverts and its gain and passband may be defined by negative feedback. An output may be taken from pin 2 and the Schmitt trigger left unused in which case no connection need be made to pin 1. The bias of the amplifier/Schmitt combination is sufficiently accurate to give the Schmitt an output mark-space ratio of between 0.9:1 and 1.1:1 with a sine wave input to the amplifier. The LF amplifier input impedance is 50 k $\Omega$  and its open loop gain roughly 54 dB.

No DC connections should be made from pin 3 except the bias connection to pin 2; all inputs should be coupled via capacitors. To prevent HF instability 2.2 k $\Omega$  in series with 120 pF should be connected from pin 2 to ground.

The output of the quadrature detector is pin 4 and its output impedance is 1 k $\Omega$ . The detector will give an output of 10 mV/Degree phase change and distortion of about 3 per cent (more if a ceramic resonator is used as a quadrature element). A single filter capacitor removes RF from the detected output.

The quadrature circuit is connected between pins 5 and 6 and may be a parallel tuned LC circuit or a ceramic resonator. The port has an input impedance of 50 k $\Omega$  shunted by 2 pF. The quadrature circuit may or may not present a DC path between the two pins. Use of ceramic quadrature elements usually results in greater distortion than the use of LC elements but such ceramic elements occupy less space and do not require adjustment. The quadrature circuit is driven by the output from pins 7 and 8 via two capacitors. Pin 7 drives pin 5 and pin 8 drives pin 6. The value of the capacitors depends on the frequency of operation and the quadrature circuit used.

Pins 9 and 10 are the outputs of the IF amplifier and are used to provide bias to its inputs. A 100 k $\Omega$  resistor is connected from pin 10 to pin 12 and pin 12 is grounded at AC by a capacitor. Pin 9 is connected to pin 13, the signal input pin, by another 100 k $\Omega$  resistor in series with a resistor of the correct value to terminate the IF source. The junction of the two resistors is decoupled at RF by a low inductance capacitor. The IF input is applied to pin 13 from the IF filter, via a coupling capacitor if necessary to isolate pin 13 at DC.

Pin 11 is earth and pins 14, 15, and 16 the supply/regulator pins. The supply, which may be between 2.5V and 6V is applied to pin 16 and to the emitter of a high gain PNP transistor whose base is connected to pin 15 and collector to pin 14. Pin 14 is stabilised at 2V and must be thoroughly decoupled at RF by a  $0.1\mu F$  capacitor. The SL6690 may be turned on in 12 milliseconds or less so the power supply may be strobed in paging applications so that the mean power dissipation in the circuit is an order of magnitude lower than its normal 2mW (1mA @ 2V).

# FM RECEIVERS USING SL6000 SERIES

The SL6600, SL6640, SL6650 and SL6690 are intended for use in NBFM receivers – mobile, hand-portable, base station and paging. They are all intended for use as IF Amplifier/Detector/Squelch modules and, of course, the SL6640 has a low power audio output stage.

The circuits, having low power consumption and, indeed, limiting amplifiers, have low resistance to intermodulation (although they have excellent dynamic range) and must be used after the main selectivity of the receiver. Modern receiver design emphasises strong signal performance even at the expense of sensitivity and hence front ends having much gain are not popular. This can

leave an uncomfortable gap between the 2 to 4  $\mu$ V output from a receiver filter and the 10  $\mu$ V or so that these circuits require to give an adequate signal-tonoise ratio. Redesign of the front end to give slightly more gain is possible and certainly the easiest solution but it may produce an unacceptable reduction in intermodulation performance. An amplifier is therefore needed between the filter and the SL6600/40/50/90.

This amplifier can be a convenience (some filters have matching impedances so high that even the input impedances of these circuits are embarassingly low) but, preceeding as it does a very high gain integrated circuit, it can suffer from stubborn instability. It also increases the power consumption of the receiver which is annoying in a hand-portable, although a hand-portable with its limited antenna is most likely to be able to tolerate a higher gain front end and hence least likely to need an extra stage of IF gain.

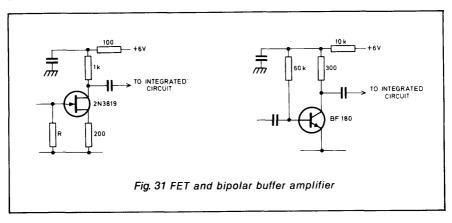

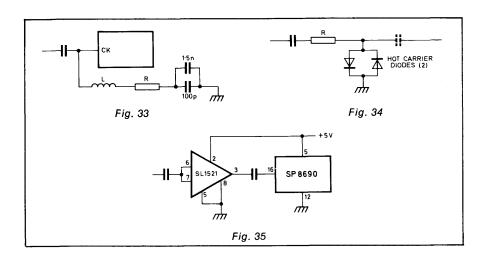

Suitable amplifiers may be made with a single transistor or FET and two circuits are shown in Fig.31. The FET circuit uses more current and an FET with a good performance at 1 mA and a low pinch-off voltage is required. The transistor circuit is far less demanding but has a lower input impedance (which depends on  $h_{\rm fe}$  and  $C_{\rm ob}$  and will vary from device to device). These amplifiers must be very well isolated if the receiver is to be stable and the powerful decoupling of the transistor circuit is a point in its favour.

Apart from the occasional necessity for a low-gain preamplifier these circuits present few problems and are very easy to use. As mentioned above, some attention must be paid to layout to isolate input and output, particularly at the same frequency, as much as possible. Other points to be remembered are the use of non-inductive capacitors (many capacitors are inductive at frequencies as low as 5 MHz) and adequate decoupling of all bias points and power supplies – in connection with this it is worth remembering that it is useless to use a good RF capacitor with short leads if the printed connection to it is long and narrow.

It is not intended to describe in detail the design of any complete receivers using these circuits. However, a review of the various types of receiver where these circuits may be used and the considerations affecting such use is given below.

### LAND MOBILE RADIOS

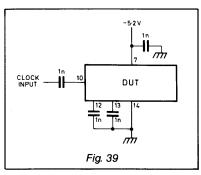

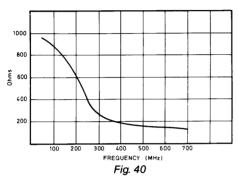

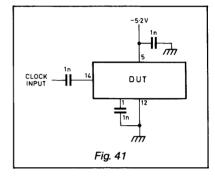

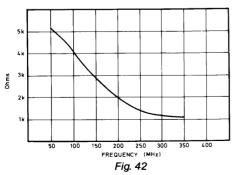

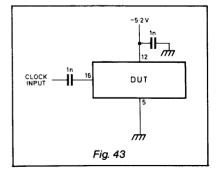

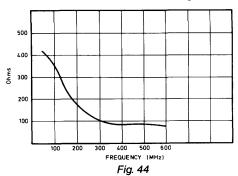

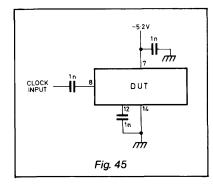

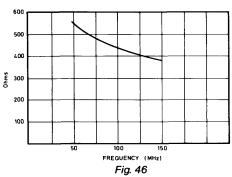

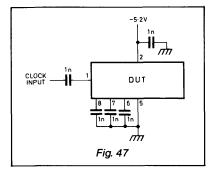

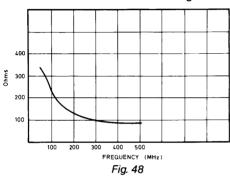

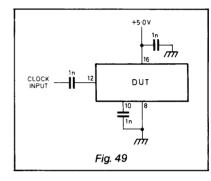

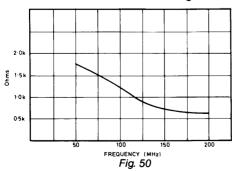

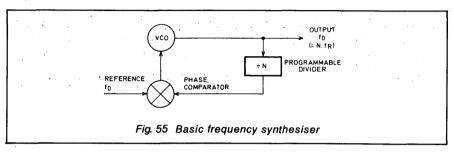

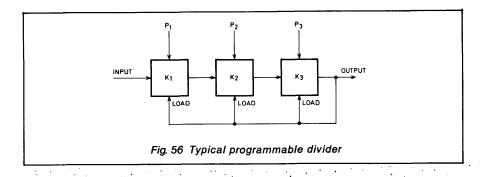

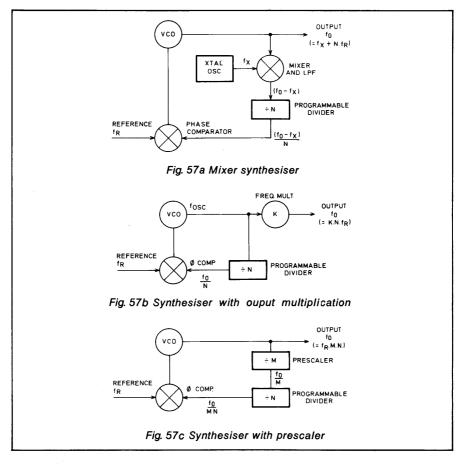

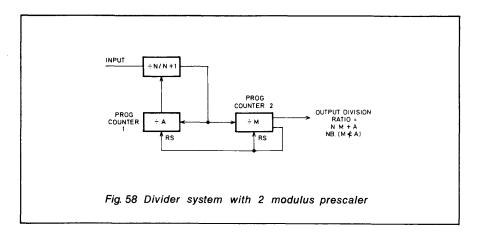

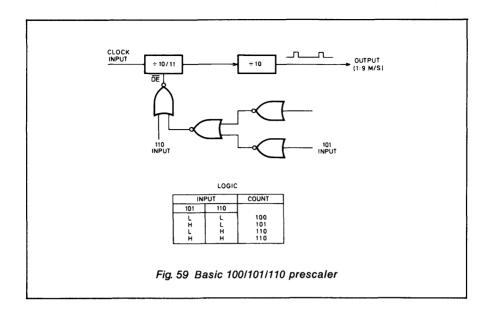

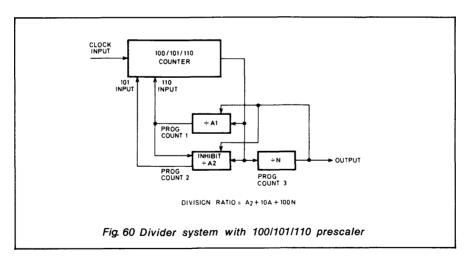

In the VHF or UHF bands land mobiles use narrow deviation FM (between 1.5 and 12kHz $\Delta$ f) and generally use a first IF of 10.7 or 21.4MHz. Transceivers can be hand-held or vehicle mounted. For hand-held transceivers the choice is between the SL6600 which has low power consumption and can be strobed and the SL6640 which has an integral output stage. The signal-to-noise ratio of either circuit is adequate when used with the recommended circuitry but there is a performance difference. The capture effect of a PLL detector is much better than that of a quadrature detector: a receiver using an SL6600 will capture the stronger of two co-channel signals even if it is only stronger by 2 to 4dB. The SL6640 will be affected by a co-channel interfering signal until it is 20dB or more below the wanted signal. Both features can be valuable; some (including military) users need to know of other signals on-channel while others, particularly in areas where channels are shared with space diversity, prefer systems which ignore low-level co-channel interference.